EDA实验报告Word格式文档下载.docx

《EDA实验报告Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《EDA实验报告Word格式文档下载.docx(23页珍藏版)》请在冰豆网上搜索。

另外,我们选择Verilog作为默认的硬件描述语言。

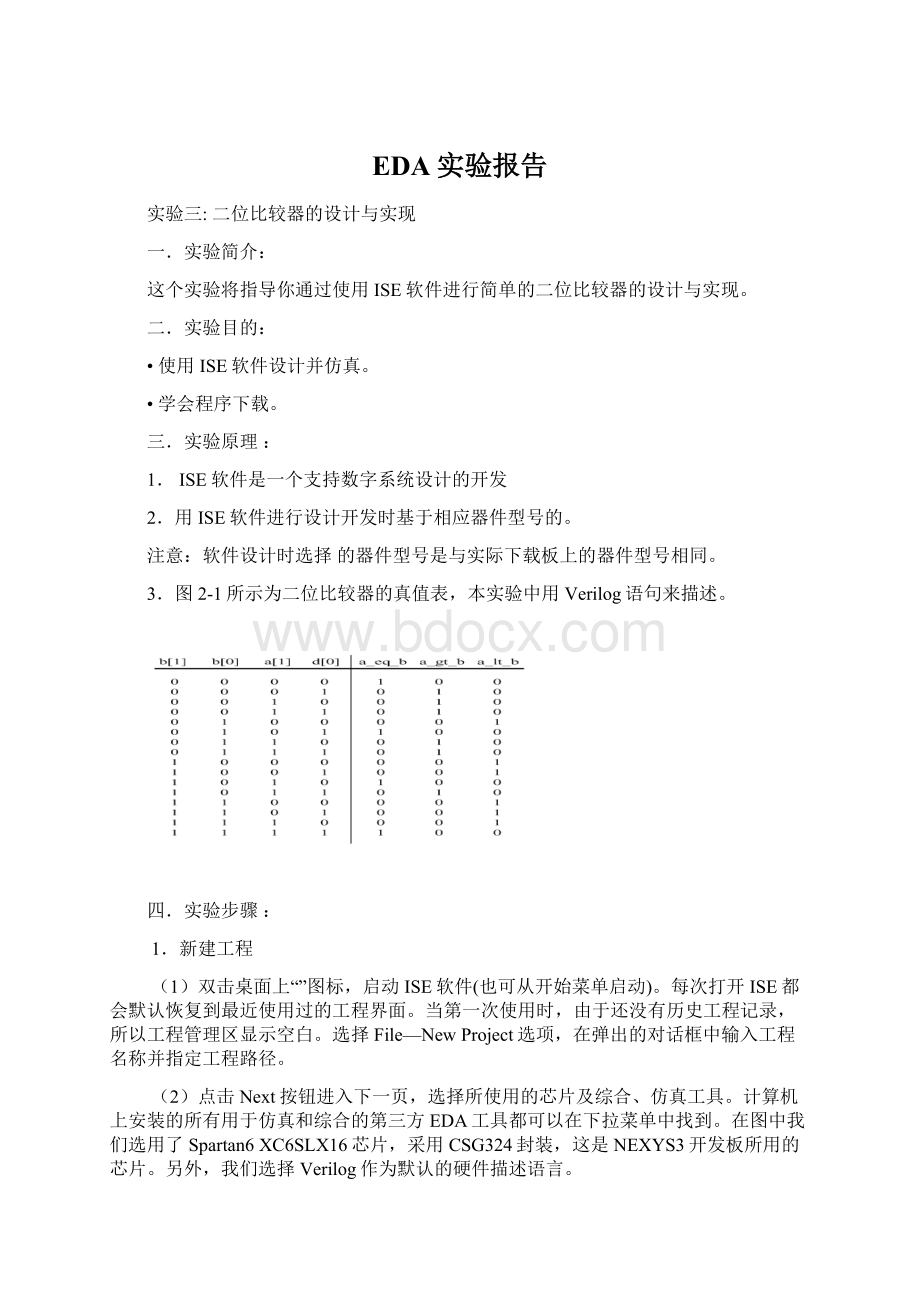

(3)再点击Next按钮进入下一页,这里显示了新建工程的信息,确认无误后,点击Finish就可以建立一个完整的工程了。

(1)在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择NewSource命令,选择VerilogModule输入,并输入Verilog文件名。

(2)单击Next按钮进入端口定义对话框。

其中ModuleName栏用于输入模块名,这里是comp2bit,下面的列表框用于端口的定义。

PortName表示端口名称,Direction表示端口方向(可选择为input、output或inout),MSB表示信号最高位,LSB表示信号最低位,对于单信号的MSB和LSB不用填写。

当然,端口定义这一步我们也可以略过,在源程序中再行添加。

(3)定义了模块的端口后,单击Next进入下一步,点击Finish完成创建。

这样,ISE就会自动创建一个Verilog模块的模板,并且在源代码编辑区打开。

简单的注释、模块和端口定义已经自动生成,接下来的工作就是将代码编写完整。

(4)输入代码后,我们还需要对模块进行测试。

在工程管理区将view设置为Simulation,在任意位置单击鼠标右键,并在弹出的菜单中选择NewSource,在类型中选择VerilogTestFixture,输入测试文件名,单击下一步。

这时所有工程中的模块名都会显示出来,我们选择要进行测试的模块。

点击Next,再单击Finish按钮,ISE会在源代码编辑区自动生成测试模块的代码。

我们看到,ISE已经自动生成了基本的信号并对被测模块做了例化。

我们的工作就是在initial…end块中的“//Addstimulushere”后面添加测试向量。

(5)完成测试文件编辑后,确认工程管理区中view选项设置为Simulation,这时在过程管理区会显示与仿真有关的进程。

右键单击其中的SimulateBehavioralModel项,选择弹出菜单中的ProcessProperties项,会弹出属性设置对话框,其中SimulationRunTime就是仿真时间的设置,可将其修改为任意时长。

(6)仿真参数设置完后,就可以进行仿真。

首先在工程管理区选中测试代码,然后在过程管理区双击SimulateBehavioralModel,ISE将启动ISESimulator,可以得到仿真结果。

3.综合与实现

(1)在工程管理区的view中选择Implementation,然后在过程管理区双击Synthesize-XST,就可以开始综合过程。

(2)另外,要实现设计,还需要为模块中的输入输出信号添加管脚约束,这就需要在工程中添加UCF文件。

在工程管理区单击鼠标右键,点击NewSource,选择Implementation-ConstraintsFile,出现一个空白的约束文件,我们就可以为设计添加各种约束。

如果综合步骤没有语法错误,XST能够给出初步的资源消耗情况,点击DesignSummary,即可查看。

(3)在过程管理区双击ImplementationDesign选项,就可以自动完成实现步骤。

如果设计没有经过综合,就会启动XST完成综合,在综合后完成实现过程。

经过实现后能够得到精确的资源占用情况。

在DesignSummary即可看到具体的资源占用情况。

4.二位比较器的verilog源代码

modulecomp2bit(

inputwire[1:

0]a,

0]b,

outputwirea_eq_b,

outputwirea_gt_b,

outputwirea_lt_b

);

assigna_eq_b=~b[1]&

~b[0]&

~a[1]&

~a[0]

|~b[1]&

b[0]&

a[0]

|b[1]&

a[1]&

a[0];

assigna_gt_b=~b[1]&

a[1]

|~b[0]&

assigna_lt_b=b[1]&

~a[1]

|b[0]&

~a[0];

endmodule

五.实验结果:

通过对二位比较器的设计与实现仿真模拟出的结果,如图所示:

实验一:

输入逻辑门的设计与实现

一.实验简介:

这个实验将指导你通过使用ISE软件进行简单的2输入逻辑门的设计与实现。

二.实验目的:

•使用ISE软件设计并仿真。

•学会程序下载。

三.实验内容:

1.ISE软件是一个支持数字系统设计的开发平台

2.用ISE软件进行设计开发时基于相应器件型号的。

3.图1-1所示电路包含6个不同的逻辑门,本实验中用Verilog语句来描述。

四.实验步骤:

1.新建工程

(1)双击桌面上“”图标,启动ISE软件(也可从开始菜单启动)。

选择File——>

NewProject选项,在弹出的对话框中输入工程名称并指定工程路径,如图所示。

(2)点击Next按钮进入下一页,选择所使用的芯片及综合、仿真工具。

计算机上安装的所有用于仿真和综合的第三方EDA工具都可以在下拉菜单中找到,如图所示。

(3)再点击Next按钮进入下一页,这里显示了新建工程的信息,确认无误后,点击Finish就可以建立一个完整的工程了,如图所示。

2设计输入和代码仿真

(1)在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择NewSource命令,会弹出如图1-5所示的新建源代码对话框,对于逻辑设计,最常用的输入方式就是HDL代码输入法(VerilogModule、VHDLModule)、状态机输入法(StateDiagram)和原理图输入法(Schematic)。

这里我们选择VerilogModule输入,并输入Verilog文件名。

(2)单击Next按钮进入端口定义对话框,如图1-6所示。

其中ModuleName栏用于输入模块名,这里是gates2,下面的列表框用于端口的定义。

简单的注释、模块和端口定义已经自动生成,接下来的工作就是将代码编写完整,如图1-7所示。

(4)输入代码后,我们还需要对模块进行测试。

这时所有工程中的模块名都会显示出来,我们选择要进行测试的模块,如gates2模块。

点击Next,再单击Finish按钮,ISE会在源代码编辑区自动生成测试模块的代码,如图1-8所示。

对gates2模块,我们可以添加如下所示的测试代码。

#200

a<

=0;

b<

#200

a<

=1;

#200

(5)完成测试文件编辑后,确认工程管理区中view选项设置为Simulation,这时在过程管理区会显示与仿真有关的进程,如图1-9中Processes栏所示。

右键单击其中的SimulateBehavioralModel项,选择弹出菜单中的ProcessProperties项,会弹出如图所示的属性设置对话框,其中SimulationRunTime就是仿真时间的设置,可将其修改为任意时长。

(1)所谓综合,就是将HDL语言、原理图等设计输入翻译成由与、或、非门和RAM、触发器等基本逻辑单元的逻辑连接(网表),并根据目标和要求(约束条件)优化所生成的逻辑连接。

完成了输入和仿真后就可以进行综合。

在工程管理区的view中选择Implementation,然后在过程管理区双击Synthesize-XST,就可以开始综合过程,如图所示

综合可能有3种结果:

如果综合后完全正确,则在Synthesize-XST前面有一个打勾的小圆圈;

如果有警告,则出现一个带感叹号的黄色小圆圈;

如果有错误,则出现一个带叉的红色小圆圈。

如果综合步骤没有语法错误,XST能够给出初步的资源消耗情况,点击DesignSummary,即可得到结果。

(3)综合完成后,下一个步骤就是实现(Implementation)。

所谓实现,是指将综合输出的逻辑网表翻译成所选器件的底层模块和硬件原语,将设计映射到器件结构上,进行布局布线,达到在选定器件上实现设计的目的。

实现主要分为3个步骤:

翻译(Translate)逻辑网表、映射(Map)到器件单元与布局布线(place&

Route)。

在ISE中,执行实现过程,会自动执行翻译、映射和布局布线过程:

也可单独执行。

在过程管理区双击ImplementationDesign选项,就可以自动完成实现的3个步骤,如图1-14所示。

4.输入逻辑门的verilog源代码

modulegates2(

inputwirea,

inputwireb,

outputwire[5:

0]z

assignz[5]=a&

b;

assignz[4]=~(a&

b);

assignz[3]=a|b;

assignz[2]=~(a|b);

assignz[1]=a^b;

assignz[0]=a~^b;

通过对输入逻辑门的设计与实现仿真模拟出的结果,如图所示:

实验四:

4位二进制-BCD码转换器的设计与实现

一、实验简介

这个实验将指导你通过使用ISE软件进行4位二进制-BCD码转换器的设计与实现。

二、实验目的

使用ISE软件设计并仿真。

学会程序下载。

三、实验内容

1.ISE软件是一个支持数字系统设计的开发平台

2.用ISE软件进行设计开发时基于相应器件型号的。

注意:

3.图8-1所示为4位二进制-BCD码转换器的真值表,本实验中用Verilog语句来描述。

四、实验步骤

1.新建工程

双击桌面上“”图标,启动ISE软件(也可从开始菜单启动)。

选择FileNewProject选项,在弹出的对话框中输入工程名称并指定工程路径。

点击Next按钮进入下一页,选择所使用的芯片及综合、仿真工具。

再点击Next按钮进入下一页,这里显示了新建工程的信息,确认无误后,点击Finish就可以建立一个完整的工程了。

2.设计输入和代码仿真

在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择NewSource命令,选择VerilogModule输入,并输入Verilog文件名。

单击Next按钮进入端口定义对话框。

其中ModuleName栏用于输入模块名,这里是binbcd4,下面的列表框用于端口的定义。

定义了模块的端口后,单击Next进入下一步,点击Finish完成创建。

输入代码后,我们还需要对模块进行测试。

完成测试文件编辑后,确认工程管理区中view选项设置为Simulation,这时在过程管理区会显示与仿真有关的进程。

仿真参数设置完后,就可以进行仿真。

3.综合与实现

在工程管理区的view中选择Implementation,然后在过程管理区双击Synthesize-XST,就可以开始综合过程。

另外,要实现设计,还需要为模块中的输入输出信号添加管脚约束,这就需要在工程中添加UCF文件。

在过程管理区双击ImplementationDesign选项,就可以自动完成实现步骤。

4.器件配置

硬件配置是FPGA开发最关键的一步,只有将HDL代码下载到FPGA芯片中,才能进行调试并最终实现相应的功能。

首先我们必须生成能下载到硬件中的二进制比特文件。

双击过程管理区的GenerateProgrammingFile,ISE就会为设计生成相应的二进制比特文件。

然后利用USB-MiniUSB缆线,来为开发板提供电源和数据下载。

我们只需上网下载免费的DigilentAdept软件,即可快速实现Nexys3开发板上FPGA的配置。

用USB-MiniUSB缆线连接开发板和PC,打开开发板的电源开关,然后启动DigilentAdept软件。

系统开始自动连接FPGA设备,成功检测到设备后,会显示出JTAG链上所用芯片。

界面上将显示检测到NEXYS3开发板上的器件FPGA(XC6SLX16)。

这里我们对FPGA进行配置。

在Browse中找到之前生成的设计的二进制比特文件,并点击旁边的Program按钮,软件就开始对FPGA进行配置。

配置成功后,下面的状态栏会显示ProgrammingSuccessful。

至此,器件配置成功,我们就可以在器件上验证预期的设计有没有很好的得以实现。

1.4位二进制-BCD码转换器的verilog源代码

modulebinbcd4(

inputwire[3:

outputwire[4:

0]p

assignp[4]=b[3]&

b[2]|b[3]&

b[1];

assignp[3]=b[3]&

~b[2]&

~b[1];

assignp[2]=~b[3]&

b[2]|b[2]&

assignp[1]=b[3]&

b[2]&

~b[1]|~b[3]&

assignp[0]=b[0];

2.4位二进制-BCD码转换器的约束文件

NET"

b[3]"

LOC="

T5"

;

NET"

b[2]"

V8"

b[1]"

U8"

b[0]"

N8"

p[4]"

T11"

p[3]"

R11"

p[2]"

N11"

p[1]"

M11"

p[0]"

V15"

五、实验结果

实验五:

8-3优先编码器的设计与实现

这个实验将指导你通过使用ISE软件进行8-3优先编码器的设计与实现。

三、实验内容

2.用ISE软件进行设计开发时基于相应器件型号的。

3.图7-1所示为8-3优先编码器的真值表,本实验中用Verilog语句来描述。

1.新建工程

双击桌面上“”图标,启动ISE软件(也可从开始菜单启动)。

2.设计输入和代码仿真

在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择NewSource命令,选择VerilogModule输入,并输入Verilog文件名。

其中ModuleName栏用于输入模块名,这里是pencode83,下面的列表框用于端口的定义。

定义了模块的端口后,单击Next进入下一步,点击Finish完成创建。

完成测试文件编辑后,确认工程管理区中view选项设置为Simulation,这时在过程管理区会显示与仿真有关的进程。

仿真参数设置完后,就可以进行仿真。

首先在工程管理区选中测试代码,然后在过程管