FPGA设计实验指导书Word文件下载.docx

《FPGA设计实验指导书Word文件下载.docx》由会员分享,可在线阅读,更多相关《FPGA设计实验指导书Word文件下载.docx(26页珍藏版)》请在冰豆网上搜索。

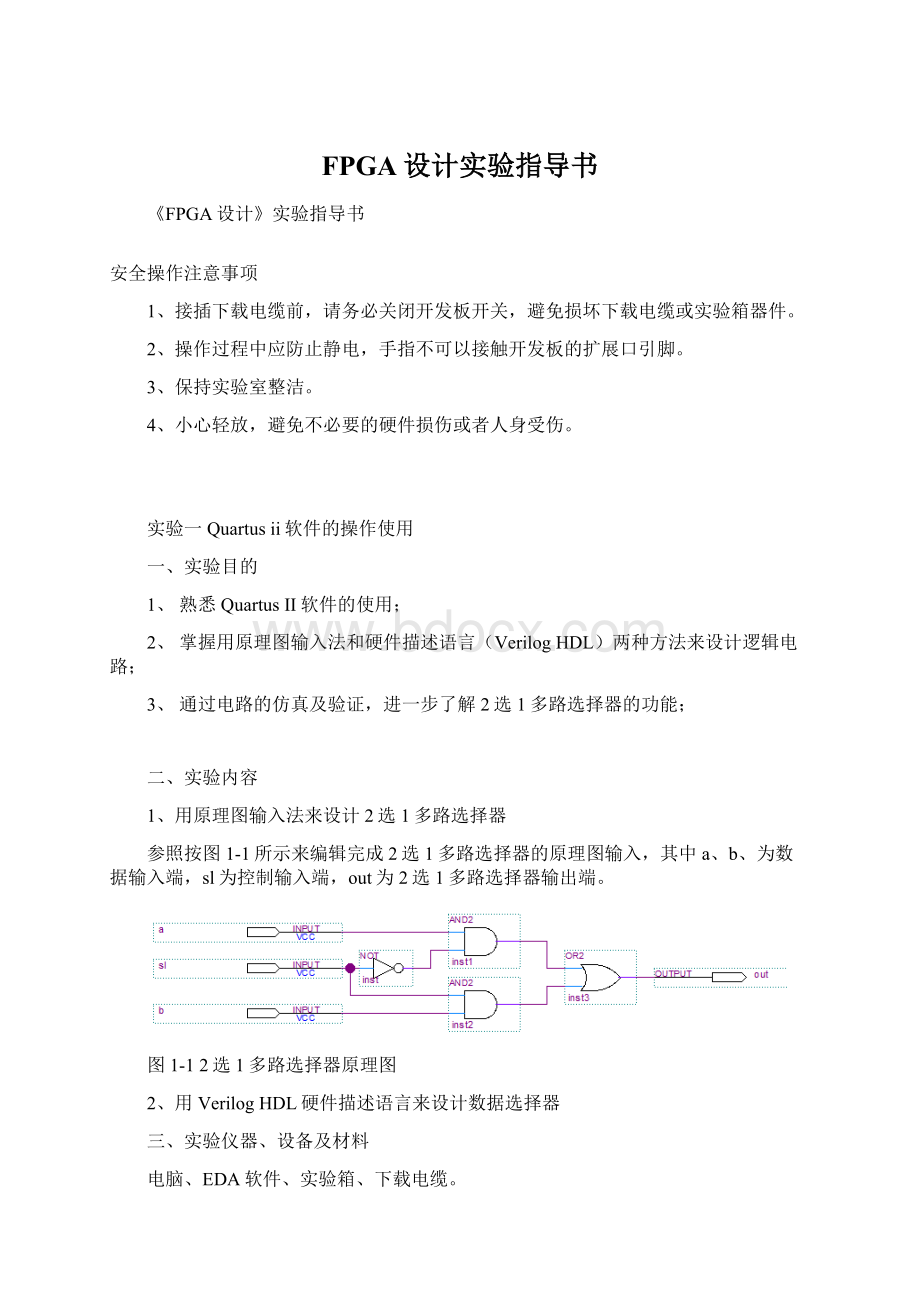

7、观察实验结果是否与仿真结果相吻合。

(二)用VerilogHDL语言完成的设计步骤:

与

(一)大体类似,只是在其第步时选择veriloghdlfile,点击OK后,键入下列代码:

modulemux21a(out,a,b,sl);

outputout;

inputa,b,sl;

regout;

always@(a,b,sl)

case(sl)

0:

out=a;

1:

out=b;

default:

out=1'

bz;

endcase

endmodule

七、实验报告要求

写出用VerilogHDL设计mux21a的主要过程。

八、实验注意事项

用原理图输入法和VerilogHDL语言两种方法所做的设计,一定要建两个不同的工程,并放在不同的目录中,且目录路径中千万不要出现中文字符。

实验二组合逻辑电路设计

一、实验目的

1、学习VerilogHDL基本语法;

2、巩固QuartusII环境下的VerilogHDL编程设计的基础

二、主要仪器设备

EDA实验系统1台

PC机

三、实验内容

1、设计一个四线至二线编码器,其真值表如下:

表2.1四线至二线编码器的真值表

1、设计一个2位信号的比较器,该比较器的电路符号如图2.1所示。

图2.1比较器电路符号

引脚说明:

A、B皆为二位信号;

CLK为时钟脉冲输入;

RST为清除控制信号。

AGTB:

当A>

B时,其值为1,否则为0;

AEQB:

当A=B时,其值为1,否则为0;

ALTB:

当A<

3、设计一个四位全加器。

四、实验报告

根据以上实验内容写出实验报告,包括程序设计,软件编译,管脚分配,硬件测试结果等内容。

实验三时序逻辑电路设计

理解触发器概念,掌握时序器件的VerilogHDL语言程序设计的方法

设计以下内容:

1、基本的D触发器;

2、同步复位的D触发器;

3、异步复位的D触发器;

4、同步置位/复位的D触发器;

根据以上实验内容写出实验报告,包括程序设计,管脚分配;

并提交其仿真结果及分析。

实验四一般计数器的设计及数码管显示

1、学习计数器的设计、仿真和硬件测试;

2、掌握原理图与文本混合设计方法;

3、学习硬件扫描显示电路的设计方法。

EDA/SOPC实验系统1台

三、实验原理

1、设计1个模为24的8421BCD码加法计数器。

2、设计24分频时序电路。

3、将分频或计数结果在数码管上显示。

五、实验报告要求

根据以上实验内容写出实验报告,包括仿真结果及分析、硬件实现、硬件测试等内容。

实验五正弦信号发生器的设计

熟悉基于DDS的正弦信号发生器的基本工作原理

EDA/SOPC实验系统1台,示波器1台

如图5-1所示为基本DDS结构,由相位累加器、相位调制器、正弦ROM查找表、D/A构成。

相位累加器是整个DDS的核心,完成相位累加运算。

相位累加器的输入是相位增量

,又由于

与输出频率

呈线性关系:

,因此相位累加器的输入又可称为频率字输入。

相位调制器接收相位累加器的相位输出,加上一个相位偏移量,用于信号的相位调制,不用时可以去掉,或者加一固定值。

正弦ROM查找表完成

的查表转换,也就是相位到幅度的转换,它的输入是相位调制器的输出,事实上就是ROM的地址。

图5-1DDS原理框图

四、实验内容

1、本实验要完成任务就是设计一个正弦信号发生器,用Verilog设计出同步寄存器、相位累加器等,正弦ROM查找表建议采用定制器件的方法完成,正弦ROM数据文件可以用C代码完成。

2、(选做内容)改变ROM存放数据格式,使之为方波或三角波,设计出可以输出包括正弦、三角及方波的DDS信号源。

五、实验报告

实验六ModelSim仿真测试

1、掌握一般计数器的ModelSim仿真测试方法。

以下是2选一多路选择器的verilog结构描述程序:

下面是它的测试模块:

四、ModelSim仿真步骤

见参考资料《ModelSim操作简介》

五、实验内容

试设计一个含异步复位、同步计数使能和可预置的十进制计数器,请写出它的Verilog程序和testbench模块,并在ModelSim软件平台上进行仿真测试。

根据以上实验内容写出实验报告,包括verilog源程序和verilogtestbench程序,并绘出仿真波形图,总结ModelSim仿真的主要工作流程。

实验七综合设计实验

1、学习动态数码管的工作原理;

2、实现FPGA对四位动态数码管的控制;

3、学习设计硬件乐曲演奏电路以及相关的控制电路;

3、熟悉模块化编程的操作流程。

三、实验内容(三选一)

1、交通灯设计

编写时序控制程序,实现东西、南北向的交通灯计数并亮灯的程序。

东西、南北方向红灯、绿灯亮的时间各为30秒,黄灯亮时间为3秒;

表7.1交通灯控制器的状态转换表

设计提示:

(1)为了实现计时,需要设计一个分频器子程序,输出周期为1秒的时钟信号;

采用倒计时形式,需要设计减法计时器;

(2)为了在七段数码管上正确显示十进制数据,需要设计一个译码器;

(3)主程序使用case语句,采用有限状态机的方式设计。

2、秒表的设计

实现FPGA对四位动态数码管的控制,使其能够正常工作;

应用四位动态数码管做为显示器件设计一个简单秒表。

要求:

(1)秒表的最小计时单位为0.1秒;

(2)设计的秒表能够实现暂停和继续计时的功能。

需要设计3个模块,分别是分频模块、计时模块和数码管动态显示模块。

3、乐曲硬件演奏电路设计

实验内容要求及提示参考教材P200-P202页

根据以上实验内容写出实验方案,包括程序设计,软件编译,仿真结果及分析,硬件测试等内容。

选做实验一秒表的设计

1、实现FPGA对四位动态数码管的控制;

2、熟悉模块化编程的操作流程

三、实验要求

1、秒表的最小计时单位为0.1秒;

2、设计的秒表能够实现暂停和继续计时的功能。

根据以上实验内容写出实验报告,包括程序设计,软件编译,仿真结果及分析,硬件测试等内容。

选做实验二出租车计费器设计

1.了解出租车计费器的工作原理。

2.学会用VerilogHDL语言编写正确的七段码管显示程序。

3.掌握用VerilogHDL编写复杂功能模块。

4.掌握电机测速、显示电器、计数电路的设计方法。

5.熟悉状态机在数字系统设计中的应用

出租车计费器一般都是按公里计费,通常是起步价xx元(xx元可以行走2公里),然后再是xx元/公里。

所以要完成一个出租车计费器,就要有两个计数单位,一个用来计公里,另外一个用来计费用。

通常在出租车的轮子上都有传感器,用来记录车轮转动的圈数,而车轮子的周长是固定的,所以知道了圈数自然也就知道了里程。

在这个实验中,就要模拟出租车计费器的工作过程,用直流电机模拟出租车轮子,通过传感器,可以得到电机每转一周输出一个脉冲波形。

结果的显示用8个七段码管,前四个显示里程,后四个显示费用。

在设计verilog程序时,首先在复位信号的作用下将所有用到的寄存器进行清零,然后开始设定到起步价记录状态,在此状态时,在起步价规定的里程里都一直显示起步价,直到路程超过起步价规定的里程时,系统转移到每公里计费状态,此时每增加一公里,计费器增加相应的费用。

为了便于显示,在编写过程中的数据用BCD码来显示,这样就不存在数据格式转换的问题。

比如表示一个三位数,那么就分别用四位二进制码来表示,当个位数字累加大于9

时,将其清零,同时十位数字加1,依此类推。

本实验要完成的任务就是设计一个简单的出租车计费器,要求是起步价3元,准行1公里,以后1元/公里。

显示部分的七段码管扫描时钟选择时钟模块的1KHz,电机模块的跳线选择GND端,这样通过旋钮电机模块的电位器,即可达到控制电机转速的目的。

另外用按键模块的S1来作为整个系统的复位按钮,每复位一次,计费器从头开始计费。

直流电机用来模拟出租车的车轮子,没转动一圈认为是行走1米,所以每旋转1000圈,认为车子前进1公里。

系统设计是需要检测电机的转动情况,每转一周,计米计数器增加1。

七段码管显示要求为前4个显示里程,后3个显示费用。

选做实验三频率计的设计

1.了解频率计的工作原理。

2.体会FPGA在数字系统设计方面的灵活性。

3.掌握VerilogHDL在测量模块设计方面的技巧。

EDA/SOPC实验系统1台、信号源1台

所谓频率就是周期性信号在单位时间(1s)内变化的次数。

若在一定时间间隔T(也称闸门时间)内测得这个周期性信号的重复变化次数为N,则其频率可表示为

f=N/T

由上面的表示式可以看到,若时间间隔T取1s,则f=N,但是这种频率计仅能测出频率大于或者等于1Hz的情况,且频率越高,精度也越高。

实际应用中,频率计的闸门时间十个可变量,当频率小于1Hz是,闸门时间就要适当放大。

本实验中为了简化实验代码,闸门时间固定为1s,闸门信号是一个0.5Hz的方波,在闸门有效(高电平)期间,对输入的脉冲进行计数,在闸门信号的下降沿时刻,所存当前的计数值,并且清零所有的频率计数器。

由于闸门时间是1s(0.5Hz方波),所以显示的频率是1s钟更新一次,且显示的内容是闸门下降沿时锁存的值。

在设计频率计的时候,八个七段码管最多可以显示99,999,999Hz,因此在设计时候用八个4位二进制码(BCD码)来表示,另外还必须有同样的八个4位二进制码来对输入的频率进行计数,在闸门下降沿的时候,将后者的值锁存到前者的8个寄存器中。

另外为了读数方便,在显示时需要进行判断,假如频率的值小于1KHz并且大于100Hz,那么只显示三位有效值,其他高位全部不显示。

本实验要完成的任务就是设计一个频率计,系统时钟选择实验箱时钟模模块的1KHz时钟,闸门时间为1s(0.5Hz,需要对系统时钟进行2000分频),在闸门为高电平期间,对输入的频率进行计数,当闸门变低的时候,记录当前的频率值,并将频率计数器清零,频率的显示每过2秒刷新一次。

频率计的输入从实验箱的观察模块的探针输入。

附录——FPGA接口对照表

复位信号

信号名称

对应FPGA引脚

RESET

240

串行接口(RS-232)

RXD1

195

TXD1

128

RXD2

223

TXD2

222

VGA接口

R

219

G

218

B

217

HS

216

VS

215

PS/2接口

CLOCK

214

DATA

213

USB接口模块

DB0

228

DB1

233

DB2

234

DB3

235

DB4

236

DB5

237

DB6

238

DB7

239

A0

227

WR

224

RD

225

CS

208

INT

207

SUSPEND

206

LCD显示模块

C/D

226

以太网接口模块

SA0

96/38

SA1

95

SA2

94

SA3

93

SA4

88

SA5

87

SA6

86

SA7

85

SA8

84

SA9

83

SD0

98

SD1

100

SD2

41

SD3

104

SD4

106

SD5

108

SD6

114

SD7

116

SD8

99

SD9

101

SD10

47

SD11

105

SD12

107

SD13

113

SD14

115

SD15

117

82

23

AEN

79

39

21

LED显示模块

D1_1

D1_2

D1_3

D1_4

D1_5

D1_6

D1_7

D1_8

D2_1

D2_2

D2_3

D2_4

D2_5

D2_6

D2_7

D2_8

拨档开关

K1

153

K2

57

K3

56

K4

55

K5

54

K6

53

K7

50

K8

49

按键模块

S1

66

S2

65

S3

64

S4

63

S5

62

S6

61

S7

60

S8

59

键盘阵列模块

ROW0

ROW1

ROW2

ROW3

COL0

COL1

COL2

COL3

七段码显示模块

A

C

D

E

F

DP

42

SEL0

43

SEL1

44

SEL2

45

交通灯显示模块

R1

20

Y1

19

G1

18

R2

17

Y2

16

G2

15

高速DA和高速AD模块

3

4

5

6

7

8

11

12

AD_CLK

AD_OE

2

DA_CLK

13

存储器模块

187

A1

186

A2

185

A3

184

A4

183

A5

170

A6

169

A7

168

A8

167

A9

166

A10

132

A11

196

A12

197

A13

58

A14

126

A15

200

A16

201

A17

131

A18

188

203

A20

202

181

180

179

178

177

176

175

174

DB8

143

DB9

141

DB10

140

DB11

139

DB12

138

DB13

137

DB14

136

DB15

135

DB16

118

DB17

119

DB18

120

DB19

121

DB20

122

DB21

123

DB22

124

DB23

125

DB24

165

DB25

164

DB26

163

DB27

162

DB28

161

DB29

160

DB30

159

DB31

158

SRAM_RD

194

SRAM_WR

173

SRAM_BE0

134

SRAM_BE1

133

SRAM_BE2

156

SRAM_BE3

144

SRAM_CS

182

FLASH_RD

127

FLASH_WR

193

FLASH_CS

音频CODEC模块

SDIN

77

SCLK

78

76

BCLK

75

DIN

74

LRCIN

73

LRCOUT

67

DOUT

68

时钟源模块

28

扬声器模块

SPERKER

46

直流电机模块

PWM

14

SPEED

29

输入输出探测模块

INPUT

152

OUTPUT

48