四输入或非门电路和版图设计Word下载.docx

《四输入或非门电路和版图设计Word下载.docx》由会员分享,可在线阅读,更多相关《四输入或非门电路和版图设计Word下载.docx(12页珍藏版)》请在冰豆网上搜索。

5.用tanner软件中的layout-Edit对电路网表进行LVS检验观察原理图与版图的匹配程度。

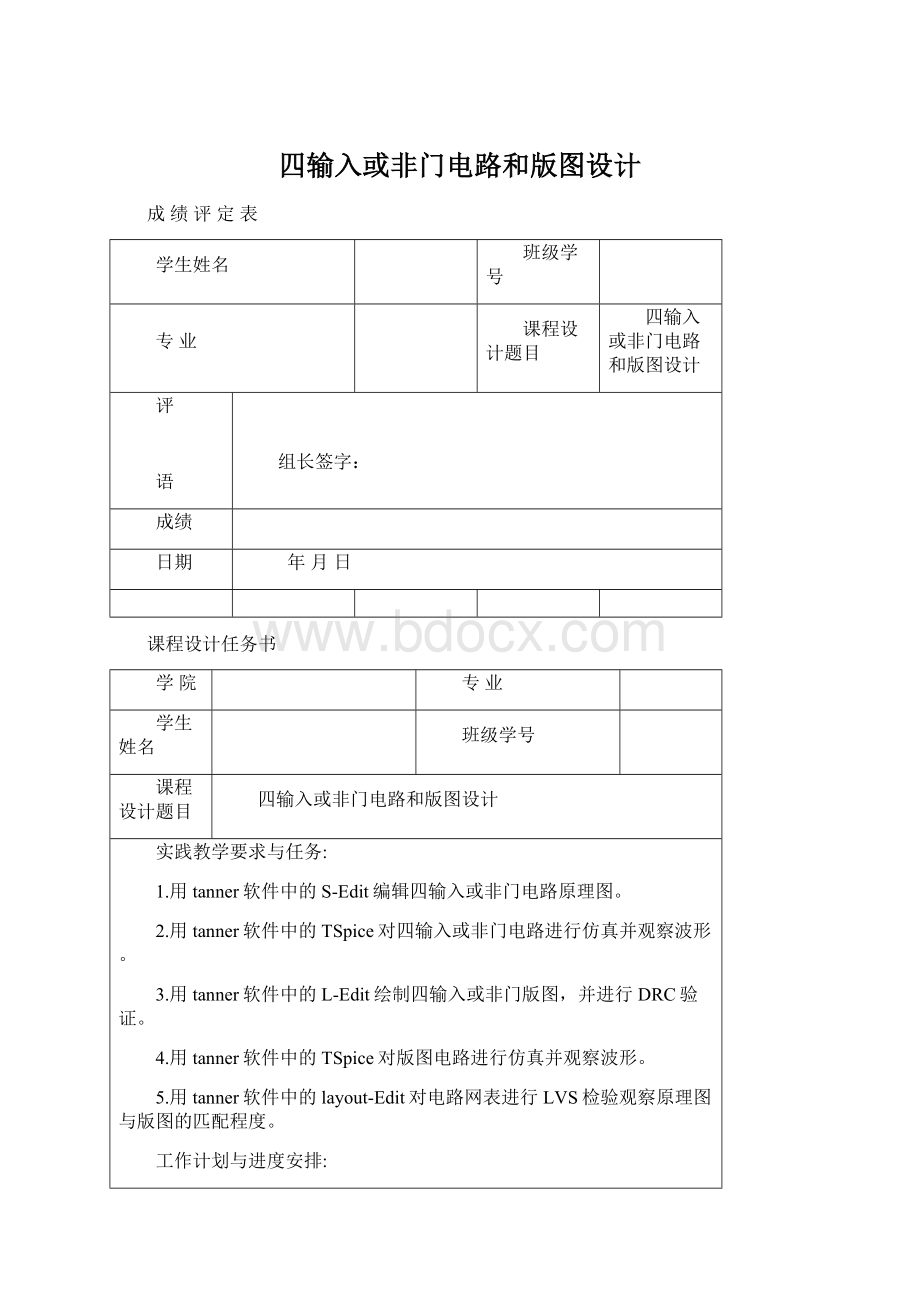

工作计划与进度安排:

第一周

周一:

教师布置课设任务,学生收集资料,做方案设计。

周二:

熟悉软件操作方法。

周三~四:

画电路图

周五:

电路仿真。

第二周

周一~二:

画版图。

周三:

版图仿真。

周四:

验证。

写报告书,验收。

指导教师:

专业负责人:

年月日

学院教学副院长:

1.绪论

设计背景

Tanner集成电路设计软件是由TannerResearch公司开发的基于Windows平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。

L-EditPro是TannerEDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。

L-EditPro包含IC设计编辑器(LayoutEditor)、自动布线系统(StandardCellPlace&

Route)、线上设计规则检查器(DRC)、组件特性提取器(DeviceExtractor)、设计布局与电路netlist的比较器(LVS)、CMOSLibrary、MarcoLibrary,这些模块组成了一个完整的IC设计与验证解决方案。

L-EditPro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。

设计目标

1.用tanner软件中的原理图编辑器S-Edit编辑四输入或非门电路原理图。

4.用tanner软件中的TSpice对四输入或非门的版图电路进行仿真并观察波形。

5.用tanner软件中的layout-Edit对四输入或非门进行LVS检验观察原理图与版图的匹配程度。

2.四输入或非门

四输入或非门电路结构

四输入或非门是最常用的基本功能电路之一,广泛应用于数字逻辑电路电路设计中。

在本次课程设计中,使用tanner软件中的原理图编辑器S-Edit编辑四输入或非门电路原理图。

真值表如下。

表四输入或非门的真值表

原理图如图。

图四输入或非门的原理图

四输入或非门电路仿真

使用TSpice对原理图进行仿真。

首先,生成电路网表,如图。

图生成原理图电路网表

给四输入或非门的输入端加入激励信号。

仿真中高电平为Vdd=5V,低电平为Gnd,并添加输入输出延迟时间。

进行仿真,输出波形。

波形图如下图。

图四输入或非门电路输入输出波形图

四输入或非门的版图绘制

用L-Edit版图绘制软件对四输入或非门电路进行版图绘制,版图结果如图。

图四输入或非门电路版图

进行DRC检测,检测是否满足设计规则。

如图。

图DRC验证结果

四输入或非门的版图电路仿真

同原理图仿真相同,首先生成电路网表。

图生成版图电路网表

添加激励、电源和地,同时观察输入输出波形,波形如图。

图四输入或非门电路版图输入输出波形图

四输入或非门电路的版图仿真波形与原理图的仿真波形,基本一致,并且符合输入输出的逻辑关系,电路的逻辑设计正确无误。

LVS检查匹配

对四输入或非门进行LVS检查验证,首先添加输入输出文件,选择要查看的输出,观察输出结果检查四输入或非门原理图与版图的匹配程度。

首先导入网表,如下图。

图导入网表

输出结果如图。

图电路LVS检查匹配图

网表匹配,设计无误。

总结

通过两周的课程设计学习,综合运用所学的知识完成了设计任务。

使我更进一步熟悉了专业知识,并深入掌握仿真方法和工具、同时为毕业设计打基础的实践环节。

进一步熟悉设计中使用的主流工具,学习了良好的技术文档撰写方法;

了解后端设计;

加深综合对所学课程基础知识和基本理论的理解好掌握,培养了综合运用所学知识,独立分析和解决工程技术问题的能力;

培养了在理论计算、制图、运用标准和规范、查阅设计手册与资料以及应用工具等方面的能力,逐步树立正确的设计思想。

在老师布置好题目后,我仔细进行设计,通过查阅各种参考书籍,最终把实验做出来了,达到了老师对本实验的要求。

在这次设计中我收获颇丰,首先最直接的收获就是我巩固了这节课所学的知识,把它运用到实践中去,并且学到了许多在课本中所没有的知识。

通过查阅相关知识,进一步加深对tannerr的了解。

其次,我们不管做什么都不能粗心,如我们输入程序时把字母打错了时,保存文件时名称与程序中的名称不一样时,都会导致编译错误,在此过程中虽然浪费了不少时间,但这也让我注意到实际做设计时应该应该注意的问题,意识到自己的不足,对学过的知识了解不够深刻,掌握的不足够。

通过对典型IC集成电路的原理图和版图的绘制及仿真,对模拟电路的工作原理有了进一步的了解。

再借助tanner软件模拟电路的原理图绘制及其版图生成,熟悉了tanner在此方面的应用,以增强计算机辅助电路模拟与设计的信心。

总的来说,这次设计还算成功,也让我明白了要把理论知识与实践结合起来,从实践中强化自己的理论,才能更好提高自己的实际动手能力和独立思考能力。

如果在设计过程中遇到问题时,我们要有耐心的查找错误,这也是学习的过程。

参考文献

[1]AlanArtofAnalongLayoutsecondEdition模拟电路版图的艺术.第二版.电子工业出版社,2013。

[2]王颖著.集成电路版图设计与TannerEDA工具使用.第二版.西安电子科技大学出版社,2009。

[3]曾庆贵著.集成电路版图基础.机械工业出版社,2008。

[4]张为著.集成电路版图基础.清华大学出版社,2009。

[5]廖谷平,陆瑞强著.TannerPro集成电路设计与布局实战指导.科学出版社2007

附录一:

原理图网表

.include"

D:

\tanner\TSpice70\models\"

VddVddGnd5

VAAGndPULSE(05010n10n50n100n)

VBBGndPULSE(05010n10n50n200n)

VCCGndPULSE(05010n10n30n100n)

VDDGndPULSE(05010n10n50n150n)

.tran/op10n800nmethod=bdf

.printtranv(Y)v(A)v(B)v(C)v(D)

*SPICEnetlistwrittenbyS-EditWin32

*WrittenonJul3,2013at16:

20:

23

*Waveformprobingcommands

.probe

.optionsprobefilename="

"

+probesdbfile="

C:

\Users\SHARK\Desktop\zou\"

+probetopmodule="

Module0"

*Maincircuit:

Module0

M1YAGndGndNMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M2YBGndGndNMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M3YCGndGndNMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M4YDGndGndNMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M5YDN5VddPMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M6N5CN6VddPMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M7N6BN7VddPMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M8N7AVddVddPMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

*Endofmaincircuit:

附录二:

版图网表

*CircuitExtractedbyTannerResearch'

sL-EditVersion/ExtractVersion;

*TDBFile:

C:

\Users\SHARK\Desktop\zou\

*Cell:

Cell0Version

*ExtractDefinitionFile:

D:

\tanner\LEdit90\Samples\SPR\example1\

*ExtractDateandTime:

07/03/2013-15:

15

.printtranv

(2)v(A)v(B)v(C)v(D)

*Warning:

LayerswithUnassignedAREACapacitance.

*<

PolyResistorID>

Poly2ResistorID>

NDiffResistorID>

PDiffResistorID>

PBaseResistorID>

NWellResistorID>

LayerswithUnassignedFRINGECapacitance.

PadComment>

Poly1-Poly2CapacitorID>

LayerswithZeroResistance.

NMOSCapacitorID>

PMOSCapacitorID>

*NODENAMEALIASES

*1=D,

*3=Gnd(2,

*4=Vdd(5,

*5=A(8,

*6=B(21,

*9=C,

M12D8VddPMOSL=3uW=11u

*M1DRAINGATESOURCEBULK(4952

M2GndD2GndNMOSL=3uW=11u

*M2DRAINGATESOURCEBULK(4952

M38C10VddPMOSL=3uW=11u

*M3DRAINGATESOURCEBULK(3538

M410B7VddPMOSL=3uW=11u

*M4DRAINGATESOURCEBULK(2124

M57AVddVddPMOSL=3uW=11u

*M5DRAINGATESOURCEBULK(710

M62CGndGndNMOSL=3uW=11u

*M6DRAINGATESOURCEBULK(3538

M7GndB2GndNMOSL=3uW=11u

*M7DRAINGATESOURCEBULK(2124

M82AGndGndNMOSL=3uW=11u

*M8DRAINGATESOURCEBULK(710