先行进位加法器Word格式.docx

《先行进位加法器Word格式.docx》由会员分享,可在线阅读,更多相关《先行进位加法器Word格式.docx(9页珍藏版)》请在冰豆网上搜索。

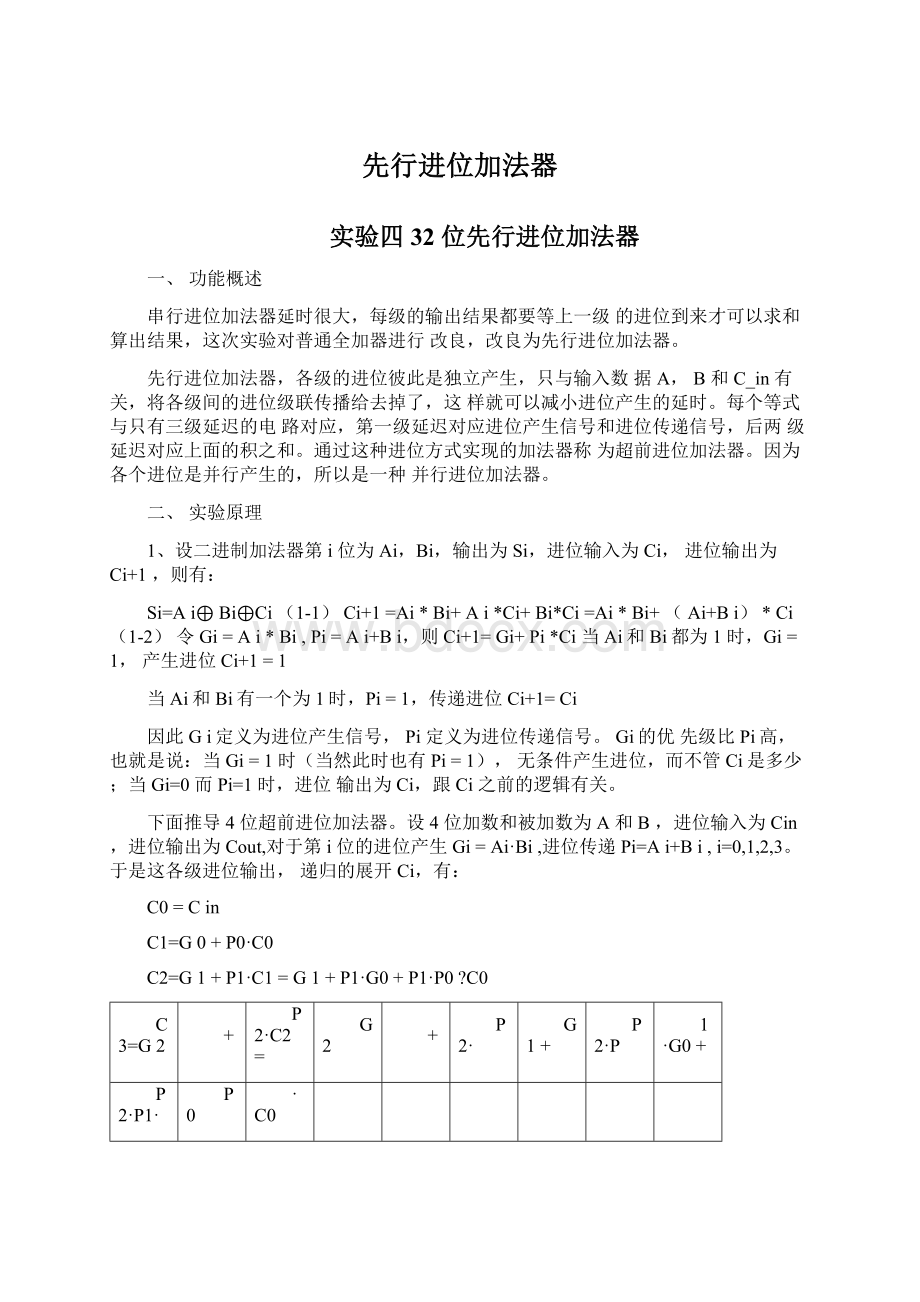

P2·

C2=

G2

G1+

P

1·

G0+

P1·

P0

·

C4=G3

P3·

C3=

G3

G2+

2·

P1

G0+P3·

P0·

(

1-3)

Cout=C4

由此可以看出,各级的进位彼此独立产生,只与输入数据Ai、Bi和Cin有关。

2、接口说明

表1:

32位超前进位加法器接口信号说明表

序号

接口信号名称

方向

说明

备注

1

A[31:

0]

I

输入数据

2

B[31:

3

S[31:

O

加法结果

4

count

最高位进位

3、结构框图

A31~28B31~28A27~24B27~24A23~20B23~20A19~16B19~16

A15~12B15~12A11~8B11~8A7~4B7~4A3~0B3~0

三、实验方案方案一:

分为两个模块:

1个4位add_4和1个add_32,其中add_32调用4个add_4.

首先设计4位超前进位加法器:

框图如下:

设计好四位的之后,开始调用四位的实现32位的

pg

方案二:

分为五个模块:

(1)计算传播值和产生值模块:

模块

(2)超前进位模块:

cla模块

(3)加法求和模块:

sum模块

(4)求和并按输出a,b,c_in分组:

bit_slice模块

(5)32位超前进位加法器总模块:

cla_32总框图:

四、验证方案:

对32位的两个输入赋值:

当a=32'

b1000_0001_0111_1011_1101_1001_1101_1000;

b=32'

b0111_1000_

0001_

1000_

1100_

0111_

0101_

0001;

c_in=1'

b0;

结果:

s=32'

b1111

_1001

_0100

_1010

_0001

_0010_

1001;

b1000_0001_

1011_

1101_

1001_

1000;

b1;

1010;

来对波形进行观察,看波形是否正确。

五、实验代码:

方案一:

(1)add_32模块顶层模块:

2)4位add_4模块方案二:

(1)cla_32顶层模块:

modulecla_32(a,b,c_in,s,count);

input[31:

0]a,b;

inputc_in;

output[31:

0]s;

outputcount;

wire[7:

0]gg,gp,gc;

wire[3:

0]ggg,ggp,ggc;

wiregggg,gggp;

bit_slice

b1(.a(a[3:

0]),.b(b[3:

0]),.c_in(gc[0]),.s(s[3:

0]),.gp(gp[0]),.gg(gg[0]));

bit_slice

b2(.a(a[7:

4]),.b(b[7:

4]),.c_in(gc[1]),.s(s[7:

4]),.gp(gp[1]),.gg(gg[1]));

b3(.a(a[11:

8]),.b(b[11:

8]),.c_in(gc[2]),.s(s[11:

8]),.gp(gp[2]),.gg(gg[2]));

b4(.a(a[15:

12]),.b(b[15:

12]),.c_in(gc[3]),.s(s[15:

12]),.gp(gp[3]),.gg(gg[3]));

b5(.a(a[19:

16]),.b(b[19:

16]),.c_in(gc[4]),.s(s[19:

16]),.gp(gp[4]),.gg(gg[4]));

b6(.a(a[23:

20]),.b(b[23:

20]),.c_in(gc[5]),.s(s[23:

20]),.gp(gp[5]),.gg(g

g[5]));

b7(.a(a[27:

24]),.b(b[27:

24]),.c_in(gc[6]),.s(s[27:

24]),.gp(gp[6]),.gg(gg[6]));

b8(.a(a[31:

28]),.b(b[31:

28]),.c_in(gc[7]),.s(s[31:

28]),.gp(gp[7]),.gg(gg[7]));

cla

c0(.p(gp[3:

0]),.g(gg[3:

0]),.c_in(ggc[0]),.c(gc[3:

0]),.gp(ggp[0]),.gg(ggg[0]));

c1(.p(gp[7:

4]),.g(gg[7:

4]),.c_in(ggc[1]),.c(gc[7:

4]),.gp(ggp[1]),.gg(ggg[

1]));

assignggp[3:

2]=2'

b11;

assignggg[3:

b00;

clac2(.p(ggp),.g(ggg),.c_in(c_in),.c(ggc),.gp(gggp),.gg(gggg));

assigncount=gggg|(gggp&

c_in);

endmodule

2)pg模块:

modulepg(a,b,p,g);

input[3:

output[3:

0]p,g;

assignp=a^b;

assigng=a&

b;

(3)cla模块:

modulecla(p,g,c_in,c,gp,gg);

input[3:

0]c;

outputgp,gg;

function[99:

0]do_cla;

begin:

label

integeri;

reggp,gg;

reg[3:

gp=p[0];

gg=g[0];

c[0]=c_in;

for(i=1;

i<

4;

i=i+1)

begin

gp=gp&

p[i];

gg=(gg&

p[i])|g[i];

c[i]=(c[i-1]&

p[i-1])|g[i-1];

end

do_cla={c,gp,gg};

end

endfunction

assign{c,gp,gg}=do_cla(p,g,c_in);

endmodule

(4)sum模块:

modulesum(a,b,c,s);

0]a,b,c;

output[3:

wire[3:

0]t=a^b;

assigns=t^c;

5)bit_slice模块:

modulebit_slice(a,b,c_in,s,gp,gg);

0]p,g,c;

pgi1(a,b,p,g);

clai2(p,g,c_in,c,gp,gg);

sumi3(a,b,c,s);

(6)激励代码:

modulecla32_tb;

//Inputs

reg[31:

0]a;

0]b;

regc_in;

//Outputs

wire[31:

wirecount;

//InstantiatetheUnitUnderTest(UUT)cla_32uut(

.a(a),

.b(b),

.c_in(c_in),

.s(s),

.count(count)

);

initialbegin

//InitializeInputs

a=0;

b=0;

c_in=0;

//Wait100nsforglobalresettofinish

#10

a=32'

b1000_

0001

0111

1001

1101

_1000;

b0111_

1000

0101

_0001;

//Addstimulushereendendmodule

六、波形图说明1、仿真波形

2、结果说明

对于三个输入:

b0111_1000_0001_1000_1100_0111_0101_0001;

c_in=1'

结果与实验方案的相同,结果仿真正确.

七、实验总结

对于这次实验,自己在老师布置完,努力做了几个下午,不断调试才得到正确结果波形,是非常有收获的。

同时我也采用了两种方案来设计,真正的对先行进位加法器有了全新的认识,对于它的内部工作原理深有体会,对自己以后的电路设计奠定了基础,自己以后会更加努力。