CMOS数字集成电路设计八位加法器实验报告文档格式.docx

《CMOS数字集成电路设计八位加法器实验报告文档格式.docx》由会员分享,可在线阅读,更多相关《CMOS数字集成电路设计八位加法器实验报告文档格式.docx(19页珍藏版)》请在冰豆网上搜索。

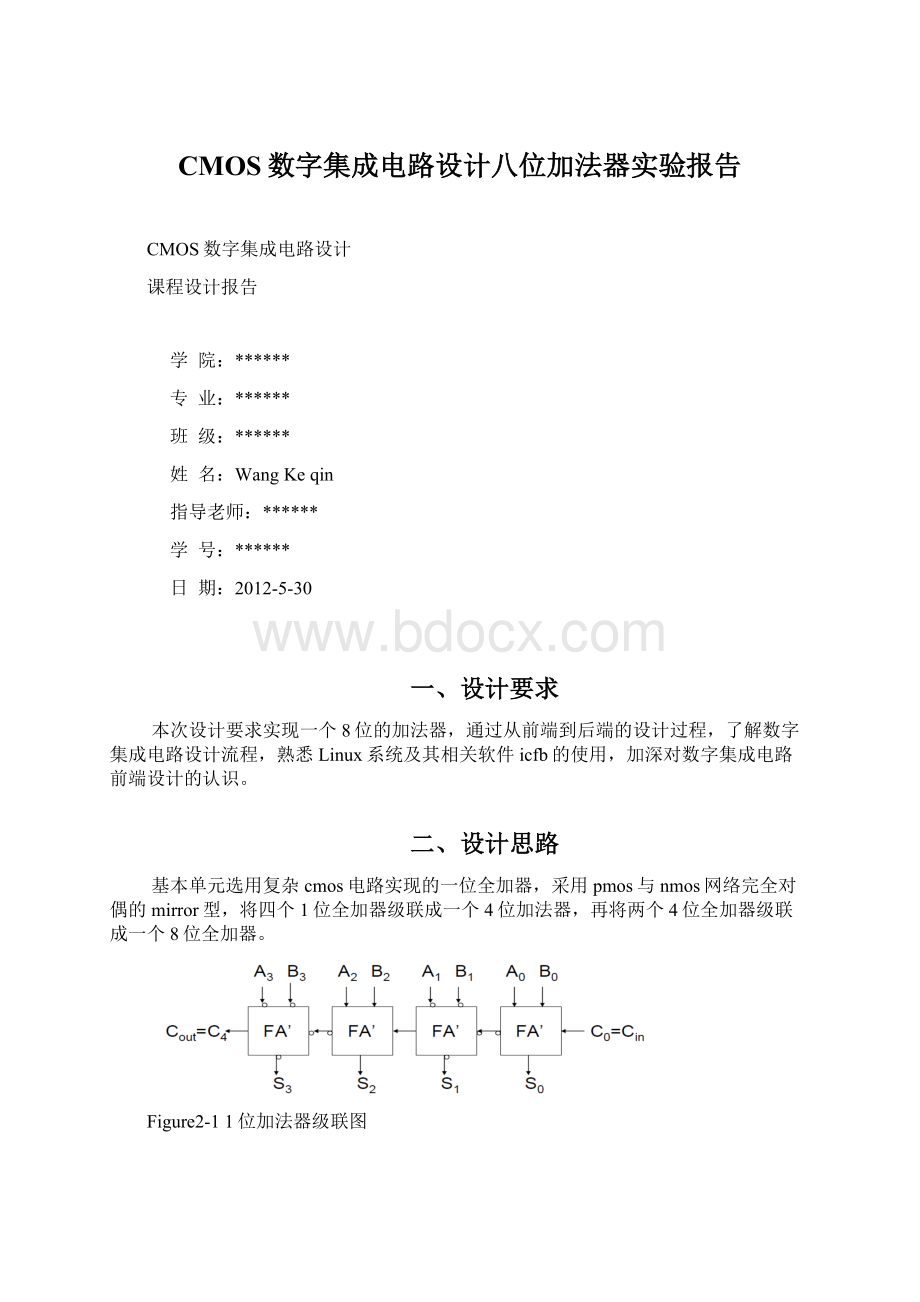

其中A、B为两个输入信号也即两个一位加数,Cin为前一位的进位输入信号,Co为当前的进位输出信号,So为和输出信号。

2)生成符号图

Figure3-21位全加器的符号图

如图Fig.3-2所示,为检查并保存1位全加器原理图后生成的符号图,左侧为输入信号A、B、Cin,右侧为输出信号,Co和So。

3)建立测试激励源

为了验证原理图是否满足逻辑要求,新建一个关于激励源的cellview,建立functional文件,编辑测试激励源的verilog文件,遍历真值表,并生成相应的符号。

Figure3-31位全加器的测试激励

如图Fig.3-3所示,为用verilog编写的1位全加器的测试激励。

初始状态三个输入信号都设为1,之后给A、B、Cin赋值三个不同频率的脉冲信号,能遍历三个输入中,全0、全1、两个1、一个1的所有情况。

4)测试电路

Figure3-41位全加器的测试电路(模拟)

Figure3-51位全加器的测试电路(数模混合)

如图Fig.3-4,、Fig.3-5所示,为1位全加器的测试电路,Fig.3-4为加模拟信号激励,Fig.3-5为加数字信号激励。

从中比较可以看出,当输入信号较多时,才用数目混合测试要比采用模拟激励测试要方便,电路会简单些。

所以在接下来的4位全加器和8位全加器测试电路中,均采用数模混合方式。

5)波形仿真

Figure3-61位全加器的仿真波形a

Figure3-71位全加器的仿真波形b

如图Fig.3-6,、Fig.3-7所示,为1位全加器的仿真波形图。

从图Fig.3-6中可以看出,仿真波形结果与真值表相符合,从图Fig.3-7中可以看出1位全加器的延时为0.1ns.

(二)4位全加器的电路设计与验证

Figure3-84位加法器的原理图

如图Fig.3-8所示,为4位加法器的原理图设计。

4位加法器采用4个1位加法器直接串联,前一级的输出直接连到下一级的输入。

左侧为四位输入信号A[3:

0]、B[3:

0]和进位输入Cin,右侧为四位输出信号D[3:

0]和进位输出Co.

Figure3-94位加法器的符号图

如图Fig.3-9所示,为检查并保存4位全加器原理图后生成的符号图,左侧为输入信号A[3:

0]、Cin,右侧为输出信号,Co和D[3:

0]。

为验证原理图是否满足逻辑要求,新建一个关于激励源的cellview,建立functional文件,编辑测试激励源的verilog文件,遍历真值表,并生成相应的符号。

Figure3-104位全加器的测试激励

如图Fig.3-10所示,为用verilog编写的4位全加器的测试激励。

初始状态进位输入设为0,a[3:

0]设为1001,b[3:

0]设为0111;

之后分别给每一位加数不同周期的脉冲信号,使得激励信号能够遍历所有的情况。

Figure3-114位全加器的测试电路(数模混合)

如图Fig.3-11所示,为4为全加器测试电路,采用数目混合形式。

从图中可以看出,采用数模混合测试方法,电路比较简单,不需要每个输入信号都给一个模拟脉冲,简洁、方便。

Figure3-124位全加器的仿真波形

如图Fig.3-12所示,为4为全加器的仿真波形图,从图中可以看出,仿真波形结果与4位全加器真值表相符合。

其中,关键路径上的延时为0.37ns,延时较大,这与每一级输出都加入一个反相器有很大关系。

(三)8位全加器的电路设计与验证

Figure3-134位加法器的原理图

如图Fig.3-13所示,为8位加法器的原理图设计。

8位加法器采用2个4位加法器串联,前一级的输出直接连到下一级的输入。

其中A[7:

0]、B[7:

0]分别为八位输入信号,Cin为进位输入信号,D[7:

0]为输出信号,Co为进位输出信号。

Figure3-148位加法器的符号图

如图Fig.3-9所示,为检查并保存8位全加器原理图后生成的符号图,左侧为两个八位的输入信号A[7:

0]和进位输入信号Cin,右侧为A[7:

0]与B[7:

0]的和输出信号D[7:

0]和进位输出信号Co。

3)测试激励源

Figure3-158位全加器的测试激励

如图Fig.3-15所示,为用verilog编写的8位全加器的测试激励。

初始状态进位输入设为0,a[7:

0]设为10100111,b[7:

0]设为10011101;

之后分别给每一位加数不同周期的脉冲信号,进位输入Cin设置为周期脉冲信号,使得激励信号能够遍历所有的情况。

Figure3-168位全加器的测试电路(数模混合)

如图Fig.3-16所示,为8位全加器测试电路,采用数模混合形式。

从图中可以看出,采用数模混合测试方法,电路比较简单,不需要每个输入信号都给一个模拟脉冲。

当输入信号数目比较大时,采用数模混合方式更加有效。

Figure3-178位加法器的仿真波形a

Figure3-188位加法器的仿真波形b

Figure3-198位加法器的仿真波形c

如图Fig.3-17、Fig.3-18、Fig.3-19所示,为8位全加器的仿真波形,电路关键路径为从Cin到Co的路径,延时为160.64-159.98=0.66ns。

Figure3-20关键路径上的最大延时波形

如图Fig.3-20所示,为Cin到Co路径上的最大延时波形图。

当A[7:

0]=8’hff,B[7:

0]=8’h00,Cin=1时候,测出Cin和Co的状态转换时间差即为关键路径上的最大延时。

从图中可以看出,关键路径上的最大延时为80.87ns-80ns=0.87ns。

Figure3-21关键路径的上升时间波形

如图Fig.3-21所示,为关键路径上的上升时间波形图,从图中可以看出,上升时间为80.536-80.445=0.091ns。

Figure3-22关键路径的下降时间波形

如图Fig.3-22所示,为关键路径上的下降时间波形图,从图中可以看出,下降时间为160.628-160.566=0.062ns。

下降时间比上升时间小的原因可能是pmos比nmos管速度慢。

6)电路参数

************************************************************************

*auCdlNetlist:

*

*LibraryName:

wangkeqin2

*TopCellName:

8_full_adder

*ViewName:

schematic

*Netlistedon:

May2504:

46:

152012

*.EQUATION

*.SCALEMETER

*.MEGA

*.GLOBALgnd!

+vdd!

*.PINgnd!

*+vdd!

*CellName:

1_full_adder

.SUBCKT1_full_adderABCinCoSo

*.PININFOCo:

OSo:

OA:

BB:

BCin:

B

Mpmos_3p315Sonet90vdd!

vdd!

pmos_3p3W=2uL=350.0nM=1.0

Mpmos_3p314net90Bnet13vdd!

pmos_3p3W=3uL=350.0nM=1.0

Mpmos_3p313net13Anet17vdd!

Mpmos_3p312net17Cinvdd!

Mpmos_3p311net90net114net34vdd!

pmos_3p3W=4uL=350.0nM=1.0

Mpmos_3p310net34Cinvdd!

Mpmos_3p39net34Bvdd!

Mpmos_3p38net34Avdd!

Mpmos_3p37net114Cinnet41vdd!

Mpmos_3p30net41Avdd!

Mpmos_3p31net41Bvdd!

Mpmos_3p36net114Anet53vdd!

Mpmos_3p35net53Bvdd!

Mpmos_3p34Conet114vdd!

Mnmos_3p315Sonet90gnd!

gnd!

nmos_3p3W=1uL=350.0nM=1.0

Mnmos_3p314net66Cingnd!

nmos_3p3W=1.5uL=350.0nM=1.0

Mnmos_3p313net70Bnet66gnd!

Mnmos_3p312net90Anet70gnd!

Mnmos_3p311net86Cingnd!

nmos_3p3W=2uL=350.0nM=1.0

Mnmos_3p310net86Bgnd!

Mnmos_3p39net86Agnd!

Mnmos_3p38net90net114net86gnd!

Mnmos_3p37Conet114gnd!

Mnmos_3p36net98Bgnd!

Mnmos_3p35net114Anet98gnd!

Mnmos_3p32net110Bgnd!

Mnmos_3p31net110Agnd!

Mnmos_3p30net114Cinnet110gnd!

.ENDS

4_full_adder

.SUBCKT4_full_adderA0A1A2A3B0B1B2B3CinCoD0D1D2D3

*.PININFOA0:

IA1:

IA2:

IA3:

IB0:

IB1:

IB2:

IB3:

ICin:

ICo:

OD0:

OD1:

OD2:

O

*.PININFOD3:

XI3A0B0Cinnet6D0/1_full_adder

XI2A1B1net6net11D1/1_full_adder

XI1A2B2net11net16D2/1_full_adder

XI0A3B3net16CoD3/1_full_adder

.SUBCKT8_full_adderA0A1A2A3A4A5A6A7B0B1B2B3B4B5B6B7CinCoD0

+D1D2D3D4D5D6D7

IA4:

IA5:

IA6:

IA7:

IB4:

I

*.PININFOB5:

IB6:

IB7:

OD3:

OD4:

OD5:

OD6:

OD7:

XI1A0A1A2A3B0B1B2B3Cinnet51D0D1D2D3/4_full_adder

XI0A4A5A6A7B4B5B6B7net51CoD4D5D6D7/4_full_adder

四、版图设计与验证

(一)1位全加器的版图设计与验证

1)1位全加器的版图设计

Figure4-11位全加器的版图

如图Fig.4-1所示,为1位全加器的版图设计,版图设计也采用nmos和pmos完全对称的镜像网路设计,上部分为pmos下部分为nmos。

pmos放一起,nmos放一起,尽量减少版图面积,和缩短布线长度。

从图中可以看出版图面积约为15.750*25.775=405.96um2,面积比较小。

2)1位全加器的DRC规则验证

Figure4-21位全加器版图的DRC验证

DRC验证是为了检验设计的版图是否满足设计规则检查。

如图Fig.4-2所示,为1位全加器版图的DRC验证结果。

从图中可以看出,最后DRC的结果又5个错误,都是金属密度的错误。

这些错误在集成电路前端设计阶段可以忽略,在后端设计中可以通过填充虚拟金属或是dummyfill来弥补。

3)1位全加器的LVS验证

Figure4-31位全加器的LVS验证结果

LVS检查是为了验证所画的版图和原理图是否匹配。

如图Fig.4-3所示,为1位全加器的LVS验证结果,从图中可以看出,1位全加器的版图和原理图匹配,满足LVS验证。

4)错误及解决办法

1)NWELL间距过小

解决办法:

将所有的pmos管都用一块大的NMELL区包住。

2)LVS没通过但显示0个错误提示

可能是由于vdd和gnd标签没有打,或是标签没有用相应的金属层标签来标注。

加上vdd!

和gnd!

用相应的金属标示层标记vdd!

与gnd!

后即通过lvs,

3)Lvs时cmos管模型不匹配

出现28个管子模式不匹配的问题,是由于从原理图中提取的netlist网表中的mos管类型为PM或是NM,而版图中为pmos_3p3和nmos_3p3。

修改网表。

在lvs工作路径下用vi编辑器打开相应的网表文件。

通过指令“:

%s/NM/nmos_3p3/”将网表中的所有的NM全部替换为nmos_3p3,再用命令“:

%s/PM/pmos_3p3/”将网表中所有的PM都替换成pmos_3p3。

之后按Esc键退出编辑模式,再通过命令“:

wq”保存并退出vi编辑模式。

在LVS的输入设置选项中把“从原理图输出网表”选项去掉,再进行LVS即通过检查。

(二)4位全加器的版图设计与验证

1)4位全加器的版图设计

Figure4-44位全加器的版图

如图Fig.4-4为4位全加器的版图设,直接调用一位全加器的版图单元,将4个一位全加器级联成一个4位全加器。

从图中可以看出,4位全加器的面积约为15.725*102.95=1618.88875um2。

2)4位全加器的DRC规则验证

Figure4-54位全加器的DRC验证结果

如图Fig.4-5所示,为4位全加器的DRC验证结果,从图中可以看出4位全加器的设计满足DRC规则验证。

3)4位全加器的LVS验证

Figure4-64位全加器的LVS验证结果

如图Fig.4-6所示,为4位全加器的LVS验证结果,从图中可以看出,4位全加器的设计原理图和版图对应,满足LVS验证。

1)DRC时显示0个error

原因是由于四个1位全加器的vdd及gnd没有全接在一起。

解决办法:

把四个vdd和gnd用金属1连在一起就可以解决问题。

2)Lvs时A2,B2,A3,B3连接上的栅极连线都没有与原理图对应上

四个1位全加器串联时,打标签时候把A2、A3、B2、B3写反了,改正过来即可解决问题。

(三)8位全加器的版图设计与验证

1)8位全加器的版图设计

Figure4-78位全加器的版图

如图Fig.4-7所示,为8位全加器的版图设计。

调用两个4位全加器版图级联,生成一个8位全加器。

为了方便连接,将下面的一个4位全加器的版图翻转180度,使上面4位全加器的输出接到下面的输入。

从图中可以看出,8位全加器的版图面积约为102.725*31.975=3284.63um2。

2)8位全加器的DRC规则验证

Figure4-88位全加器的DRC验证结果

如图Fig.4-8所示,为8位全加器的DRC验证结果,从图中可以看出8位全加器的设计满足DRC规则验证。

3)8位全加器的LVS验证

Figure4-98位全加器的LVS验证结果

如图Fig.4-9所示,为8位全加器的LVS验证结果,从图中可以看出,8位全加器的设计原理图和版图对应,满足LVS验证。

LVS时,missingnetNet30

由于8位全加器的版图是由两个四位全加器级联而成,为了连接方便把下面的4位全加器翻转了180度,gnd放在中间,最小间隔,两个gnd忘记用金属1连接了。

连接起来再runLVS即可解决问题。

五、设计总结

实验里我们通过一个8位加法器的设计熟悉了cadence软件icfb的使用和集成电路前端设计的整体流程。

第一次画8位全加器,由于没有经验,管子排列相当凌乱,面积比较大,布线杂乱无章,虽然第一次功能实现了,但非常不科学。

之后又从新画了一遍,第二次采用镜像行的MOS管,借鉴第一次的经验,第二次画图就比较快,而且占用面积也较小,功能仿真也比较好。

完成这次设计,花费的时间挺多的,经常在实验室一画就是一天,遇到了很多问题,也请教了老师和好多同学。

完成了8位全加器的设计还真的挺有收获的,由于第一次做这样门级的电路还是有很多不完善的地方:

比如对电源和地的处理;

没有每隔3-4级加一个缓冲级的buffer,导致延时较大;

而且由于时间的问题没有做进位旁路和曼彻斯特进位链使得电路实际上就是八级1位加法器直接相连,最后的延迟时间达到了0.87ns,以后有机会会重新完善电路的设计。