CPLD设计BCD的优先编码器BCD码十进制加法计数器8位的左右移位寄存器电路时钟分配电路步.docx

《CPLD设计BCD的优先编码器BCD码十进制加法计数器8位的左右移位寄存器电路时钟分配电路步.docx》由会员分享,可在线阅读,更多相关《CPLD设计BCD的优先编码器BCD码十进制加法计数器8位的左右移位寄存器电路时钟分配电路步.docx(17页珍藏版)》请在冰豆网上搜索。

CPLD设计BCD的优先编码器BCD码十进制加法计数器8位的左右移位寄存器电路时钟分配电路步

1设计一个BCD的优先编码器电路,输入为10个开关的状态,要求输出开

关对应的编码。

输出编码用4位表示,第一个开关为0时,输出为0000时,第二个开关为0时,输出为0001时,......第10个开关为0时,输出为1001。

第10个开关的优先级最高。

当没有按键按下时,输出信号E为1。

有按键按下时,输出信号E为0。

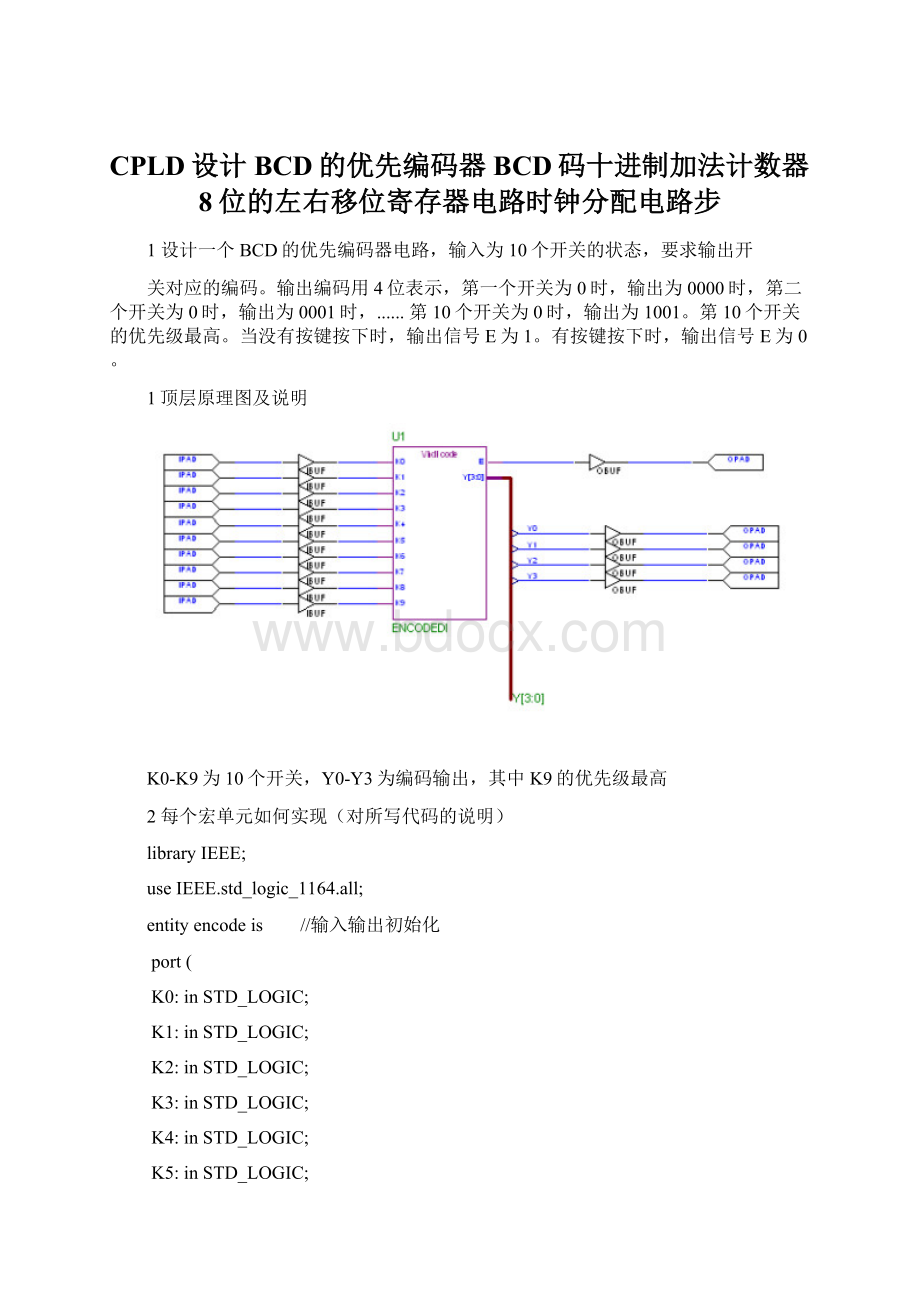

1顶层原理图及说明

K0-K9为10个开关,Y0-Y3为编码输出,其中K9的优先级最高

2每个宏单元如何实现(对所写代码的说明)

libraryIEEE;

useIEEE.std_logic_1164.all;

entityencodeis//输入输出初始化

port(

K0:

inSTD_LOGIC;

K1:

inSTD_LOGIC;

K2:

inSTD_LOGIC;

K3:

inSTD_LOGIC;

K4:

inSTD_LOGIC;

K5:

inSTD_LOGIC;

K6:

inSTD_LOGIC;

K7:

inSTD_LOGIC;

K8:

inSTD_LOGIC;

K9:

inSTD_LOGIC;

Y:

outSTD_LOGIC_VECTOR(3DOWNTO0);

E:

outSTD_LOGIC

);

endencode;

architectureencode_archofencodeis

begin

E<=K0ANDK1ANDK2ANDK3ANDK4ANDK5ANDK6ANDK7ANDK8ANDK9;

//如果都是1的话则E为0

Y<="1001"WHEN(K9='0')ELSE//进行优先编码,根据优先级依次判断

"1000"WHEN(K9='1'ANDK8='0')ELSE

"0111"WHEN(K9='1'ANDK8='1'ANDK7='0')ELSE

"0110"WHEN(K9='1'ANDK8='1'ANDK7='1'ANDK6='0')ELSE

"0101"WHEN(K9='1'ANDK8='1'ANDK7='1'ANDK6='1'ANDK5='0')ELSE

"0100"WHEN(K9='1'ANDK8='1'ANDK7='1'ANDK6='1'ANDK5='1'ANDK4='0')ELSE

"0011"WHEN(K9='1'ANDK8='1'ANDK7='1'ANDK6='1'ANDK5='1'ANDK4='1'ANDK3='0')ELSE

"0010"WHEN(K9='1'ANDK8='1'ANDK7='1'ANDK6='1'ANDK5='1'ANDK4='1'ANDK3='1'ANDK2='0')ELSE

"0001"WHEN(K9='1'ANDK8='1'ANDK7='1'ANDK6='1'ANDK5='1'ANDK4='1'ANDK3='1'ANDK2='1'ANDK1='0')ELSE

"0000"WHEN(K9='1'ANDK8='1'ANDK7='1'ANDK6='1'ANDK5='1'ANDK4='1'ANDK3='1'ANDK2='1'ANDK1='1'ANDK0='0')ELSE

"XXXX";//若无法确定状态,则输出XXXX

endencode_arch;

3时序仿真结果

4时序分析

=====================================================================

Timingconstraint:

Defaultperiodanalysis

41itemsanalyzed,0timingerrorsdetected.

Maximumdelayis13.241ns.

=====================================================================

Timingconstraint:

Defaultnetenumeration

25itemsanalyzed,0timingerrorsdetected.

Maximumnetdelayis2.435ns.

=====================================================================

2设计一个2位的BCD码十进制加法计数器电路,输入为时钟信号CLK,进位

输入信号CIN,每个BCD码十进制加法计数器的输出信号为D、C、B、A和进位输出信号COUT,输入时钟信号CLK用固定时钟,进位输入信号CIN.

1顶层原理图及说明

以第四位计数器的进位段作为高四位的时钟信号,因为设计为到1001B(9)进位输出,所以再输出端加了一个非门,翻转输出,达到延迟一个时钟信号的目的。

2每个宏单元如何实现(对所写代码的说明)

libraryIEEE;

useIEEE.std_logic_1164.all;

entityBCDis

port(//输入输出初始化

CIN:

inSTD_LOGIC;

CLK:

inSTD_LOGIC;

R:

inSTD_LOGIC;

D:

outSTD_LOGIC;

C:

outSTD_LOGIC;

B:

outSTD_LOGIC;

A:

outSTD_LOGIC;

COUT:

outSTD_LOGIC

);

endBCD;

architectureBCD_archofBCDis

typeStateTypeis(st0,st1,st2,st3,st4,st5,st6,st7,st8,st9);//共有10个状态

signalpresent_state,next_state:

StateType;

signalF:

STD_LOGIC_VECTOR(3downto0);

begin

process(CLK)

begin

if(CLK'eventANDCLK='1')then//时钟信号上升沿触发

ifR='1'then//复位信号

present_state<=st0;//采用多进程的摩尔状态机设计方法

else

present_state<=next_state;

endif;

endif;

endprocess;

process(present_state)

begin

casepresent_stateis//每个状态分别对应一个BCD码的输出

whenst0=>F<="0000";

COUT<='0';

next_state<=st1;

whenst1=>F<="0001";

COUT<='0';

next_state<=st2;

whenst2=>F<="0010";

COUT<='0';

next_state<=st3;

whenst3=>F<="0011";

COUT<='0';

next_state<=st4;

whenst4=>F<="0100";

COUT<='0';

next_state<=st5;

whenst5=>F<="0101";

COUT<='0';

next_state<=st6;

whenst6=>F<="0110";

COUT<='0';

next_state<=st7;

whenst7=>F<="0111";

COUT<='0';

next_state<=st8;

whenst8=>F<="1000";

COUT<='0';

next_state<=st9;

whenst9=>F<="1001";

COUT<='1';

next_state<=st0;

endcase;

endprocess;

D<=F(3);//把F信号输出到输出端

C<=F

(2);

B<=F

(1);

A<=F(0);

endBCD_arch

3时序仿真结果

4时序分析

================================================================================

Timingconstraint:

Defaultperiodanalysis

91itemsanalyzed,0timingerrorsdetected.

Minimumperiodis4.878ns.

Maximumdelayis12.324ns.

================================================================================

Timingconstraint:

Defaultnetenumeration

33itemsanalyzed,0timingerrorsdetected.

Maximumnetdelayis2.540ns.

--------------------------------------------------------------------------------

3设计一个8位的左右移位寄存器电路,输入为时钟信号CLK,方向控制信号D,

输出信号为每个寄存器的状态

1顶层原理图及说明

CLK为时钟信号,D为方向控制信号,R为复位信号,S0-S9为状态输出

2每个宏单元如何实现

libraryIEEE;

useIEEE.std_logic_1164.all;

entitydisplaceis

port(//输入输出初始化

D:

inSTD_LOGIC;

R:

inSTD_LOGIC;

CLK:

inSTD_LOGIC;

S:

outSTD_LOGIC_VECTOR(7downto0)

);

enddisplace;

architecturedisplace_archofdisplaceis

typeStateTypeis(st0,st1,st2,st3,st4,st5,st6,st7);//共有8个状态,非别对应8个移位输出

signalpresent_state,next_state:

StateType;

begin

process(CLK)

begin

if(CLK'eventandCLK='1')then//时钟信号上升沿触发

ifR='1'then//复位信号

present_state<=