8位数码管动态显示的频率计Word文档格式.docx

《8位数码管动态显示的频率计Word文档格式.docx》由会员分享,可在线阅读,更多相关《8位数码管动态显示的频率计Word文档格式.docx(16页珍藏版)》请在冰豆网上搜索。

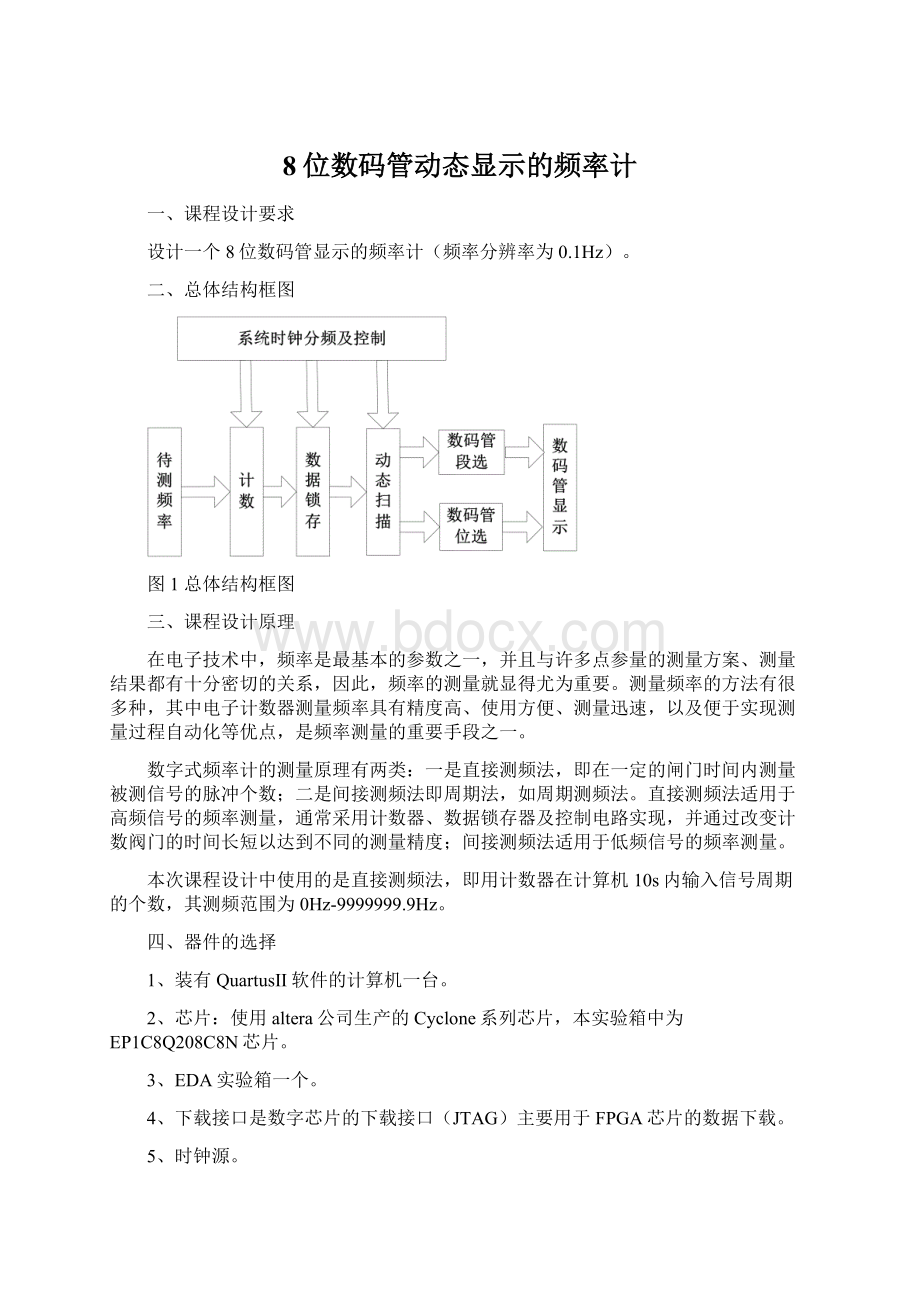

源程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYFPKZIS

PORT(CLK:

INSTD_LOGIC;

TSTEN:

OUTSTD_LOGIC;

CLR_CNT:

LOAD:

CLOCK:

OUTSTD_LOGIC);

ENDFPKZ;

ARCHITECTUREBEHAVOFFPKZIS

SIGNALCOUNT1:

INTEGERRANGE0TO20000;

SIGNALCOUNT2:

SIGNALCLK_DATA1:

STD_LOGIC;

SIGNALCLK_DATA2:

SIGNALDIV2CLK:

STD_LOGIC;

BEGIN

PROCESS(CLK)

BEGIN

IFCLK'

EVENTANDCLK='

1'

THEN

IFCOUNT1=10000THEN

COUNT1<

=0;

CLK_DATA1<

=NOTCLK_DATA1;

ELSECOUNT1<

=COUNT1+1;

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(CLK_DATA1)

IFCLK_DATA1'

EVENTANDCLK_DATA1='

IFCOUNT2=500THEN

COUNT2<

CLK_DATA2<

=NOTCLK_DATA2;

ELSECOUNT2<

=COUNT2+1;

PROCESS(CLK_DATA2)

IF(CLK_DATA2'

EVENTANDCLK_DATA2='

)THEN

DIV2CLK<

=NOTDIV2CLK;

PROCESS(CLK_DATA2,DIV2CLK)

IF(CLK_DATA2='

0'

ANDDIV2CLK='

)THEN

CLR_CNT<

='

;

ELSE

CLOCK<

=CLK_DATA2;

LOAD<

TSTEN<

=DIV2CLK;

ENDBEHAV;

(2)十进制计数器的功能模块图及其源程序

图4功能模块图

当使能端为高电平,清零端为低电平时,实现十进制计数功能。

第一个CNT10计数输出CQ=9时,下一秒时钟上升沿到来时,将产生一个CARRY_OUT信号作为下一个CNT10的时钟信号,同时CQ清零,依次递推到8个CNT10。

当清零端为低电平,使能端为低电平时停止计数。

当清零端为高电平时,计数器清零。

图5仿真波形图

ENTITYCNT10IS

INSTD_LOGIC;

CLR:

ENA:

CQ:

OUTINTEGERRANGE0TO9;

CARRY_OUT:

OUTSTD_LOGIC);

ENDCNT10;

ARCHITECTUREbehavOFCNT10IS

SIGNALCQI:

INTEGERRANGE0TO9;

PROCESS(CLR,CLK,ENA)

IF(CLR='

CQI<

ELSIF(CLK'

IF(ENA='

IF(CQI=9)THEN

CQI<

CARRY_OUT<

ELSE

=CQI+1;

CQ<

=CQI;

ENDbehav;

(3)32位锁存器的功能模块图及其源程序

图6功能模块图

实现方式:

LOAD信号上升沿到来时将对输入到内部的CNT10计数信号进行锁存。

锁存信号,并将结果输出给SELTIME。

图7仿真波形图

ENTITYREG32BIS

PORT(

LOAD:

DIN:

INSTD_LOGIC_VECTOR(31DOWNTO0);

DOUT:

OUTSTD_LOGIC_VECTOR(31DOWNTO0));

ENDENTITYREG32B;

ARCHITECTUREbehavOFREG32BIS

PROCESS(LOAD,DIN)IS

IFLOAD'

EVENTANDLOAD='

THENDOUT<

=DIN;

ENDARCHITECTUREbehav;

(4)数码管扫描的功能模块图及其源程序

图8功能模块图

锁存信号输出DIN[31..0],然后由SELTIME进行扫描输出,当SEL为”000”时选通第一个CNT10,输出到LED7进行译码输出。

依次类推。

图9仿真波形图

ENTITYSELTIMEIS

PORT(

CLK:

DIN:

DAOUT:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

SEL:

OUTSTD_LOGIC_VECTOR(2DOWNTO0));

ENDSELTIME;

ARCHITECTUREbehavOFSELTIMEIS

SIGNALSEC:

STD_LOGIC_VECTOR(2DOWNTO0);

IF(CLK'

IF(SEC="

111"

SEC<

="

000"

ELSE

=SEC+1;

PROCESS(SEC,DIN(31DOWNTO0))

CASESECIS

WHEN"

=>

DAOUT<

=DIN(3DOWNTO0);

001"

=DIN(7DOWNTO4);

010"

=DIN(11DOWNTO8);

011"

=DIN(15DOWNTO12);

100"

=DIN(19DOWNTO16);

101"

=DIN(23DOWNTO20);

110"

=DIN(27DOWNTO24);

=DIN(31DOWNTO28);

WHENOTHERS=>

NULL;

ENDCASE;

SEL<

=SEC;

(5)七段数码管译码显示的功能模块图及其源程序

图10功能模块图

将实验结果使用数码管直观的显示出来。

图11仿真波形图

ENTITYLED7IS

PORT(DIN:

INSTD_LOGIC_VECTOR(3DOWNTO0);

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDLED7;

ARCHITECTUREbehavOFLED7IS

--SIGNALLED7:

STD_LOGIC_VECTOR(6DOWNTO0);

PROCESS(DIN)

CASEDINIS

0000"

DOUT<

0111111"

0001"

0000110"

0010"

1011011"

0011"

1001111"

0100"

1100110"

0101"

1101101"

0110"

1111101"

0111"

0000111"

1000"

1111111"

1001"

1101111"

1010"

1110111"

1011"

1111100"

1100"

0111001"

1101"

1011110"

1110"

1111001"

1111"

1110001"

(6)3-8译码器的功能模块图及其源程序

图12功能模块图

利用3-8译码器将数码管的位选信号选通。

图13仿真波形图

ENTITYLS138IS

PORT(Q:

INSTD_LOGIC_VECTOR(2DOWNTO0);

D:

OUTSTD_LOGIC_VECTOR(7DOWNTO0));

ENDLS138;

ARCHITECTUREbehavOFLS138IS

WITHQSELECT

D<

00000001"

WHEN"

"

00000010"

00000100"

00001000"

00010000"

00100000"

01000000"

10000000"

wHEN"

11111111"

WHENOTHERS;

WITHQSELECT

dp<

'

6、顶层模块图

图14总体设计顶层模块图

其中8个十进制计数器模块JSQ的底层模块图如图15所示:

图15计数器模块原理图

本次课程设计的时钟信号由试验箱上面的20MHz的晶振提供,经过系统时钟和控制模块后分别产生0.05Hz和1kHz的脉冲信号0.05Hz的脉冲信号十进制计数器的使能信号,使计数器统计出待测信号在10s脉宽之间的脉冲数目。

再由计数模块将测得的信号传送给数码管显示部分,通过译码模块产生可以在数码管上显示的BCD码。

而1kHz是作为数码管动态扫描的频率,由于人的视觉暂留现象,频率较高时,数码管看起来就是连续发光。

本设计中使个位显示为数码管的小数点后面一位,由此实现了频率分辨率为0.1Hz的频率计设计。

七、实际电路测试

在quartus中将总体项目工程做好后,进行引脚分配和下载。

下载成功后,改变输入信号进行测试,测试结果如下:

(1)当输入信号为10.5Hz时,数码管显示10.5Hz

图16输入为10.5Hz

(2)当输入信号为10.5Hz时,数码管显示10.5Hz

图17输入为100.4Hz

(3)当输入信号为888.8Hz时,数码管显示888.8Hz

图18输入为888.8Hz

结论

EDA技术是电子设计的发展趋势,利用EDA工具可以代替设计者完成电子系统设计中的大部分工作。

EDA工具从数字系统设计的单一领域,发展到今天,应用范围己涉及模拟、微波等多个领域,可以实现各个领域电子系统设计的测试、设计仿真和布局布线等,这些都是我在这次课设中深刻体会到的。

经过这次课程设计,让我真正认识了EDA这门学科,了解到这种方式下的设计方案,硬件电路简洁,集成度高,体现了当今社会所需的先进技术,日后必定在有着广阔的发展空间。

通过这次对EDA课程设计的进一步操作,能更好的在QuartusII上进行VHDL程序的编译及各个模块的仿真,虽然在实际操作过程中由于粗心造成了程序的缺失和错误,但都在老师和同学的帮助下一一解决了。

很好地巩固了我们学过的专业知识,使我对数字系统结构也有了更进一步的了解和认识,同时对数据库软件EDA技术、VHDL等系列知识都有了一定的了解。

使用EDA技术开发页面的能力也有了很大提高,也使我们把理论与实践从真正意义上相结合了起来;

考验了我们借助互联网络搜集、查阅相关文献资料,和组织材料的综合能力。

在这次课程设计中,虽然应用的都是在书本上学过的知识,但是只有应用到实际中才算真正的学懂了这些知识。

本次数字频率计的涉及到了VHDL语言、QuartusII软件,EDA技术等。

涉及了微机原理和EDA所学的大部分内容。

通过这次课程设计实践巩固了学过的知识并能够较好的利用。

课程设计实践不单是将所学的知识应用于实际,在设计的过程中,只拥有理论知识是不够的。

逻辑思维、电路设计的步骤和方法、考虑问题的思路和角度等也是很重要,需要我们着重注意锻炼的能力。

在这次设计中还发现理论与实际常常常存在很大差距,为了使电路正常工作,必须灵活运用原理找出解决方法。

在课题设计中,通过使用QuartusII这个完全集成化、易学易用的可编程逻辑设计环境,利用VHDL语言设计完成八位十进制数字频率计,能够较好的测定所给频率,并且具有自动清零和自动测试的功能,基本符合此次课程设计给出的要求。

致谢

经过这几周的实际操作,使我提高了很多只有在实际操作中遇到的问题并解决问题的能力,虽然过程比较累,有时也心烦意乱,但是经过周围同学与老师的帮助指导与帮助,最终顺利的完成了此次课程设计。

在此,我要向在百忙之中抽时间对本课程设计进行审阅的老师表示感谢,同时,也要感谢本次设计同组的同学,不仅使我完成了实验,还从中学到了许多宝贵的知识,增长了我计算机方面的技能。

感谢他在我遇到困难时的热情帮助,在课程设计中,我们积极的交流与探讨也使我受益非浅,希望在以后的学习道路中我们能够共同进步。

在此我谨向我的老师以及在课程设计过程中给予我很大帮助的同学们致以最诚挚的谢意。