算法流程图和ASM图Word格式文档下载.docx

《算法流程图和ASM图Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《算法流程图和ASM图Word格式文档下载.docx(16页珍藏版)》请在冰豆网上搜索。

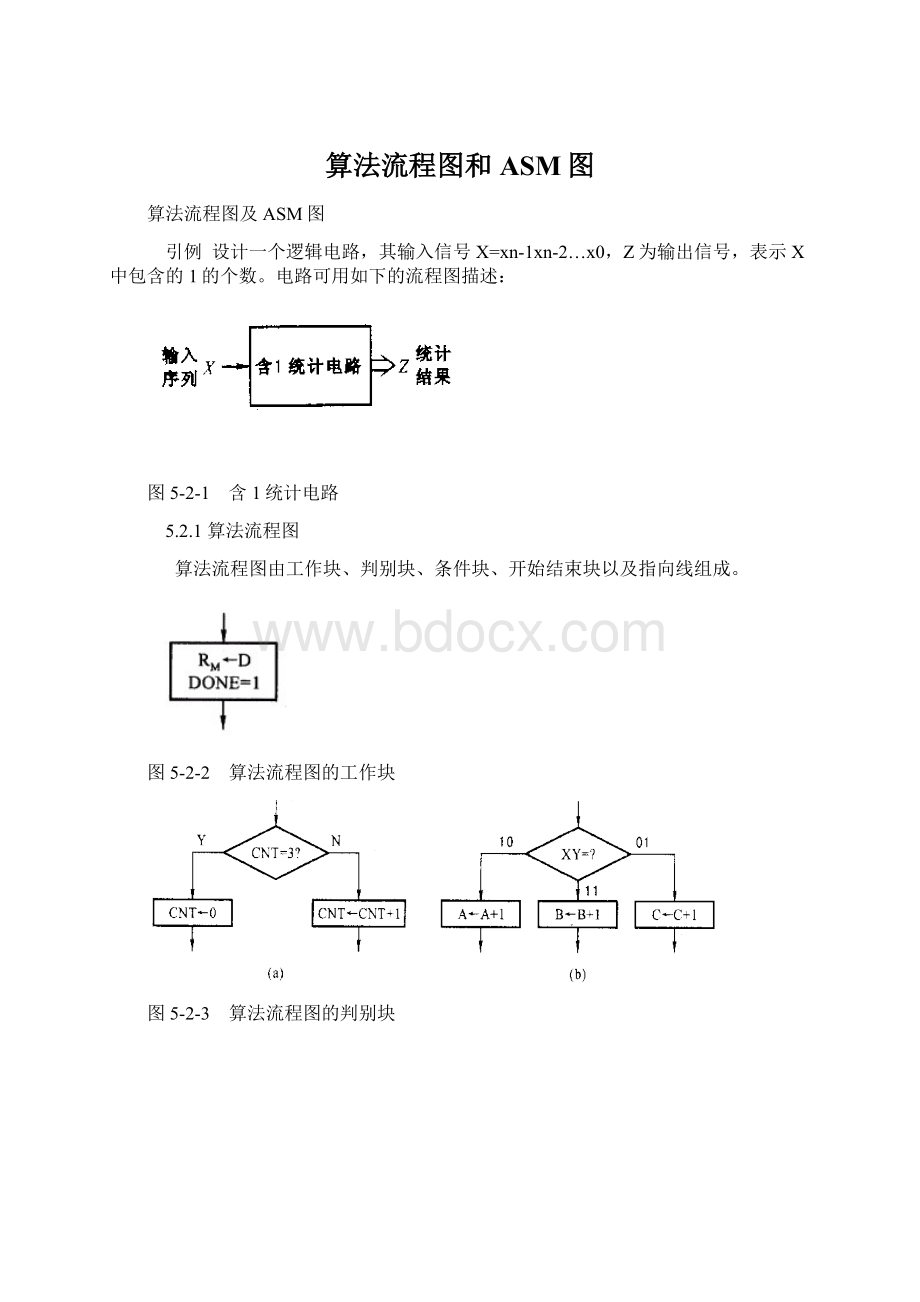

图5-2-6

含1统计电路的算法流程图

5.2.2算法设计

例5-2-1

设计如下左图所示的乘法电路。

图中,输入信号A=A4A3A2A1是被乘数,B=B4B3B2B1是乘数,且均为4位二进制数,P=A*B是输出信号,为8位二进制数。

START为启动信号,END为结束标志。

其算法逻辑图见下右图。

图5-2-7

乘法器的算法流程图

例5-2-2

设计一个电路,用于计算平面上两点之间的距离。

该电路输入信号为两个8位二进制数X和Y,分别代表两点横坐标的差值和纵坐标的差值,电路输出为Z,表示两点之间的距离。

计算误差要求小于10%。

图5-2-8

例5-2-2的算法流程图

5.2.3电路划分与逻辑框图

例5-2-3

根据含1统计电路的算法流程图,画出电路的逻辑框图。

如下。

图5-2-9

含1统计电路的逻辑框图

例5-2-4

画出4位二进制乘法器的逻辑框图。

图5-2-10

乘法器的逻辑框图

例5-2-5

根据距离运算电路的算法流程图,画出该电路的逻辑框图。

图5-2-11

距离运算电路的逻辑框图

5.2.4数据处理单元的设计

例5-2-6

设计含1统计电路的数据处理单元。

如图。

图5-2-12

含1统计电路的数据处理单元

例5-2-7

设计4位乘法器的数据处理单元。

图5-2-13

4位乘法器的数据处理单元

5.2.5ASM图

5.2.5.1ASM图的基本符号和组成

图5-2-14

ASM图的状态图

图5-2-15

ASM图的判别块

图5-2-16

ASM图的条件输出块

5.2.5.2导出ASM图的方法

ASM图和算法流程图间的相互关系和转换规则十分明确,两者之间工作块(状态块)、判别块、条件输出块基本对应。

例5-2-8

将含1统计电路的算法流程图转换成为ASM图。

如下图。

图5-2-18

含1统计电路控制器ASM图

例5-2-9

将4位乘法器的算法流程图转换为ASM图。

图5-2-19

乘法器控制单元ASM图

5.2.6控制单元的设计

5.2.6.1以触发器为核心的控制器设计

例5-2-10

导出上图所示的乘法控制单元的逻辑电路。

1.对ASM图进行状态分配:

S0——00,S1——01,S2——11,S3——10

图5-2-20

乘法器控制单元设计过程之一

2.填写激励函数卡诺图

3.导出输出方程

END=Q1Q0

CR

=

Q1Q0

CA=

Q1Q0

CB1=

CB0=Q1Q0+

CC=

CM1=

Q1Q0Bi

CM0=

Q1Q0Bi+Q1Q0

4.画逻辑图:

图5-2-21

乘法器控制单元逻辑电路之一

5.2.6.2以集成计数器为核心的控制器设计

例5-2-11

用集成计数器74163,辅以适当的组合器件,设计乘法器控制单元电路。

1.状态分配:

图5-2-22

乘法控制器单元设计过程之二

2.列操作表

3.填写激励函数卡诺图

4.导出输出方程

CA=CB1=Q1Q0

Q1Q0=Q0

5.画逻辑图:

图5-2-23

乘法器控制单元逻辑电路之二

5.2.6.3以集成移位器为核心的控制器设计

例5-2-12

用集成移位器74194,辅以适当的组合器件,设计乘法器控制单元的电路。

进行状态分配:

S0——00,S1——01,S2——11,S3——10,得操作表及各激励输入端的函数卡诺图,如图5-2-24。

图5-2-24

乘法器控制单元逻辑电路之三

各输出信号的函数表达式为:

END=QAQB

QAQB

CA=CB1=QAQB

CB0=QAQB+

QAQB

QAQBBi

QAQBBi+QAQB

激励函数M1、M0用双4选1MUX实现,各输出信号仍用译码器辅以少量门电路加以实现,其逻辑电路如图5-2-25所示。

图5-2-25

5.2.6.4以集成多D触发器为核心的控制器设计

例5-2-13

用四D触发器74175,辅以适当的组合器件,设计乘法器控制单元电路。

用多D触发器设计时序电路时,状态分配采用“一对一”的方法。

所以进行状态分配如下:

S0——0000,S1——1100,S2——1010,S3——1001。

由ASM图列出次态表,如表5-2-3所示。

表5-2-3

次态表

由ASM图可直接写出各输出方程

END=Q0

CR=Q1

CA=CB1=Q1

CC=Q2

CB0=Q1+Q3

CM1=Q2Bi

CM0=Q2Bi+Q3

控制单元的逻辑框图如图5-2-26所示。

图5-2-26

乘法器控制单元逻辑电路之四

5.2.7设计举例

图5-2-27给出了FIFO(先进先出,又称为队列)的顺序存储器的示意图和待设计FIFO的框图。

图5-2-27

FIFO存储器示意图

图5-2-28给出了队列在RAM中可能的几种分布位置。

图中阴影代表队列已占据的存储空间,空白表示未被占据的存储空间。

图5-2-28

队列在RAM中的几种位置分布

图5-2-29(a)给出了读操作的示意图。

读操作时,WA不变,RA加1。

显然,若RA加1后与WA相等,则表示队列已空。

图5-2-29(b)、(c)给出了写操作的示意图。

写操作时,RA不变,WA加1。

若WA加1后与RA相等,则表示队列已满。

图5-2-29

FIFO的读/写操作

在分析FIFO逻辑功能及读写操作特点的基础上,现进行电路设计。

1、算法设计与逻辑框图

该FIFO的算法流程图如图5-2-30所示。

图5-2-30

FIFO的算法流程图

实现上述算法逻辑框图如图5-2-31所示。

图5-2-31

FIFO的逻辑框图

2、数据处理单元的设计

图5-2-32为数据处理单元的逻辑图。

图5-2-32

FIFO的数据处理单元

3、导出ASM图

根据算法流程图和数据处理单元的逻辑图,可导出控制器的ASM图,如图5-2-33所示。

图5-2-33

FIFO控制器的ASM图

4、控制器的设计

对ASM图进行如下状态分配:

S0——00,S1——01,S2——10,S3——11

如图5-2-34(a)所示。

选择D触发器作为控制器的状态寄存器。

由ASM图可直接导出激励函数卡诺图,如图5-2-34(b)所示。

图5-2-34

状态分配及卡诺图

可画出控制器的逻辑电路,如图5-2-35所示。

图5-2-35

FIFO控制器的逻辑图