计数器文档格式.docx

《计数器文档格式.docx》由会员分享,可在线阅读,更多相关《计数器文档格式.docx(17页珍藏版)》请在冰豆网上搜索。

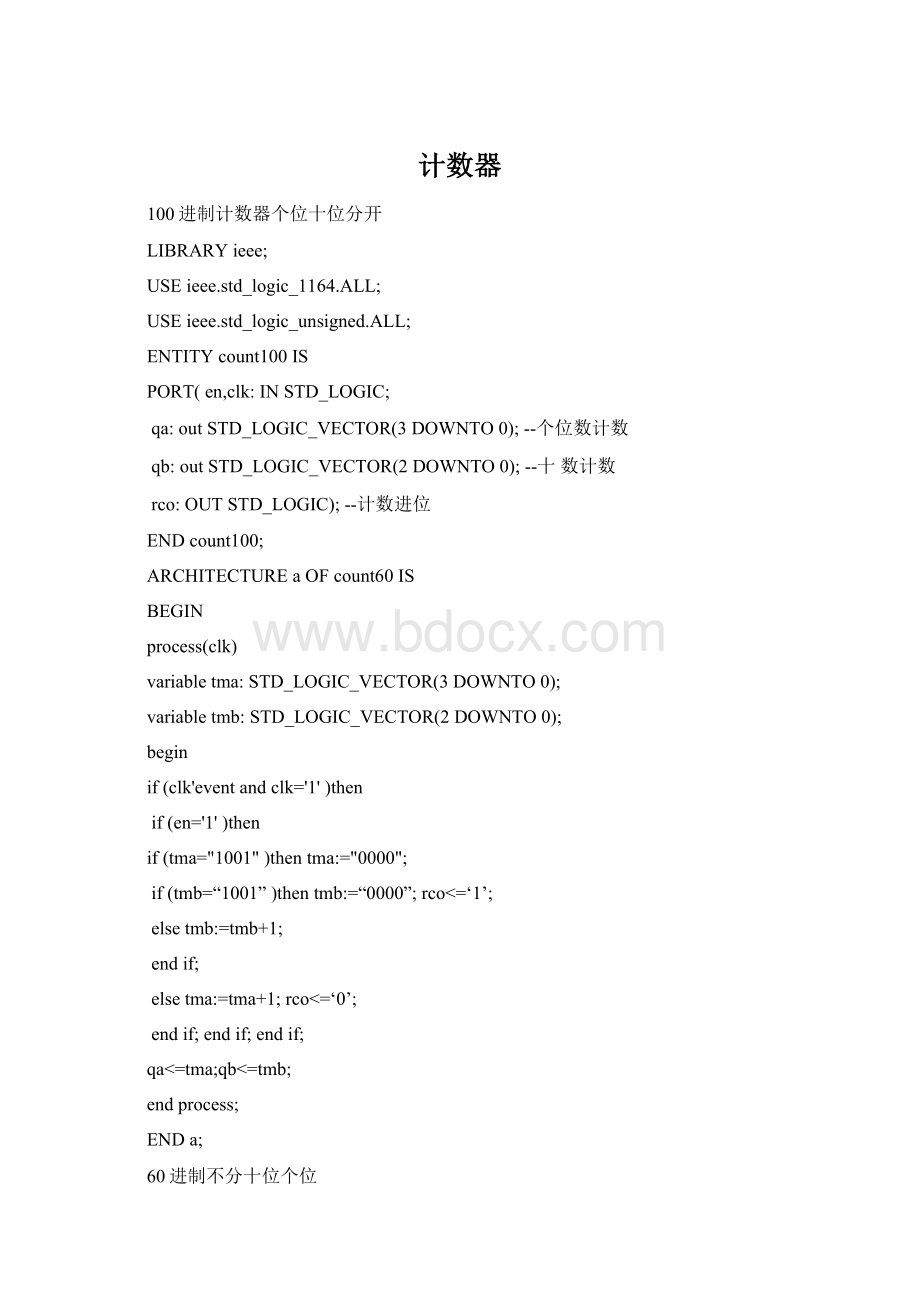

)then

if(en='

if(tma="

1001"

)thentma:

="

0000"

;

if(tmb=“1001”)thentmb:

=“0000”;

rco<

=‘1’;

elsetmb:

=tmb+1;

endif;

elsetma:

=tma+1;

=‘0’;

qa<

=tma;

qb<

=tmb;

endprocess;

ENDa;

60进制不分十位个位

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitylsyis

port(clk:

instd_logic;

cq:

outstd_logic_vector(7downto0);

cout:

outstd_logic);

endlsy;

architecturezhangoflsyis

begin

process(clk)

variablecqi:

std_logic_vector(7downto0);

ifclk'

then

ifcqi<

59thencqi:

=cqi+1;

elsecqi:

=(others=>

'

0'

);

endif;

ifcqi=59thencout<

='

elsecout<

cq<

=cqi;

endzhang;

分频器50占空比1:

1

ENTITYcountIS

PORT(clk:

inSTD_LOGIC;

clkout:

bufferSTD_LOGIC;

ENDcount;

ARCHITECTUREaOFcountIS

Signalcount:

STD_LOGIC_vector(21downto0);

PROCESS(clk)

IF(clk'

EVENTANDclk=‘1’)THEN

IF(count=“11001"

)

THENcount=“00000”;

clkout<

=notclkout;

ELSE

count=count+1;

ENDIF;

ENDPROCESS;

使用vhdl语言设计程序,能够实现计算输入信号中1的个数。

输入信号data为八位信号,输出y为三位信号,要求该程序能够计算出八位信号的八位中有几位信号是1

libraryieee;

entitydatais

port(data:

instd_logic_vector(7downto0);

y:

outstd_logic_vector(2downto0));

enddata;

architectureloopofdatais

p1:

process(data)

variabletmp:

std_logic_vector(2downto0);

tmp:

000"

foriin0to7loop

ifdata(i)='

then

=tmp+'

endloop;

y<

=tmp;

endprocessp1;

设计一个D触发器,输入信号为时钟clk,数据D[3:

0],复位端rst,输出为Q[3:

0],要求分别设计同步复位D触发器和异步复位D触发器

entitydffis

port(clk,d,clr:

q:

enddff;

architecturedff2ofdffis

process(clk,clr)

begin

if(clr='

)then

q<

elsif(clkeventandclk='

=d;

enddff2;

if(clk'

eventandclk='

else

endprocess;

下列程序是使用条件信号赋值语句设计的异或门,请使用ifelse语句改写该程序。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYxor_gateIS

PORT(a,b:

instd_logic;

c:

outstd_logic);

endxor_gate;

ARCHITECTUREdata_flowOFxor_gateIS

C<

='

WHENa='

ANDb='

ELSE

'

ENDdata_flow;

改:

if(a='

c<

)then

下列程序是使用case语句设计的数据选择器,请使用withselect选择信号带入语句改写该程序。

entitymuxis

port(d0,d1,d2,d3,a0,a1:

y:

endmux;

architecturebehavofmuxis

signala:

std_logic_vector(1downto0);

process(a0,a1,d0,d1,d2,d3)

a<

=a1&

a0;

caseais

when"

00"

=>

=d0;

01"

=d1;

10"

=d2;

11"

=d3;

whenothers=>

Z'

endcase;

endbehav;

withaselect

y<

=d0when"

d1when"

d2when"

d3when"

whenothers;

数据检测

对串行数据进行检测,连续输入3个或者3个以上的1时输出为1,其他输入情况下输出为0)

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

entitychuanxingjianceis

port(clk,x:

endchuanxingjiance;

architectureoneofchuanxingjianceis

typestate_typeis(s0,s1,s2,s3);

signalp,n:

state_type;

then

p<

=n;

process(x,p)

casepis

whens0=>

ifx='

thenn<

=s1;

elsen<

=s0;

whens1=>

=s2;

whens2=>

=s3;

whens3=>

whenothers=>

null;

endone;

FLASHMemory存储的数据是非易失的(不容易丢失)。

对

熔丝型结构的PROM数据写好后,可以再次修改数据

错

EEPROM是用紫外线照射进行数据擦除

所选答案:

正确答案:

EEPROM需要用20~25V的大电压进行数据写入

EEPROM可以逐字擦除逐字写入数据。

FLASHMemory可以逐字擦除逐字写入数据。

下列哪个存储器的数据掉电后会丢失。

RAM

FPGA中文含义是什么?

现场可编程门阵列

生产第一块FPGA芯片的公司是下列哪家公司?

Xilinx

以下哪个工具是Xilinx公司的可编程逻辑器件设计工具?

ISE

下列哪个语言是IEEE标准的硬件描述语言

VHDL

一个VHDL语言可以含有多个实体

buffer既能用于输出,也能用于反馈

out既能用于输出,也能用于反馈

inout既能用于输出,也能用于反馈

Bit数据类型含有几个值?

B.2

字符不区分大小写

以下哪种数据类型不是VHDL语言可以直接使用的数据类型

D.Std_logic

Std_Logic数据类型含有几个值?

A.9

下列哪个数据对象不一定代表着实际的物理结构?

C.变量

给信号再次赋值使用:

=

给变量再次赋值使用:

给常量再次赋值使用<

变量只能出现在进程和子程序中

可以在结构体里面进行变量的定义

A:

=“10110001”;

ASLL2的值是多少?

11000100

ASRL2的值是多少?

00101100

AROL2的值是多少?

11000110

B:

=“01011101”;

AANDB等于什么?

00010001

AORB等于什么?

11111101

AXORB等于什么?

C:

=“1110”;

A&

C[2]&

B[0]等于什么?

1011000111

下列哪个是合法的标识符

C.addr_3

VHDL程序包含哪五个部分

实体结构体配置包集合库