CMOS反相器版图设计与仿真报告文档格式.docx

《CMOS反相器版图设计与仿真报告文档格式.docx》由会员分享,可在线阅读,更多相关《CMOS反相器版图设计与仿真报告文档格式.docx(15页珍藏版)》请在冰豆网上搜索。

而在本例中则在L-Edit文件夹中新建立“反相器版图”文件夹,并将新文件以文件名“Ex11”存与此文件夹中。

如图一所示。

图一打开L-Edit,并另存文件为Ex11

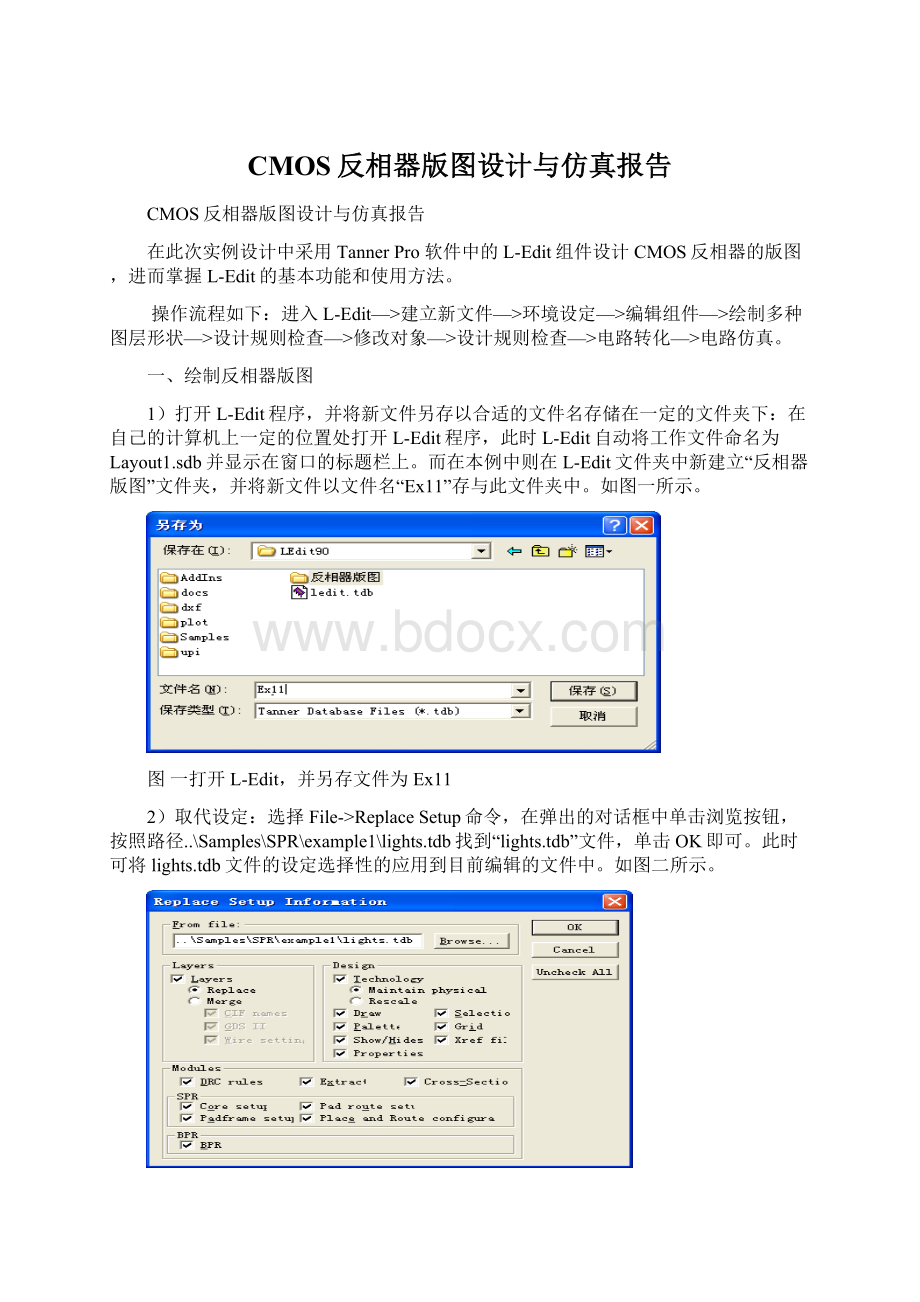

2)取代设定:

选择File->

ReplaceSetup命令,在弹出的对话框中单击浏览按钮,按照路径..\Samples\SPR\example1\lights.tdb找到“lights.tdb”文件,单击OK即可。

此时可将lights.tdb文件的设定选择性的应用到目前编辑的文件中。

如图二所示。

图二取代设定

3)编辑组件:

L-Edit编辑方式是以组件(Cell)为单位而不是以文件为单位,一个文件中可以包含多个组件,而每一个组件则表示一种说明或者一种电路版图。

每次打开一个新文件时便自动打开一个组件并命名为“Cell0”;

也可以重命名组件名。

方法是选择Cell->

Rename命令,在弹出的对话框中的Renamecellas文本框中输入符合实际电路的名称,如本设计中采用组件名“inv”即可,之后单击OK按钮。

如图三所示。

图三重命名组件为inv

4)设计环境设定:

绘制布局图必须要有确实的大小,因此要绘图前先要确认或设定坐标与实际长度的关系。

选择Setup->

Design命令,打开SetDesign对话框,在Technology选项卡中出现使用技术的名称、单位与设定。

本设计中的技术单位是Lambda。

而Lambda单位与内部单位InternalUnit的关系可在TechnologySetup选项组中设定。

此次设计设定1个Lambda为1000个InternalUnit,也设定1个Lambda等于1个Micron。

如图四所示。

图四技术设定

接着选择Grid选项卡,其中包括使用格点显示设定、鼠标停格设定与坐标单位设定。

此次设计设定1个显示的格点等于1个坐标单元,设定当格点距离小于8个像素时不显示;

设定鼠标光标显示为Smooth类型,设定鼠标锁定的格点为0.5个坐标单位;

设定1个坐标单位为1000个内部单位。

如图五所示。

图五格点设定

设定结果为1个格点距离等于1个坐标单位,也等于1个Micron。

5)编辑PMOS组件:

按照NWell层、PSelect层、Active层、Ploy层、Mental1层、Activecontact层的流程编辑PMOS组件。

其中,NWell层宽为24个格点、高为15个格点,PSelect层宽为18个格点、高为10个格点,Active层宽为14个格点、高为5个格点,Ploy层宽为2个格点、高为20个格点,Mental1层宽为4个格点、高为4个格点,Activecontact层宽为2个格点、高为2个格点。

在设计各个图层时,一定要配合设计规则检查(DRC),参照设计规则反复修改对象。

这样才可以高效的设计出符合规则的版图。

PMOS组件的编辑结果如图六所示。

图六PMOS组件结果图

利用L-Edit观察截面的功能来观察该布局图设计出的组件的制作流程与结果。

单击命令行上的Cross-Selection按钮打开GenerateCross-Section对话框,在Processdefinitionfile文本框中输入..\Samples\SPR\example1\lights.xst文件;

之后单击Pick按钮,在编辑画面选则要观察的位置,再单击OK即可。

如图七所示。

图七观看各图层的生长顺序

6)新建NMOS组件:

选择Cell->

New命令.打开CreateNewCell对话框,在其中的Cellname文本框中输入组件名“noms”,单击确定按钮即可。

如图八所示。

图八新建nmos组件

7)编辑NMOS组件:

按照NSelect层、Active层、Ploy层、Mental1层、Activecontact层的流程编辑NMOS组件。

其中,NSelect层宽为18个格点、高为9个格点,Active层宽为14个格点、高为5个格点,Ploy层宽为2个格点、高为9个格点,Mental1层宽为4个格点、高为4个格点,Activecontact层宽为2个格点、高为2个格点。

NMOS组件的编辑结果如图九所示。

图九nmos组件版图

同样,利用L-Edit观察截面的功能来观察该布局图设计出的组件的制作流程与结果。

结果如图十所示。

图十NMOS制作流程

8)新增并编辑PMOS基板节点组件Basecontactp:

按照NWell层、NSelect层、Active层、Mental1层、Activecontact层的流程编辑PMOS基板节点组件。

其中,NWell层宽为15个格点、高为15个格点,NSelect层宽为9个格点、高为9个格点,Active层宽为5个格点、高为5个格点,Mental1层宽为4个格点、高为4个格点,Activecontact层宽为2个格点、高为2个格点。

PMOS基板节点组件的编辑结果如图十一所示。

图十一PMOS基板组件

利用L-Edit观察截面的功能来观察该布局图设计出的组件的制作流程与结果。

结果如图十二所示。

图十二PMOS基板组件制作流程

9)新增并编辑NMOS基板接触点组件Basecontactn:

按照PSelect层、Active层、Mental1层、Activecontact层的流程编辑NMOS基板接触点组件。

其中,PSelect层宽为9个格点、高为9个格点,Active层宽为5个格点、高为5个格点,Mental1层宽为4个格点、高为4个格点,Activecontact层宽为2个格点、高为2个格点。

NMOS基板接触点组件的编辑结果如图十三所示。

图十三NMOS基板接触点

结果如图十四所示。

图十四NMOS基板接触点制作流程

10)引用Basecontactn、Basecontactp、nmos、pmos组件:

Instance命令,在弹出的对话框中选择Basecontactn组件,单击OK按钮即可。

用相同的方法可引用Basecontactp组件,pmos组件和nmos组件。

11)DRC检查:

引用后,将Basecontactn和Basecontactp组件分别放到nmos组件和pmos左边。

单击命令行的DRC按钮进行检查,结果如图十五所示。

由图可知,不违背设计规则。

图十五DRC检查

11)连接闸极Ploy和汲极Mental1:

由于反相器的pmos和nmos的闸极是连通的,故可以直接以Ploy图层将pmos与nmos的Ploy相连接;

而且它们的汲极也是连通的,故可以用Mental1相连接。

如图十六所示。

经DRC检查无错误。

图十六连接闸极和汲极

12)绘制电源线:

由于反相器需要有Vdd和GND电源,所以需要绘制以Mental1来表示的电源线,即利用Mental1在pmos上方与nmos下方各绘制一个宽为39个格点,高为3个格点的电源图样。

如图十七所示,经DRC检查无错误。

图十七绘制电源线

13)标注Vdd和GND节点,连接电源与接触点:

为了便于电源的区分与表示,可以采用标注节点的方法将上下两个电源区别开来,即在命令工具条中单击插入节点按钮,再回到编辑窗口在电源部分拖曳选中,之后在弹出的对话框的Portname文本框中输入节点名称。

为了使电源加载到反相器上,必须将电源和接触点连接。

此时可使用Mental1层金属,即分别将PMOS的左接触点与Basecontactp组件的接触点用Mental1层和Vdd电源相接,及将NMOS的左接触点与Basecontactn组件接触点用Mental1层和GND电源相接。

结果如图十八所示。

图十八标注节点,连线

14)加入输入节点:

由于反相器有一个输入端口,输入信号是从闸极输入,又由于此次设计的规则要求,输入信号必须由Mental2传入,故反相器输入端口需要绘制mental2层、Via层、Mental1层、PloyContact层和Poly层,才能将信号从Mental2层传至Poly层。

即在编辑窗口的空白处按照Poly层、Mental1层、Mental2层、PolyContact层、Via层的顺序绘制各个图层。

其中,Poly层宽为5个格点、高为5个格点,Mental1层宽为9.5个格点、高为4个格点,Mental1层宽为5个格点、高为5个格点,Mental2层宽为5个格点、高为5个格点,PolyContact层宽为2个格点、高为2个格点,Via层宽为2个格点、高为2个格点。

配合DRC检查无误后,可将此输入端口群组起来,即选中输入端口部分,再选择Draw->

Group命令,在弹出的对话框的GroupCellname中输入名字如“portA”,即可与当前文件中新增加一个portA组件。

组件portA的版图如图十九所示。

图十九输入端口版图

15)加入输出端口:

反相器有一个输出端口,输出信号从汲极输出,由于设计规则的限制,输出信号必须由Mental2输出,故输出端口要绘制Mental1层、Mental2层和Via层才能将信号输出,即按照Mental1层、Mental2层和Via层的顺序绘制个个图层,其中Mental1层、Mental2层宽高均为4个格点和Via层宽高均为2个格点。

同样的方法将输出端口群组为端口OUT。

结果如图二十所示。

图二十输出端口版图

加入输入输出端口后的最终的反相器版图及输入输出端口处的图层如图二十一所示。

图二十一最后版图设计展示

16)更改组件名称,并转化为Spice文件:

将反相器版图改名为inv,即选择Cell->

RenameCell命令,在弹出的对话框中的Renamecellas文本框的输入“inv”即可。

同时可使用菜单栏中Tools->

Extract选项可将版图转化为Spice文件。

如图二十二所示。

二、使用T-Spice进行版图设计仿真

1)打开T-Spice程序,打开反相器版图的Spice文件“inv.spc”并按照如下流程在Spice文件中插入命令:

加载包含文件->

Vdd电源电压值设定->

输入信号A设定->

分析设定->

输出设定->

进行模拟。

设定后在文件中加入如下命令行:

.include"

D:

\Tanner\tanner\TSpice70\models\ml2_125.md"

,vvddVddGND5,vaAGNDPULSE(0550n5n5n50n100n),.tran/op1n400nmethod=bdf,.printtranv(A)v(OUT)。

设定后的结果如图二十三所示。

图二十三T-Spice设定

2)单击仿真按钮进行仿真,自动弹出的仿真波形如下图二十四所示。

图二十四仿真波形图

有波形图可以知道,时间10ns~110ns的输入数据为1,输出数据为0。

同理,在时间120ns~200ns输入数据为0,输出数据为1。

总之,输入与输出反相,所以可知设计结果与理论分析一致,此次设计正确成功。

仿真数据报告如下图二十五所示。

图二十五仿真数据报告