第5章MOS集成电路的版图设计Word文档下载推荐.docx

《第5章MOS集成电路的版图设计Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《第5章MOS集成电路的版图设计Word文档下载推荐.docx(19页珍藏版)》请在冰豆网上搜索。

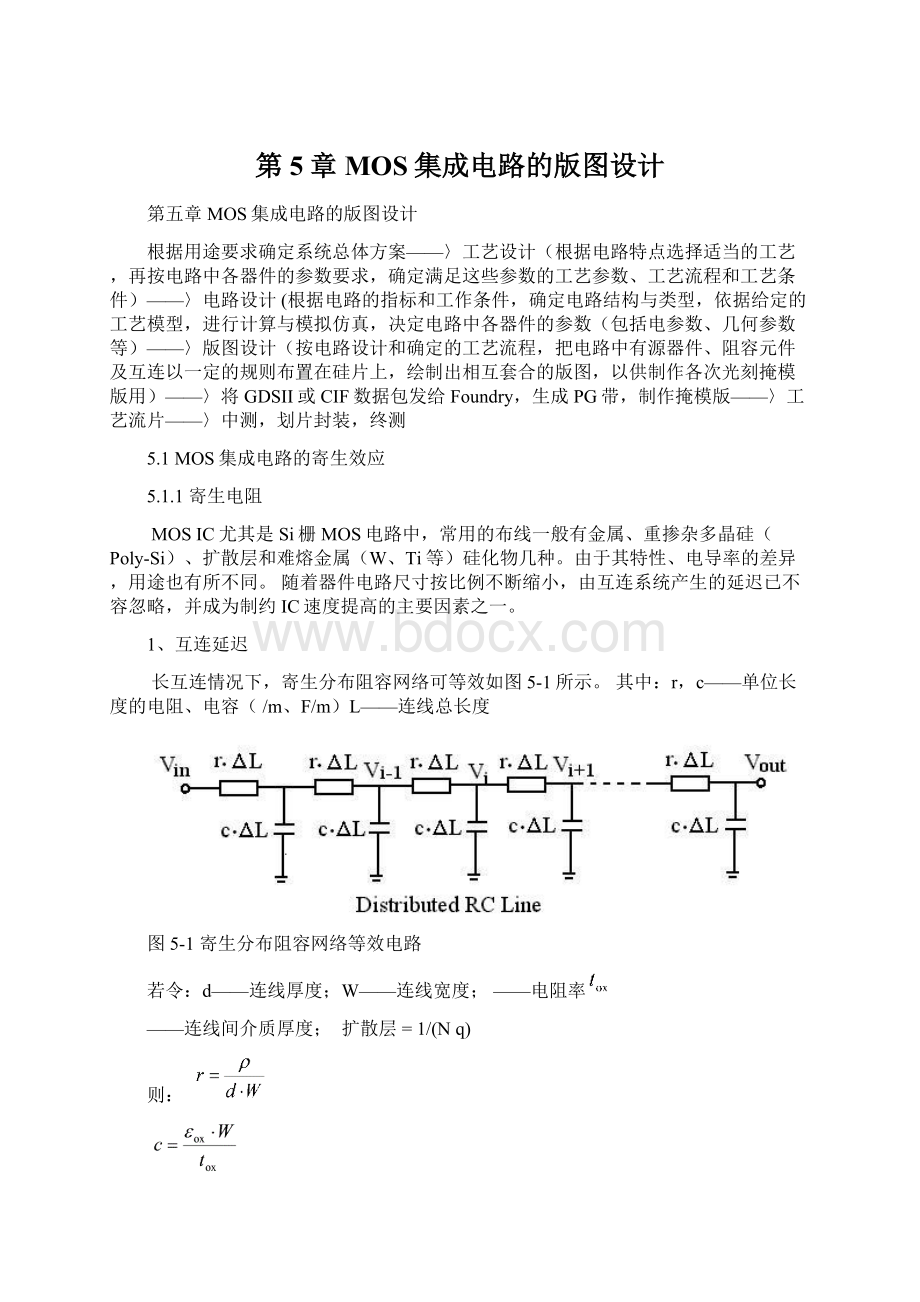

即将整个长连线等效为一总的R总、C总,则:

(5-6)

图5-2集总模型等效电路

可见,与分布网络分析情况差1/2的关系,而与实际测试相比,分布模型更为接近。

因此,在分析长互连延迟时应采用分布RC模型。

例5-1:

已知:

采用1m工艺,n+重掺杂多晶硅互连方块电阻R=15/,多晶硅与衬底间介质(SiO2)的厚度tox=6000Å

。

求:

互连长度为1mm时所产生的延迟。

解:

采用分布RC模型,得:

补充材料:

图5-3由边际电场效应产生的寄生电容

以上分析互连系统的电容时,仅考虑到互连与衬底间的电容,但实际上还有边际电场形成的电容Cff(FringingField)。

随着尺寸的不断缩小,Cff往往可与面积电容相比拟,不可忽略不计。

对于1mCMOS工艺,单位面积Cff如下表所示。

表5-1不同连线层与衬底间的Cff

Cff(fF/m2)

PolySi-Sub

0.0430.004

Metal1-Sub

0.0440.001

Metal2-Sub

0.0350.001

Metal3-Sub

0.0330.001

由此,可见上例中单位面积的边际电场效应电容为:

Cff=0.0432=0.086fF/m2

而单位面积的平板电容:

C平板=ox/tox=0.058fF/m2

Cff与C平板已在同一量级,不能忽略,需重新计算:

2、导电层的选择

选用导电层时应注意:

(1)VDD、VSS尽可能选用金属导电层,并适当增加连线宽度,只有在连线交叉“过桥”时,才考虑其它导电层。

(2)多晶硅不宜用作长连线,一般也不用于VDD、VSS电源布线。

(3)通常应使晶体管等效电阻远大于连线电阻,以避免出现电压的“分压”现象,影响电路正常工作。

(4)在信号高速传送和信号需在高阻连线上通过时,尤其要注意寄生电容的影响。

扩散层与衬底间电容较大,很难驱动;

在某些线路结构中还易引起电荷分享问题,因此,应使扩散连线尽可能短。

5.1.2寄生电容

MOS电路中,除了由互连系统造成的分布电容之外,还存在许多由于MOSFET结构特点所决定的寄生电容。

其中:

CMOS——单位面积栅电容=COX,是节点电容的主要组成部分

5m工艺,TOX=1000Å

,COX0.345fF/m2

1m工艺,TOX=200Å

,COX1.725fF/m2

CMNT——Al-栅氧-n+区之间的电容(CMOS)

CM——Al-场氧-衬底间的电容(CMOS/10)

CMN——Al-场氧-n+区之间的电容(23CM)

Cpn——D、S与衬底之间的pn结电容(Nsub,Cpn)

CGD对器件工作速度影响较大,可等效为输入端的一个密勒电容:

Cm=(1+KV)CGD,KV为电压放大系数。

5.1.3寄生沟道

图5-4寄生沟道形成示意图

由图5-4可见,当互连跨过场氧区时,如果互连电位足够高,可能使场区表面反型,形成寄生沟道,使本不应连通的有源区导通,造成工作电流泄漏,使器件电路性能变差,乃至失效。

预防措施:

(1)增厚场氧厚度t’OX,使V’TF,但需要增加场氧时间,对前部工序有影响,并将造成台阶陡峭,不利于布线。

(2)对场区进行同型注入,提高衬底浓度,使V’TF。

但注意注入剂量不宜过高,以防止某些寄生电容增大,以及击穿电压的下降。

(3)版图设计时,尽量把可能产生寄生MOS管的扩散区间距拉大,以使W/L,ron,但这样将使芯片面积,集成度。

5.1.4CMOS电路中的闩锁(Latch-up)效应

——闩锁效应为CMOS电路所独有,是由于CMOS结构中存在pnpn四层结构所形成的寄生可控硅造成的。

所以nmos或pmos电路中不会出现。

1、CMOS电路中寄生可控硅结构的形成

2、

图5-5CMOS反相器剖面图和寄生可控硅等效电路

由图5-5可见,由CMOS四层pnpn结构形成寄生可控硅结构。

(1)正常情况下,n-衬底与p-阱之间的pn结反偏,仅有极小的反向漏电流,T1、T2截止。

(2)当工作条件发生异常,VDD、VSS之间感生较大的衬底电流,在RS上产生较大压降。

当T1管EB结两端压降达到EB结阈值电压,T1导通,通过RW吸收电流。

当RW上压降足够大,T2导通,从而使VDD、VSS之间形成通路,并保持低阻。

当npnpnp>

1,则发生电流放大,T1、T2构成正反馈,形成闩琐,此时,即使外加电压撤除仍将继续保持,VDD、VSS间电流不断增加,最终导致IC烧毁。

(3)诱发寄生可控硅触发的三个因素:

T1、T2管的值乘积大于1,即npnpnp>

1。

T1、T2管EB结均为正向偏置。

电源提供的电流维持电流IH。

(4)诱发闩琐的外界条件:

射线瞬间照射,强电场感应,电源电压过冲,跳变电压,环境温度剧变,电源电压突然增大等。

2、防止闩琐的措施

A.版图设计和工艺上的防闩锁措施

使T1、T2的,npnpnp«

工艺上采取背面掺金,中子辐射电子辐照等降低少子寿命。

减少RS、RW使其远小于Ren、Rep。

版图中加保护环,伪集电极保护结构,内部区域与外围分割

增多电源、地接触孔的数目,加粗电源线、地线对电源、地接触孔进行合理布局,减小有害的电位梯度。

输入输出保护

采用重掺杂衬底上的外延层,阱下加p+埋层。

制备“逆向阱”结构。

采用深槽隔离技术。

B.器件外部的保护措施

电源并接稳压管。

低频时加限流电阻(使电源电流<

30mA)

尽量减小电流中的电容值。

(一般C<

0.01F)

3、注意事项:

输入电压不可超过VDDVSS范围。

输入信号一定要等VDDVSS电压稳定后才能加入;

关机应先

关信号源,再关电源。

不用的输入端不能悬浮,应按逻辑关系的需要接VDD或VSS

5.2MOS集成电路的工艺设计

5.2.1CMOSIC的主要工艺流程

1、Al栅CMOS工艺流程

衬底制备(n-Si,<

100>

晶向,[Na+]=1010cm-2,=36cm)一次氧化p-阱光刻MK1注入氧化p-阱B离子注入p-阱B再分布p+区光刻MK2B淀积p+硼再分布n+区光刻MK3磷淀积磷再分布PSG淀积增密(800100nm厚的SiO2,2.5%的P2O5)栅光刻MK4栅氧化P管调沟注入光刻MK5P管调沟硼注入N管调沟注入光刻MK6N管调沟磷注入注入退火引线孔光刻MK7蒸发Al(1.2m)反刻AlMK8Al-Si合金化长钝化层(含23%P2O5的PSG,800100nm)钝化孔光刻MK9前工序结束

2、多晶硅栅NMOS工艺流程

(1)衬底制备

典型厚度0.40.8mm,

=75125mm(3”5”)

NA=10151016cm-3

=252cm

(2)预氧化

在硅片表面生长一层厚SiO2,以

保护表面,阻挡掺杂物进入衬底。

(3)涂光刻胶

涂胶,甩胶,(几千转/分钟),

烘干(100℃)固胶。

(4)通过掩模版MASK对光刻胶曝光

(5)刻有源区。

掩模版掩蔽区域下未被曝光的光刻胶被显影液洗掉;

再将下面的SiO2用HF刻蚀掉,露出硅片表面。

(6)淀积多晶硅

除净曝光区残留的光刻胶(丙酮),在整个硅片上生长

一层高质量的SiO2(约1000Å

),即栅氧,然后再淀

积多晶硅(12m)。

(7)刻多晶硅,自对准扩散

用多晶硅版刻出多晶硅图形,再用有源区版刻掉

有源区上的氧化层,高温下以n型杂质对有源区

进行扩散(1000℃左右)。

此时耐高温的多晶硅和

下面的氧化层起掩蔽作用

——自对准工艺

(8)刻接触孔

在硅片上再生长一层SiO2,用接触孔版刻出接触孔。

(9)反刻Al

除去其余的光刻胶,在整个硅片上蒸发或淀积一层Al

(约1m厚),用反刻Al的掩模版反刻、腐蚀出

需要的Al连接图形。

(10)刻钝化孔

生长一层钝化层(如PSG),对器件/电路进行平坦化

和保护。

通过钝化版刻出钝化孔(压焊孔)。

图5-6硅栅NMOS工艺流程示意图

若要形成耗尽型NMOS器件,只需在第(5)、(6)步之间加一道掩模版,进行沟道区离子注入。

NMOS工艺流程的实质性概括:

P型掺杂的单晶硅片上生长一层厚SiO2。

MK1—刻出有源区或其他扩散区(薄氧化版/扩散版)。

MK2—形成耗尽型器件时,刻出离子注入区。

MK3—刻多晶硅图形(栅、多晶硅连线)。

以多晶硅栅为掩模,进行D、S的自对准扩散。

MK4—刻接触孔。

MK5—反刻Al。

MK6—刻钝化孔(压焊点窗口)

3、硅栅CMOS工艺

(1)P阱CMOS工艺流程

MK1—P阱版,确定P阱深扩散区域(阱注入剂量11013cm-2,能量60KeV)

MK2—确定薄氧化区,即有源区。

MK3—多晶硅版。

MK4—P+版,和MK2一起确定所有的P+扩散区域(一般为B注入,41014cm-221015cm-2,6080KeV)。

MK5—N+版,确定所有的N+区域(磷注入:

8101441015cm-2,6080KeV)

MK6—确定接触孔。

实际上在此之前,一般先作PSG磷硅玻璃回流平坦化(40008000Å

)。

刻出接触孔后,下一步蒸Al前,要用H2SO4+H2O2液加5%HF氢氟酸清洗,确保Al与Si的良好接触和与SiO2的良好附着。

MK7—反刻Al,确定金属层的连接图形。

MK8—刻钝化孔,露出向外引线的压焊点。

钝化层通常用PECVD实现:

1000Å

SiO2+4000Å

PSG+1000Å

SiO2或50007000Å

Si3N4

(2)N阱CMOS工艺以Berkeley大学N阱CMOS工艺为例,介绍N阱CMOS工艺流程。

Mask1N阱区确定磷注入的N阱区域

生长栅氧,淀积Si3N4

Mask2NMOS有源区刻出P型衬底上面的薄氧层,露出NMOS有源区窗口

在需要厚氧的区域,Si3N4被有选择性地刻蚀掉(等离子刻蚀或RIE)

用硼(B)作P型场注入

Mask3PMOS有源区刻出N阱上面的薄氧层,露出PMOS有源区窗口阱上的Si3N4被选择性地刻蚀掉,露出场区

用磷作N型场注入

刻蚀掉剩余的Si3N4层

调沟注入

在整个硅片上淀积重掺杂的N型多晶硅

Mask4NMOS栅刻N沟MOS多晶硅栅

砷(As)注入,在未被多晶硅覆盖的衬底区域形成n+区

Mask5PMOS栅刻P沟MOS多晶硅栅,引入硼注入,形成p+区

整个硅片上淀积厚氧化层

Mask6接触孔确定接触孔

Mask7金属淀积Al,形成互联图形

Mask8钝化长钝化层,并刻出钝化孔,露出压焊点

4、硅的局部氧化工艺

——Si3N4(氨气氛中硅烷SiH4还原法生长)只能被缓慢氧化,因此可用来保护下面的硅不被氧化。

选择性腐蚀氮化硅(180℃左右的磷酸)后,留下氧化物图形(见图5-7)。

由SiSiO2时,SiO2的体积约增大为Si体积的2.2倍。

因此,氧化物边缘台阶只有常规平面工艺的一半,有助于金属布线的连续性。

图5-7局部氧化示意图

如采用预腐蚀(腐蚀液:

HF+HNO3+H2O或醋酸稀释)局部氧化,则:

以Si3N4为掩模,在下一步进行氧化前将露出的Si有选择地腐蚀掉一部分,减少Si的量,可使氧化后的表面与未氧化的Si表面基本保持在同一平面(除在窗口附近稍有起伏)等平面工艺。

图5-8等平面工艺的实现

采用LOCOS工艺,与浅结工艺结合,可起到较好的隔离表面漏电流的作用,并能较好地实现硅片表面平坦化,有利于金属布线。

LOCOS工艺的缺点:

氮化物直接长在硅表面,将在窗孔中引起较高的位错密度,因此通常在生长氮化物之前先长一层薄的氧化物(几十Å

),降低因晶格失配导致的高位错密度。

但这层薄氧化物的存在,使氮化物边缘下面产生一些氧化,形成一锥形的氧化物穿进将成为窗孔的区域,形似鸟嘴“Birdbeak”。

当氮化层被腐蚀掉后,此“鸟嘴”仍可能保留,在浅扩散时,将阻挡杂质进入Si衬底内,使硅的有效使用面积降低。

另一方面,“鸟嘴”将使MOS管实际的沟道宽度W减小,导致IDS比设计值偏低,并产生阈值电压VT随W减小迅速升高形成所谓“窄沟效应”。

图5-9“鸟嘴”的形成

5.2.2体硅CMOS工艺设计中阱工艺的选择

1、P阱工艺

发展较早,技术较成熟。

轻掺杂的N型衬底上作PMOS,P阱内作NMOS,使VTP、VTN的匹配较易调整。

P阱衬底浓度(ND)较高,使n降低,PMOS衬底浓度NA较低,p有所提高,有利于P管、N管性能匹配。

2、N阱工艺

P型衬底作n-阱,与E/DNMOS工艺兼容。

轻掺杂P型衬底上的NMOS载流子迁移率n提高,尤其适合用在动态CMOS、P-E逻辑、多米诺逻辑中。

3、双阱工艺

在高浓度n+衬底上生长高阻外延层(接近半绝缘状态),可分别作N阱、P阱,闩锁效应得到抑制。

由双阱工艺思想发展到绝缘衬底上的CMOS技术——SOI(SiliconOnInsulator)。

圆片(Wafer)尺寸与衬底厚度:

3——0.4mm5——0.625mm

4——0.525mm6——0.75mm

硅片的大部分用于机械支撑。

阱的深度D、S的结深Xj+D、S耗尽扩散+阱与衬底间PN结之间的耗尽扩散+光刻、套刻间距

此外,阱深还与电源电压有关,VDD=5V,阱深56m;

VDD=10V,阱深89m。

5.3MOS集成电路的版图设计规则

图5-10基本的设计规则图解

5.3.1设计规则

——70年代末,Meed和Conway倡导以无量纲的“”为单位表示所有的几何尺寸限制,版图上所有图形和间距尺寸均为的整数倍。

通常取栅长L的一半,又称等比例设计规则。

由于其规则简单,主要适合于芯片设计新手使用,或不要求芯片面积最小,电路特性最佳的应用场合。

5.3.2微米设计规则

——80年代中期,为适应VLSIMOS电路制造工艺,发展了以微米为单位的绝对值表示的版图规则。

可针对一些细节进行具体设计,灵活性大,对电路性能的提高带来很大方便。

适用于有经验的设计师以及力求挖掘工艺潜能的场合。

5.4MOS集成电路版图举例

5.4.1硅栅CMOS反相器的输入保护电路

CMOS电路通常采用电阻、二极管网络作保护电路,如图5-11(a)所示,其版图见5-11(b)。

图5-11硅栅CMOS反相器的输入保护电路

实际经验证明,为实现良好的限流作用,一般R设计为400800之间;

为保证二极管有一定的瞬间大电流泄放能力,其面积设计为500800m2之间比较合适。

此外,D1、D2分别加有隔离环,以抑制闩锁效应。

5.4.2铝栅工艺CMOS反相器版图举例

图5-12为铝栅CMOS反相器版图示意图。

可见,为了防止寄生沟道以及p管、n管的相互影响,采用了保护环或隔离环:

对n沟器件用p+环包围起来,p沟器件用n+环隔离开,p+、n+环都以反偏形式接到地和电源上,消除两种沟道间漏电的可能。

版图分解:

刻P阱

刻P+区/环

刻n+区/环

刻栅、预刻接触孔

刻Al

图5-12铝栅CMOS反相器版图示意图

5.4.3硅栅NMOS反相器版图举例

1、E/ENMOS反相器

刻有源区

刻多晶硅

刻接触孔

反刻Al

图5-12E/ENMOS反相器版图示意

图5-12E/ENMOS反相器版图示意

2、E/DNMOS反相器

刻耗尽注入区

图5-13E/DNMOS反相器版图

5.4.4硅栅CMOS与非门版图举例

刻p+环

刻n+环

刻PSD

刻NSD

图5-14硅栅CMOS与非门版图

5.5版图设计技巧

1、布局要合理

(1)引出端分布是否便于使用或与其他相关电路兼容,是否符合管壳引出线排列要求。

(2)特殊要求的单元是否安排合理,如p阱与p管漏源p+区离远一些,使pnp,抑制Latch-up,尤其要注意输出级。

(3)布局是否紧凑,以节约芯片面积,一般尽可能将各单元设计成方形。

(4)考虑到热场对器件工作的影响,应注意电路温度分布是否合理。

2、单元配置恰当

(1)芯片面积降低10%,管芯成品率/圆片可提高1520%。

(2)多用并联形式,如或非门,少用串联形式,如与非门。

(3)大跨导管采用梳状或马蹄形,小跨导管采用条状图形,使图形排列尽可能规整。

3、布线合理

布线面积往往为其电路元器件总面积的几倍,在多层布线中尤为突出。

扩散条/多晶硅互连多为垂直方向,金属连线为水平方向,电源地线采用金属线,与其他金属线平行。

长连线选用金属。

多晶硅穿过Al线下面时,长度尽可能短,以降低寄生电容。

注意VDD、VSS布线,连线要有适当的宽度。

容易引起“串扰”的布线(主要为传送不同信号的连线),一定要远离,不可靠拢平行排列。

4、CMOS电路版图设计对布线和接触孔的特殊要求

(1)为抑制Latchup,要特别注意合理布置电源接触孔和VDD引线,减小横向电流密度和横向电阻RS、RW。

采用接衬底的环行VDD布线。

增多VDD、VSS接触孔,加大接触面积,增加连线牢固性。

对每一个VDD孔,在相邻阱中配以对应的VSS接触孔,以增加并行电流通路。

尽量使VDD、VSS接触孔的长边相互平行。

接VDD的孔尽可能离阱近一些。

接VSS的孔尽可能安排在阱的所有边上(P阱)。

(2)尽量不要使多晶硅位于p+区域上

多晶硅大多用n+掺杂,以获得较低的电阻率。

若多晶硅位于p+区域,在进行p+掺杂时多晶硅已存在,同时对其也进行了掺杂——导致杂质补偿,使多晶硅。

(3)金属间距应留得较大一些(3或4)

因为,金属对光得反射能力强,使得光刻时难以精确分辨金属边缘。

应适当留以裕量。

5、双层金属布线时的优化方案

(1)全局电源线、地线和时钟线用第二层金属线。

(2)电源支线和信号线用第一层金属线(两层金属之间用通孔连接)。

(3)尽可能使两层金属互相垂直,减小交叠部分得面积。