EDA实验指导书Word格式文档下载.docx

《EDA实验指导书Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《EDA实验指导书Word格式文档下载.docx(34页珍藏版)》请在冰豆网上搜索。

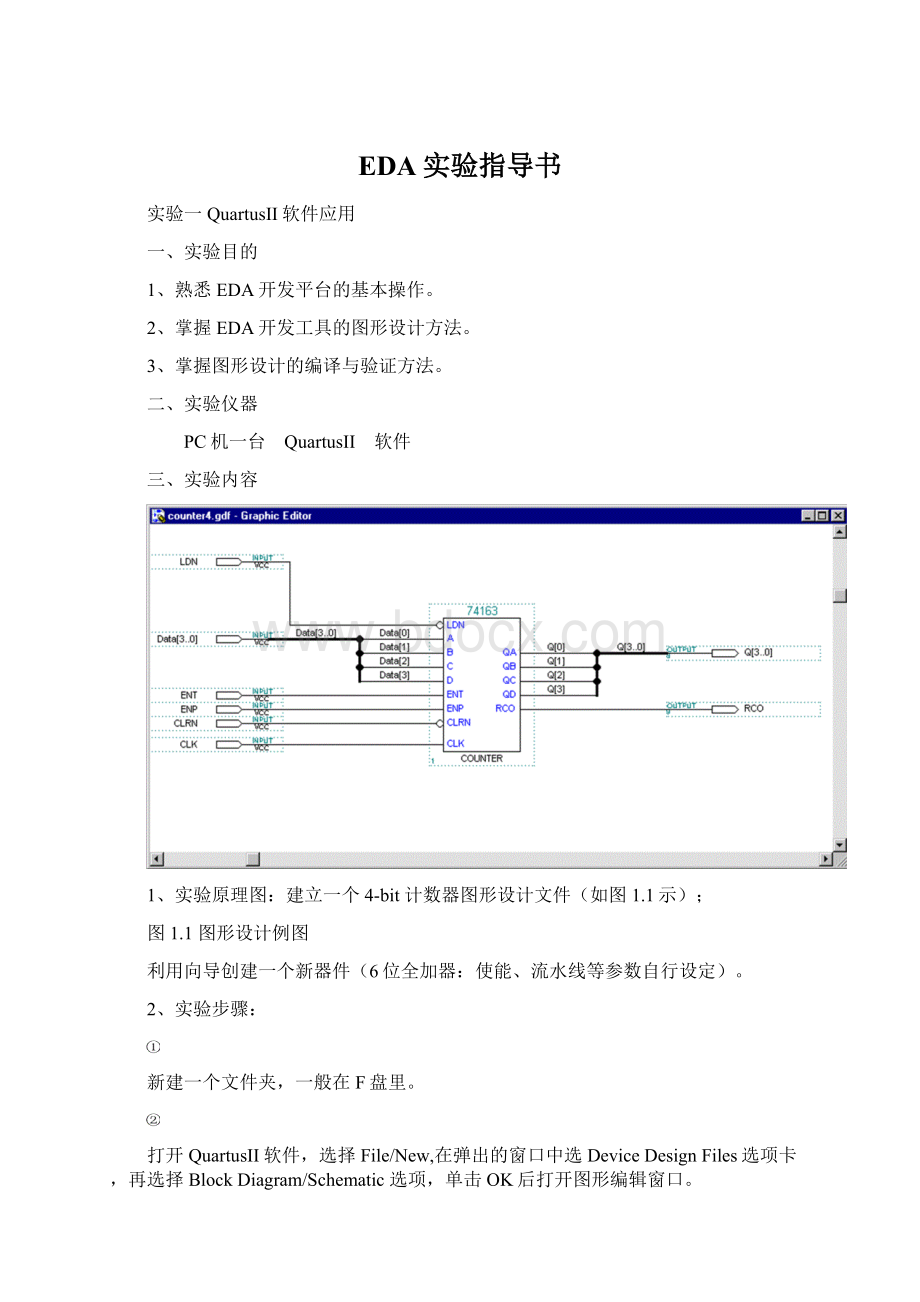

1、24进制加法计数器的程序:

LIBRARYIeee;

USEieee.std_logic_1164.ALL;

USEieee.std_logic_unsigned.ALL;

ENTITYcount24IS

PORT(en,clk:

INSTD_LOGIC;

qa:

outSTD_LOGIC_VECTOR(3DOWNTO0);

--个位数计数

qb:

outSTD_LOGIC_VECTOR(1DOWNTO0));

--十位数计数

ENDcount24;

ARCHITECTUREa1OFcount24IS

BEGIN

process(clk)

variabletma:

STD_LOGIC_VECTOR(3DOWNTO0);

variabletmb:

STD_LOGIC_VECTOR(1DOWNTO0);

begin

ifclk'

eventandclk='

1'

then

ifen='

iftma="

1001"

thentma:

="

0000"

;

tmb:

=tmb+1;

Elsiftmb="

10"

andtma="

0011"

tmb:

00"

elsetma:

=tma+1;

endif;

qa<

=tma;

qb<

=tmb;

endprocess;

ENDa1;

2、实验步骤:

1)24进制计数器

打开QuartusII软件,选择File/New,在弹出的窗口中选DeviceDesignFiles选项卡,再选择VHDLFile选项,单击OK后打开程序编辑窗口。

选择File/SaveAs命令,保存文件在已经创建的文件夹里,文件名一定要与程序的实体名一致。

打开工程中的程序文件,把1中24进制加法计数器的程序输入。

打开波形编辑器,选择File/New,在New中选择OtherFiles中的VectorWaveformFile选项,单击OK,出现空白的波形编译窗口。

2)修改以上程序获得60进制加法计数器,并进行功能和时间仿真验证。

手写出24进制与60进制的加法器的实验程序,打印出仿真波形图,完成实验报告

1、比较图形设计和语言设计方法的差别和优缺点。

实验三组合逻辑电路的VHDL描述

1、掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3、熟悉FPGA设计的过程,比较原理图输入和文本输入的优劣。

PC机一台 QuartusII 软件

1、用VHDL语言设计一个四舍五入判别电路,其输入为8421BCD码,要求当输入大于或等于5时,判别电路输出为1,反之为0。

参考电路原理图如图3.1所示。

图3.1四舍五入判别参考电路

2、用VHDL语言设计四个开关控制一盏灯的逻辑电路,要求改变任意开关的状态能够引起灯亮灭状态的改变。

(即任一开关的合断改变原来灯亮灭的状态,参考电路原理图如图3.2所示。

)

图3.2灯控参考电路

3、用VHDL语言设计一个优先排队电路(参考电路原理图如图3.3所示),其中:

A=1,最高优先级;

B=1,次高优先级;

C=1,最低优先级。

要求输出端最多只能有一端为“1”,即只能是优先级较高的输入端所对应的输出端为“1”。

图3.3优先排队参考电路

4、自行设计纪录方式,完成实验报告

1、CPLD和FPGA有什么差别?

设计中应该注意什么问题?

2、图形设计方法中采用LPM设计有什么好处?

实验四扫描显示驱动电路

1、了解实验系统中8位八段数码管显示模块的工作原理;

2、掌握计数器和地址发生器的VHDL描述方法;

3、掌握LED数码管7段译码器的VHDL描述方法;

4、掌握编码器的VHDL描述方法;

5、设计标准扫描驱动电路模块,以备后面实验用。

PC机一台 QuartusII 软件EDA实验箱

图4.1所示的是8位数码扫描显示电路,其中每个数码管的8个段:

h、g、f、e、d、c、b、a(h是小数点)都分别连在一起,8个数码管分别由8个选通信号k1、k2、…k8来选择。

被选通的数码管显示数据,其余关闭。

如在某一时刻,k3为高电平,其余选通信号为低电平,这时仅k3对应的数码管显示来自段信号端的数据,而其它7个数码管呈现关闭状态。

根据这种电路状况,如果希望在8个数码管显示希望的数据,就必须使得8个选通信号k1、k2、…k8分别被单独选通,并在此同时,在段信号输入口加上希望在该对应数码管上显示的数据,于是随着选通信号的扫变,就能实现扫描显示的目的。

其VHDL示例程序如程序4.1所示。

图4.18位数码扫描显示电路图

1、实验内容1:

理解程序中各语句的含义,以及该例的整体功能。

对该例进行编辑、编译、综合、适配、仿真,给出仿真波形。

实验方式:

若考虑小数点,SG的8个段分别与PIO49、PIO48、…、PIO42(高位在右)、BT的8个位分别与PIO34、PIO35、…、PIO41(高位在左);

电路模式不限,引脚图参考附图11。

将GW48EDA系统左下方的拨码开关全部向上拨,这时实验系统的8个数码管构成图4.1的电路结构,时钟CLK可选择clock0,通过跳线选择16384Hz信号。

引脚锁定后进行编译、下载和硬件测试实验。

将实验过程和实验结果写进实验报告。

2、自行设计纪录方式,完成实验报告

【例5.1】

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYSCAN_LEDIS

PORT(CLK:

SG:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

--段控制信号输出

BT:

OUTSTD_LOGIC_VECTOR(7DOWNTO0));

--位控制信号输出

END;

ARCHITECTUREoneOFSCAN_LEDIS

SIGNALCNT8:

STD_LOGIC_VECTOR(2DOWNTO0);

SIGNALA:

INTEGERRANGE0TO15;

P1:

PROCESS(CNT8)--编码器

BEGIN

CASECNT8IS

WHEN"

000"

=>

BT<

="

00000001"

;

A<

=1;

001"

00000010"

=3;

010"

00000100"

=5;

011"

00001000"

=7;

100"

00010000"

=9;

101"

00100000"

=11;

110"

01000000"

=13;

111"

10000000"

=15;

WHENOTHERS=>

NULL;

ENDCASE;

ENDPROCESSP1;

P2:

PROCESS(CLK)--计数器

IFCLK'

EVENTANDCLK='

THENCNT8<

=CNT8+1;

ENDIF;

ENDPROCESSP2;

P3:

PROCESS(A)–-译码电路

CASEAIS

WHEN0=>

SG<

0111111"

WHEN1=>

0000110"

WHEN2=>

1011011"

WHEN3=>

1001111"

WHEN4=>

1100110"

WHEN5=>

1101101"

WHEN6=>

1111101"

WHEN7=>

0000111"

WHEN8=>

1111111"

WHEN9=>

1101111"

WHEN10=>

1110111"

WHEN11=>

1111100"

WHEN12=>

0111001"

WHEN13=>

1011110"

WHEN14=>

1111001"

WHEN15=>

1110001"

ENDPROCESSP3;

例4.1是扫描显示的示例程序,其中clk是扫描时钟;

SG为7段控制信号,由高位至低位分别接g、f、e、d、c、b、a7个段;

BT是位选控制信号,接图中的8个选通信号:

k1、k2、…k8。

程序中CNT8是一个3位计数器,作扫描计数信号,由进程P2生成;

进程P3是7段译码查表输出程序,进程P1是对8个数码管选通的扫描程序,例如当CNT8等于"

时,K2对应的数码管被选通,同时,A被赋值3,再由进程P3译码输出"

,显示在数码管上即为“3”;

当CNT8扫变时,将能在8个数码管上显示数据:

13579BDF。

1、字形编码的种类,即一个8段数码管可产生多少种字符,产生所有字符需多少根译码信号线?

2、字符显示亮度和扫描频率的关系,且让人感觉不出光烁现象的最低扫描频率是多少?

3、扫描显示和静态显示有什么差别?

使用扫描显示有什么好处?

实验五VHDL硬件设计

-------计数器及时序电路描述

1、了解时序电路的经典设计方法(JK触发器和一般逻辑门组成的时序逻辑电路)。

2、了解同步计数器,异步计数器的使用方法。

3、了解同步计数器通过清零阻塞法和预显数法得到循环任意进制计数器的方法。

4、理解时序电路和同步计数器加译码电路的联系,设计任意编码计数器。

5、了解同步设计和异步设计的区别。

实验内容中的六个实验均要通过实验十的“扫描显示电路”进行显示,具体连线根据每个实验内容完成时的管脚分配来定义,同相应的输入输出接口功能模块相连,扫描模块的设计参考实验四。

1、用JK触发器设计异步四位二进制加法计数器。

8位LED数码管16进制显示扫描显示驱动电路设计,实验参考原理图如图5.1所示。

其中,计数时钟频率CLK<

2Hz;

扫描时钟频率>

40Hz;

四位JK触发器接成异步计数器;

SEL0~SEL2为扫描地址(控制八位数码管的扫描顺序和速度);

A……G为显示译码输出,代表数码管的八个段位(a,b,c,d,e,f,g);

八位数码管同时顺序显示0~F。

图5.1计数器设计参考原理图

3.绘制原理图后进行仿真验证,最后下载到实验箱。

1、说明在FPGA设计中,同步设计和异步设计的不同之处。

2、图形设计和VHDL语言设计编程各有什么优点,混合编程时应注意些什么问题?

3、应用状态机设计时序电路需要注意哪些问题?

实验六函数信号发生器

1、了解函数信号发生的方法。

2、掌握LPM_ROM的使用方法。

3、了解DAC0832的工作原理和控制时序。

4、掌握DAC0832的控制时序的VHDL设计实现方法。

5、了解低通滤波电路的原理及其在信号发生中的应用。

2、熟悉SignalTapII测试方法。

计算机、QuartusII软件、EDA试验箱、示波器。

1、在QuartusII上完成正弦信号发生器设计,包括仿真和资源利用情况了解(假设利用Cyclone器件)。

最后在实验系统上实测,包括SignalTapII测试、FPGA中ROM的在系统数据读写测试和利用示波器测试。

示例程序如例6.1,

【例6.1】正弦信号发生器顶层设计

--正弦信号发生器源文件

ENTITYSINGTIS

--信号源时钟

DOUT:

OUTSTD_LOGIC_VECTOR(7DOWNTO0));

--8位波形数据输出

ARCHITECTUREDACCOFSINGTIS

COMPONENTdata_rom--调用波形数据存储器LPM_ROM文件:

data_rom.vhd声明

PORT(address:

INSTD_LOGIC_VECTOR(5DOWNTO0);

--6位地址信号

inclock:

INSTD_LOGIC;

--地址锁存时钟

q:

ENDCOMPONENT;

SIGNALQ1:

STD_LOGIC_VECTOR(5DOWNTO0);

--设定内部节点作为地址计数器

PROCESS(CLK)--LPM_ROM地址发生器进程

IFCLK'

THENQ1<

=Q1+1;

--Q1作为地址发生器计数器

ENDIF;

ENDPROCESS;

u1:

data_romPORTMAP(address=>

Q1,q=>

DOUT,inclock=>

CLK);

--例化

信号输出的D/A使用实验系统上的DAC0832,注意其转换速率是1μs,其引脚功能简述如下:

ILE:

数据锁存允许信号,高电平有效,系统板上已直接连在+5V上;

WR1、WR2:

写信号1、2,低电平有效;

XFER:

数据传送控制信号,低电平有效;

VREF:

基准电压,可正可负,-10V~+10V;

RFB:

反馈电阻端;

IOUT1/IOUT2:

电流输出端。

D/A转换量是以电流形式输出的,所以必须将电流信号变为电压信号;

AGND/DGND:

模拟地与数字地。

在高速情况下,此二地的连接线必须尽可能短,且系统的单点接地点须接在此连线的某一点上。

建议选择GW48系统的电路模式No.5,由附录对应的电路图可见,DAC0832的8位数据口D[7..0]分别与FPGA的PIO31、30..、24相连,如果目标器件是EP1C3T144,则对应的引脚是:

72、71、70、69、68、67、52、51;

时钟CLK接系统的clock0,对应的引脚是93,选择的时钟频率不能太高(转换速率1μs,)。

还应该注意,DAC0832电路须接有+/-12V电压:

GW48系统的+/-12V电源开关在系统左侧上方。

然后下载SINGT.sof到FPGA中;

波形输出在系统左下角,将示波器的地与GW48系统的地(GND)相接,信号端与“AOUT”信号输出端相接。

如果希望对输出信号进行滤波,将GW48系统左下角的拨码开关的“8”向下拨,则波形滤波输出,向上拨则未滤波输出,这可从输出的波形看出。

1、采用本方法估计可以产生的正弦波的频率能到多少?

2、若要产生任意信号波形和高速波形输出应该注意什么问题?

附录1GW48EDA/SOPC主系统使用说明

第一节GW48教学实验系统原理与使用介绍

一、GW48系统使用注意事项

1、闲置不用GW48系统时,必须关闭电源!

!

2、在实验中,当选中某种模式后,要按一下右侧的复位键,以使系统进入该结构模式工作。

注意此复位键仅对实验系统的监控模块复位,而对目标器件FPGA没有影响,FPGA本身没有复位的概念,上电后即工作,在没有配置前,FPGA的I/O口是随机的,故可以从数码管上看到随机闪动,配置后的I/O口才会有确定的输出电平。

3、换目标芯片时要特别注意,不要插反或插错,也不要带电插拔,确信插对后才能开电源。

其它接口都可带电插拔。

请特别注意,尽可能不要随意插拔适配板,及实验系统上的其他芯片。

4、使用实验系统前,查阅系统的默认设置ppt文件:

EDA技术与VHDL书实验课件说明_必读.ppt。

二、GW48系统主板结构与使用方法

以下将详述GW48系列SOPC/EDA实验开发系统(GW48-PK2/CK)结构与使用方法,对于这2种型号的不同之处将给予单独指出。

该系统的实验电路结构是可控的。

即可通过控制接口键,使之改变连接方式以适应不同的实验需要。

因而,从物理结构上看,实验板的电路结构是固定的,但其内部的信息流在主控器的控制下,电路结构将发生变化---重配置。

这种“多任务重配置”设计方案的目的有3个:

1、适应更多的实验与开发项目;

2、适应更多的PLD公司的器件;

3、适应更多的不同封装的FPGA和CPLD器件。

系统板面主要部件及其使用方法说明如下。

以下是对GW48系统主板功能块的注释。

附图1GW48EDA系统电子设计二次开发信号图

(1)“模式选择键”:

按动该键能使实验板产生12种不同的实验电路结构。

这些结构如第二节的13张实验电路结构图所示。

例如选择了“NO.3”图,须按动系统板上此键,直至数码管“模式指示”数码管显示“3”,于是系统即进入了NO.3图所示的实验电路结构。

(2)适配板:

这是一块插于主系统板上的目标芯片适配座。

对于不同的目标芯片可配不同的适配座。

可用的目标芯片包括目前世界上最大的六家FPGA/CPLD厂商几乎所有CPLD、FPGA和所有ispPAC等模拟EDA器件。

第七节的表中已列出多种芯片对系统板引脚的对应关系,以利在实验时经常查用。

(3)ByteBlasterMV编程配置口:

如果要进行独立电子系统开发、应用系统开发、电子设计竞赛等开发实践活动,首先应该将系统板上的目标芯片适配座拔下(对于Cyclone器件不用拔),用配置的10芯编程线将“ByteBlasterMV”口和独立系统上适配板上的10芯口相接,进行在系统编程(如GWDVP-B板),进行调试测试。

“ByteBlasterMV”口能对不同公司,不同封装的CPLD/FPGA进行编程下载,也能对isp单片机89S51等进行编程。

编程的目标芯片和引脚连线可参考附图1,从而进行二次开发。

(4)ByteBlasterII编程配置口:

该口主要用于对Cyclone系列AS模式专用配置器件EPCS4和EPCS1等编程。

(5)混合工作电压源:

系统不必通过切换即可为CPLD/FPGA目标器件提供5V、3.3V、2.5V、1.8V和1.5V工作电源,此电源位置可参考附图1。

(6)JP5编程模式选择跳线:

(仅GW48-PK2型含此)。

如果要对Cyclone的配置芯片进行编程,应该将跳线接于“ByBtII”端,在将标有“ByteBlasterII”编程配置口同适配板上EPCS4/1的AS模式下载口用10芯线连接起来,通过QuartusII进行编程。

当短路“Others”端时,可对其它所有器件编程,端口信号参考附图1。

(7)JP6/JVCC/VS2编程电压选择跳线:

跳线JVCC(GW48—PK2型标为“JP6”)是对编程下载口的选择跳线。

对5V器件,如10K10、10K20、7128S、1032、95108、89S51单片机等,必须选“5.0V”。

而对低于或等于3.3V的低压器件,如1K30、1K100、10K30E、20K300、Cyclone、7128B等一律选择“3.3V”一端。

(8)并行下载口:

此接口通过下载线与微机的打印机口相连。

来自PC机的下载控制信号和CPLD/FPGA的目标码将通过此口,完成对目标芯片的编程下载。

计算机的并行