基于FPGA的FIR数字低通滤波器的IP核设计解读Word下载.docx

《基于FPGA的FIR数字低通滤波器的IP核设计解读Word下载.docx》由会员分享,可在线阅读,更多相关《基于FPGA的FIR数字低通滤波器的IP核设计解读Word下载.docx(47页珍藏版)》请在冰豆网上搜索。

(3)A/D采样电路、D/A转换电路的选择

根据采样定理,和信号的最高频率fsmax=20kHz,求得采样频率fc>

2fmax,即fc必须大于40kHz。

对应采样最小时间T=1/fc=25(ns),我们考虑了AD7810和MAX148,经过对性能的分析比较,设计选择了转换速度快,转换精度高的MAX148。

实现IFFT信号模拟输出需要经过D/A转换电路。

选择时考虑了DAC0808和TLC5615两款芯片。

经过实际分析和性能比较,TLC5615可达到10位转换,串行输出,外围电路简单。

所以本系统选择TLC5615。

(5)低频功率放大器电路的设计和选择

功率放大器分为甲类、乙类、甲乙类、丙类、丁类放大器。

通常运用的放大器中效率比较:

η甲<

η甲乙<

η乙<

η丙<

η丁

常用的放大器中理想情况下甲类放大器的最高效率为50%,乙类功放的最高频率为78.5%,丙类功放的最高频率可达85%-90%。

但丙类功放要求特殊形式负载,不适用低频,而甲类放大器达不到效率≥60%的系统要求。

所以本系统选择使用乙类放大器作为低频功放。

实际设计时在电路中引入了反馈电路,试性能有了较好的改善。

由于不能使用MOS集成功率模块,本设计使用晶体管二极管和分立的大功率MOS管等元件搭建了引入反馈的乙类推挽功率放大器。

1.2.2系统组成

经过以上各方面的方案论证与分析比较,本设计采用基于FPGA数字幅频均衡功率放大器的方案。

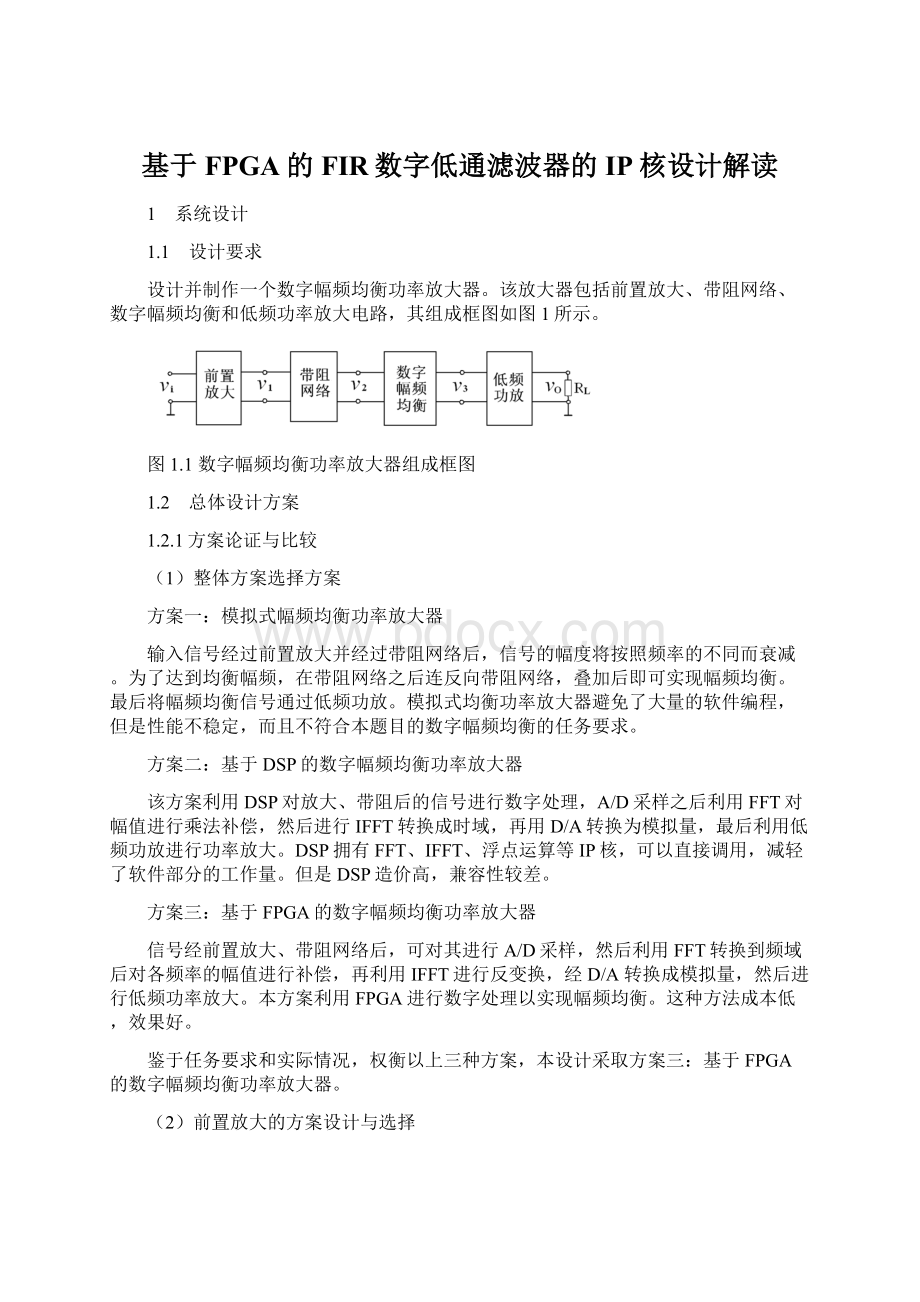

具体系统框图如图1.2所示。

系统分为前置放大器、带阻网络、FPGA数字处理模块、功率放大器模块。

前置放大器使用AD603和NE5532级联放大,阻带网络按题目说明焊接,得到频域值,数字幅频均衡部分使用FPGA技术,先用MAX148进行采样,再利用FFT原理进行幅频补偿,然后进行IFFT,经D/A转换得到信号时域模拟量,再通过功率放大电路完成功率放大。

AD603、NE5532级联MAX148

ViV1V2

FPGA数字处理部分

输出信号VoRLV3

图1.2基于FPGA的数字幅频均衡功率放大器系统框图

2 单元硬件电路设计

2.1 前置放大的设计

题目要求输入信号有效值小于10mV,电压放大倍数不小于400倍,增益

A(dB)=20lg400=52.04(dB),而输入信号频率在20Hz-20kHz,所以要求选用放大器须有足够的增益和增益带宽。

AD603是AD公司推出的一种低噪声且由电压控制的增益放大器。

它提供精确的、可由管脚选择的增益,它的增益是线性变化的,且在温度和电源电压变化时有很高的稳定性,在带宽为9MHz时增益控制电压VG=VC1-VC2(-500mV≤VG≤500mV),理论上增益与增益控制电压的关系:

增益A1(dB)=40VG+30 (从10dB到50dB)

NE5532的增益计算:

增益A2(dB)=20lg(RF/RE)(dB)

级联后增益可达:

A(dB)=(40VG+30)×

[20lg(RF/RE)](dB)

而且增益在带宽内可调,信号不失真。

在20Hz-20kHz通频带内衰减小于-1dB。

为了实现输出阻抗为600Ω,在输出端加射级跟随器然后串联600Ω电阻。

前置放大器电路如图2.1所示。

电压增益可由滑动变阻器R4、R3来控制,R4控制VG=VC1-VC2=VC1–0=VC1,R3控制RF/RE,这样即可实现增益可调。

图2.1前置放大电路图

2.2带阻网络的设计

根据题目说明1的带阻网络图搭建带阻电路。

为了达到较高的精度,所用电阻精确度均为千分之一,电感电容也精确度较高。

带阻网络电路如图所示。

信号经过带阻网络后时域变为频域,各个频率对应特定的幅值。

其波特图特性为400Hz左右衰减倍数大,从约400Hz向两侧的衰减倍数逐渐减小。

2.3 A/D采样、D/A转换的电路的设计

A/D部分实现模拟信号到数字信号的转换,ADC采用10位的MAX148。

电路图如图附录4.2所示。

在模拟信号输入端加600Ω接地,然后串接射级跟随器。

D/A部分将数字处理部分得到的数字信号转换成模拟信号,芯片采用10位转换、串行输出的TLC5615,外围电路如图附录4.3所示。

2.4 功率放大器电路的设计

电路如图2.5所示,设计为引入反馈的乙类推挽MOS管功率放大器。

电路的MOS管选用IFR9530和IFR530组成对管使用,NE5532构成电压驱动激励级,功率放大器采用±

20V为供电。

因为经过前置放大器、带阻网络、数字幅频均衡后的信号会使Vi放大400倍左右,所以当Vi为5mV时功率放大器前端的输入电压V3约为2V。

功率放大器的负载为RL=8Ω。

功放输出功率:

,电源供给的功率:

,功率放大器的效率为:

为了实现20Hz-20kHz带通,在功放前设置高通RC滤波电路和低通滤波电路。

要求截止频率为20Hz,由系统函数,

,

,

令R约1.5kΩ,可得出电容的大概值。

R未算入后续电路的阻抗,所以可对C的值在附近调试。

同理,

,取R=500kΩ,可得到电容C的大概值。

因为R未算入其它阻抗,也可对电容在附近调试。

反馈中电容取120pF。

图2.2低频功率放大器电路图

3 软件设计

FPGA设计用verilog语言对其编程,采用

Quartus的Verilog编译。

程序分为控制部分

和数字处理部分。

3.1 控制部分的程序设计

控制部分的程序主要是分为模数转换和数

模转换两大部分,通过FPGA来控制A/D和D/A

电路进行转换。

3.2数字处理部分的程序设计

数字处理部分的程序主要是完成FFT时频

变换、浮点乘法和IFFT反变换等功能。

3.3主程序流程图

流程图如右图所示。

4系统测试

4.1测试使用的仪器

信号发生器FG708S数字万用表UT-52直流稳压稳流电源JW-4型

数字示波器TDS2012B频率特性测试仪BT3-D

4.2指标测试和测试结果

4.2.1前置放大器部分的指标测试和测试结果

(1)放大倍数和通频带的测试

采用示波器TDS2012B对电压幅值进行测量,当输入信号有效值5mV时幅值为5mV×

=7.07mV,所以信号发生器幅值设为7mV,改变信号频率,在放大电路输出端利用示波器测试不同频率信号对应的输出信号幅值。

表4.1放大倍数测试记录表

Vi

/mV

输出信号幅值Vo/V

平均值

2020Hz

100Hz

300Hz

500Hz

2k

4k

10k

14k

16k

20k

7

2.98V

2.97V

3.04V

3.18V

2.99V

2.89V

2.95V

根据表中数据并计算可知,放大器放大倍数达到428倍,且在带宽内增益稳定。

计算各个频率的增益值:

A=20lg(Vo/Vi),可以证明-1dB通频带包括20Hz-20kHz。

(2)输出电阻的测试

利用公式伏安法对输出电阻进行测量:

表4.2输出电阻测试记录表

Uo1(V)

Uo2(V)

Ri(Ω)

5.84

2.96

593

5.98

2.98

596

5.82

2.90

601

(令RL=600Ω)

求平均数后得:

Ro=595(Ω)

4.2.2 带阻网络部分的指标测试和结果

要求以10kHz时输出的信号V2电压幅度为基准最大衰减≥10dB。

具体结果:

表4.3带阻网络衰减测试记录表

测试数据

频率频率

20Hz20Hz

1kHz

5kHz

10kHz10kHz

20kHz20kHz

Vi幅值

0.67V

0.27V

0.336V

0.65V

1.02V

1.23V

由测试结果可知,500Hz的衰减最大,与10kHz相比衰减10.54dB。

4.2.3 数字幅频均衡电路的指标测试和结果

(1)输入阻抗的测试

利用伏安法测试输入阻抗表4.4数字幅频均衡电路输入电阻测试记录表

测试项目

1

2

3

Ui/V

5

U1/V

9.98

9.97

10.09

U2/V

4.96

4.95

4.93

Ri

597

598

603

对Ri取平均值得:

Ri=599(Ω)

(2)电压幅度波动的测试

先测量10kHz时的电压幅度V0,然后测不同频率的电压幅度Vn,计算20lg[(Vn-V0)/V0]。

表4.6电压幅度波动测试记录表

频率(Hz)

20

1k

5k

15k

Vn(V)

2.10

2.01

2.34

2.23

2.29

2.4

20lg(20lg(Vn/V0)

-0.45

1.10

0.47

0.23

1.30

4.2.4 功率放大器部分的指标和测试结果

(1)输出功率和输出波形的测试表4.7输出功率测试记录表

Uo(V)

Po(W)

13.428V

22.53W

13.444V

22.59W

13.410V

22.47W

用数字万用表的伏特表测负载8Ω上的

电压Uo,利用公式计算输出功率。

求平均值得:

Po=22.53(W)

利用数字示波器TDS2012B观察输出波形:

输出正弦波,无明显失真。

(2)通频带的测试表4.8通过频带测试记录表

类别

频率

f0

1.93kHz

fL

19.93Hz

fH

28.6kHz

对输入信号的频率从20Hz调到20kHz,

使用示波器观察放大倍数最大时的幅值并记录。

在改变频率使幅值变为最大幅值的0.707倍,记录频率值。

(3)放大器效率的测试

功率放大器效率为:

=67%

4.3结果分析

本设计实现了题目任务的大部分要求和指标,在前置放大器放大倍数、带阻网络最大衰减、功率放大器输出功率以及功率放大器的效率等方面都做了一定的扩展,总体上较好的完成了任务要求。

但是数字幅频均衡方面因为时间有限而且编程要求较高所以实现效果不佳。

另外,部分实际测试结果与Multisim仿真软件的仿真结果有差异,虽然实现了指标要求,但是与理论值有差异。

分析原因,输入信号为小于10mV的小信号,器件噪声、器件精密度、电路板的焊制会对频率的波形、稳定性和准确度产生影响。

功放部分的效率会受器件的功耗,滤波器电路的影响。

5 结论

本设计采用基于FPGA的数字幅频均衡功率放大器的方案。

系统分为前置放大、带阻网络、FPGA数字处理模块、功率放大器。

前置放大器使用AD603和NE5532级联放大,放大倍数符合要求。

阻带网络按题目说明焊接,达到要求的衰减值。

数字幅频均衡部分使用FPGA技术,A/D采样后利用FFT原理变换到频域根据浮点乘法原理对各点进行补偿,然后IFFT得到时域,再经D/A转换,通过功率放大电路完成功率放大。

功率放大器设计为带负载的乙类推挽放大器,输出功率、效率较高。

系统大部分指标达到任务要求。

附录4电路原理图

电路原理图分前置放大部分、带阻网络部分、数字幅频均衡部分、功率放大器部分。

(1)带阻网络部分

图附录4.1带阻网络电路图

(2)A/D采样电路

图附录4.2A/D采样电路图

(3)D/A转换部分电路

图附录4.3D/A转换电路图

(4)低通滤波算法电路

图附录4.4低通滤波器

(5)高通滤波算法电路

图附录4.5高通滤波电路

目录

摘要I

AbstractII

1绪论1

1.1课题的目的和意义1

1.2FPGA技术的发展及应用2

1.3FPGA软件设计工具QuartusII3

2FIR数字滤波器的理论研究及分析5

2.1数字滤波器的理论基础5

2.2数字滤波器的分类5

2.3FIR数字滤波器的设计方法6

3FPGADSP系统设计分析7

3.1DSP的基本概念7

3.2FPGA实现DSP的特点8

3.3DSPBuilder设计工具及设计规则9

4基于FPGA的FIR低通滤波器设计12

4.1设计方案12

4.2FDATool滤波器设计12

4.3FPGA定点数的确定14

4.3.1导出系数文件14

4.3.2FPGA定点数转换15

4.4FIR滤波器模型的建立17

4.4.1乘加子系统的搭建17

4.4.2滤波器模块的添加和模块参数设置21

4.4.3各模块的连接27

5Simulink仿真29

5.1仿真时间设定29

5.2示波器模块显示29

5.3仿真结果分析31

6总结33

参考文献34

致谢35

附录36

附录1FIR滤波器仿真模型图36

附录2FIR滤波器测试模型图37

附录3FPGA定点数转换程序37

摘要

在现代通信领域中,FIR数字滤波器以其良好的线性特性被广泛使用,属于数字信号处理的基本模块之一。

在实践中,往往要求对信号处理有实时性和灵活性,而已有的一些软件和硬件的实现方式则难以同时到达这两方面的要求。

随着可编程逻辑器件和FDA技术的发展,使用FPGA来实现FIR滤波器,既具有实时性,又兼顾了一定的灵活性,越来越多的电子工程师采用FPGA器件来实现FIR滤波器。

本设计利用MATLAB/Simulink/DSPBuilder设计一个FIR滤波器。

首先根据滤波器指标,利用MATLAB工具箱滤波器设计工具设计滤波器,然后根据实际需要将系数导出并量化。

接下来在Simulink中使用Simulink库和DSPBuilder库建立设计模型,并在Simulink中仿真。

关键词:

FPGA,FIR低通滤波器,DSPBuilder,Simulink

Abstract

Inthemoderncommunicationsfield,theFIRDigitalFilterisusedfromanypracticalapplicationsforitsgoodlinearphasecharacter,anditprovideanimportantfunctionindigitalsignalprocessingdesign.Inpractice,thereisalwaysareal-timeandflexiblerequirementforsignalprocessing.However,softwareandhardwaretechniquesavailableforimplementationaredifficulttomeetthedemandforthetwoaspectsinthesametime.AlongwiththedevelopmentofPLDdeviceandEDAtechnology,moreandmoreelectricalengineersuseFPGAtoimplementFIRFilter,asitnotonlymeetthereal-timerequirement,butalsohassomeflexibility.

ThisdesignusesMATLAB/Simulink/DSPBuildertodesignaFIRDigitalFilter.Firstlyaccordingtotheindexofthefilter,MATLAB/Toolboxes/FilterDesign/FilterDesign&

AnalysisTool(FDATool)isusedtodesignthefilter.Thenaccordingtopracticalrequirementderiveandquantifythecoefficient.UsetheSimulinkLibraryandtheDSPBuilderLibrarytoestablishdesignmodelandsimulateintheSimulink.

Keywords:

FPGA,FIRlowpassFilter,DSPBuilder,Simulink

1绪论

1.1课题的目的和意义

在当今的生活中,身边的工程技术领域越来越受到关注。

其中的通信领域所涉及到的各种信号更是重中之重。

如何在较强的背景的噪声下和干扰的信号下有效提炼出真正的有用信号并将其真正运用到实际的工程中,这正是信号处理要解决的问题。

上世纪60年代,数字信号处理在理论层上发展迅猛。

其体系和框架逐渐成熟,如今,数字信号处理已经成为一门完整的学科。

其涉及到许多学科而又广泛应用于许多领域,20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。

数字信号处理是一种通过使用数学技巧执行转换或提取信息,来处理现实信号的方法,这些信号由数字序列表示。

而数字滤波器在这门学科中占有很重要的地位。

数字滤波器是一个离散时间系统(按预定的算法,将输入离散时间信号要求的输出离散时间信号的转换为所特定功能装置)。

应用数字滤波器处理模拟信号时,首先须对输入模拟信号进行限带、抽样和模数转换。

数字滤波器输入信号的抽样率应大于被处理信号带宽的两倍,其频率响应具有以抽样频率为间隔的周期重复特性,且以折叠频率即1/2抽样频率点呈镜像对称。

为得到模拟信号,数字滤波器处理的输出数字信号须经数模转换、平滑。

数字滤波器具有高精度、高可靠性、可程控改变特性或复用、便于集成等优点。

数字滤波器在语言信号处理、图像信号处理、医学生物信号处理以及其他应用领域都得到了广泛应用。

它涉及到的领域很广,如通信系统,系统控制,生物医学工程,机械振动,遥感遥测,地质勘探,故障检测,电力系统,航空航天,自动化仪器等。

数字滤波器的好坏对相关的众多工程技术领域影响很大,一个好的数字滤波器会有效的推动众多的工程技术领域改造和学科发展。

所以对数字滤波器的工作原理,硬件结构和实现方法进行研究具有一定的意义。

FPGA(Field-ProgrammableGateArray),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA采用了逻辑单元阵列LCA(LogicCellArray)这样一个概念,内部包括可配置逻辑模块CLB(ConfigurableLogicBlock)、输出输入模块IOB(InputOutputBlock)和内部连线(Interconnect)三个部分。

现场可编程门阵列(FPGA)是可编程器件。

与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构,FPGA利用小型查找表(16×

1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了即可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。

FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程.

1.2FPGA技术的发展及应用

FPGA正处于高速发展时期,新型芯片的规模越大,成本也越来越低,低端的FPGA已逐步取代了传统的数字元件,高端的FPGA将会成为今后竞争的主流。

自1985年问世以来,FPGA从集成电路与系统家族一个不起眼的小角色逐渐成为电子设计领域的重要器件。

它极大地提高了设计灵活性并缩短了产品上市时间,在通信、工业控制、航空领域中广泛应用。

FPGA行业集中度很高,几家美国公司掌握着行业的“制空权”。

特别是在航空航天及军工等特殊领域,美国等少数国家对先进的技术保持封锁。

因此,发展国内FPGA产业不是要不要的问题,而是怎么发展的问题。

国内IC企业介入FPGA的时间并不长,多数公司还处于学习阶段。

Altera公司和Xilinx公司为代表的FPGA厂商,除了在FPGA产品线上不断推陈出新之外,也在不懈地提高开发软件的设计能力,他们的软件产品在很多方面一点也不逊色于专业的EDA厂商,所以从这个角度来说,FPGA厂商也是EDA公司。

这里的代表性产品就是