选题3基于FPGA的计算器设计Word下载.doc

《选题3基于FPGA的计算器设计Word下载.doc》由会员分享,可在线阅读,更多相关《选题3基于FPGA的计算器设计Word下载.doc(16页珍藏版)》请在冰豆网上搜索。

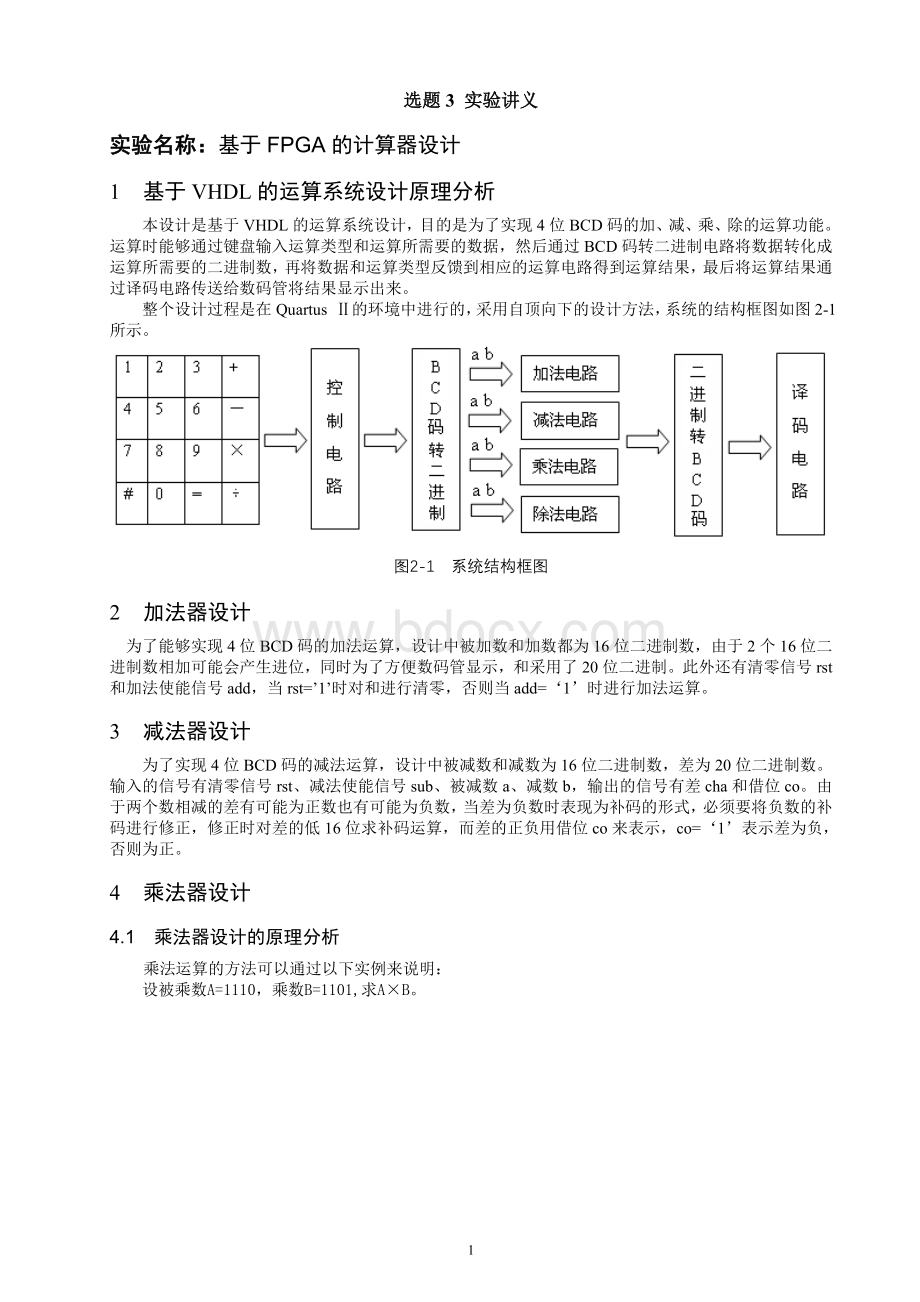

由以上实际例子可以看出,16位二进制乘法运算可以使用移位相加的方法来实现,被乘数左移16次,乘数右移16次,当时钟上升沿到来时都对乘数的最低位进行判断,如果乘数的最低位为1则乘积加上已经移位的被乘数,否则加0。

4.2乘法器电路结构框图

根据乘法原理,采用移位相加的办法来实现乘法运算,如图5-1。

图5-1乘法器设计结构框图

4.2.1乘法器控制电路设计

由于此次设计的是16位二进制乘法器电路,被乘数和乘数必须要移动16次,因此必须要使时钟信号只有16个脉冲。

控制电路采用计数的办法,当乘法运算使能信号mul=‘1’时,将计数值cnt16b清零,否则当cnt16b小于16时,cnt16b加1且cp等于clk;

否则cp等于0,这样就保证了cp输出只有16个脉冲。

关键的VHDL程序如下:

process(clk,mul)--描述了一个移位脉冲计数器,产生移位脉冲

begin

ifmul='

1'

thencnt16b<

="

00000"

;

elsifclk'

eventandclk='

then

ifcnt16b<

16thencnt16b<

=cnt16b+1;

endif;

endif;

endprocess;

process(clk,cnt16b,mul)

begin

ifmul='

0'

ifcnt16b<

16thencp<

=clk;

elsecp<

='

endif;

elsecp<

endif;

endprocess;

4.2.2乘数右移电路设计

乘数右移的目的是为了判断乘数的最低位是0还是1,如果为0则乘机加上移位后的被乘数,否则加上0。

process(clk,mul)

ifclk'

thenshifter16<

=multiplier;

--当mul='

装载入乘数

elseshifter16(14downto0)<

=shifter16(15downto1);

--将乘数右移一位

qb<

=shifter16(0);

4.2.3被乘数左移电路设计

被乘数左移在乘法运算中是必须的,根据乘法运算的原理,当乘数的最低位为‘1’时左移后的被乘数作为加法电路的一个加数。

当乘法运算使能信号mul为‘1’时,在被乘数前添加16个0,之后当脉冲到来的时候左移一位。

process(mul,clk)

ifmul='

thenseg8<

0000000000000000"

&

multiplicand;

--当mul='

在被乘数前添加16个0

elsifclk'

then

seg8(31downto1)<

=seg8(30downto0);

seg8(0)<

4.2.4加法电路

加法电路负责判断右移后的乘数的最低位是‘0’还是‘1’,如果是‘1’则将乘积和左移后的被乘数相加,否则加0。

当乘法运算使能信号mul为‘1’时,乘积初始化为0。

process(mul,clk)

ifmul='

thensum<

=(others=>

'

);

--当mul='

乘积清零

ifqb='

sum<

=sum+d;

4.3乘法器顶层设计

将控制电路、乘数右移电路、被乘数左移电路以及加法电路都打包后,采用原理图的方式将各个模块连接成顶层电路,顶层实体端口定义如图5-2。

图5-2乘法器顶层实体

端口信号说明:

clk:

时钟脉冲

mul:

乘法运算使能信号

a:

被乘数

b:

乘数

product:

乘积

乘法器顶层电路的连接图如图5-3。

图5-3乘法器顶层连接图

4.4波形仿真及结果分析

利用QUARTUSⅡ软件将乘法器电路的顶层电路运行后,进行时序仿真,仿真波形如图5-4。

图5-4乘法运算时序仿真波形

在波形仿真时设置被乘数a=9999,乘数b=998,从波形图可以看出,运算完成时的乘积为9979002这说明运算结果正确。

在mul=1,时候开始进行乘法运算,经过16个脉冲之后得到乘积,综上所述,4位BCD码乘法器电路已经设计完成。

5除法器的设计

5.1除法器设计原理分析

此次设计的16位二进制除法器采用的是比较相减的方法,先在被除数前添加16个0,当时钟脉冲上升沿到来时将前一次高16位与除数比较,若大于或等于则将被除数的高16位减去除数,同时左移并将被除数的第1位置1,若小于则只是将被除数左移,等到下一个脉冲到来时再循环此操作,直到第16个脉冲之后停止操作。

这样进行16个脉冲周期之后,被除数的高16位为余数,低16位为商。

除法运算的原理可以通过以下实例来说明:

设被除数A=1110,除数B=0110,求解A÷

B的过程如下:

5.2除法器电路结构框图

根据前面的算法分析,可知除法器设计要用到锁存器和移位寄存器,还有定时器判断运算过程。

设计框图如图6-1。

图6-1除法器电路结构图

除法器电路由控制电路、比较电路、减法电路和移位电路组成。

控制电路负责产生16个脉冲的时钟信号、转载信号、运算结束信号;

比较电路则是将被除数的高16位和除数进行比较,若大于或等于则great为‘1’,否则为‘0’;

减法电路先判断比较电路输出的great是否为‘1’,若为‘1’则将被除数的高16位和除数相减,否则不进行运算只保存被除数的高16位;

移位电路是将被除数进行左移,并对great进行判断,若为‘1’则将被除数的第一位置‘1’。

5.3除法器顶层设计

除法器顶层设计的端口信号定义如图6-2。

图6-2除法器电路顶层实体

信号说明:

clk:

:

系统时钟脉冲

load:

除法运算使能信号(即装载信号)

a:

被除数

b:

除数

q:

商

r:

余数

除法器顶层电路的连接图如图6-3。

图6-3除法器顶层连接图

5.4除法器波形仿真及结果分析

利用QUARTUSⅡ软件将除法器电路的顶层电路运行后,进行时序仿真,仿真波形如图6-4。

图6-4除法器时序仿真波形

在波形仿真时设置被除数a=9999,除数b=534,从波形图可以看出,运算完成时的商q为18,余数r为387,这说明运算结果正确。

在load=1,时候开始进行除法运算,经过16个脉冲之后得到商和余数,综上所述,4位BCD码除法器电路已经设计完成。

6键盘扫描电路设计

6.1矩阵式键盘的原理

矩阵式键盘是一种常见的输入装置,在日常生活中,矩阵式键盘在计算机、电话、手机等各式电子产品上已经被广泛应用[3]。

图7.1是一个4×

4矩阵式键盘的面板配置图,其中数字0~9作为各种运算的数字输入键,#为清零功能键,=为运算结果键,+、-、×

、÷

为运算的选择键。

键盘上的每一个按键其实就是一个开关,每个键都有一个上拉电阻,当某键按下时,该按键的接点会呈现低电平状态,反之,未按下时则呈现高电平状态。

图7-14×

4矩阵式键盘的面板配置

6.2扫描电路设计

6.2.1键盘扫描电路原理

对键盘采用0~15计数的方式,输入信号为键盘的列信号,对键盘进行逐行扫描。

扫描键盘的编码方式如图7-2,当没有按下键盘时,键盘输入到按键检测电路col的值均为1,此时key=‘1’;

否则当使用者按下键盘按钮时,键盘检测到按键电路col的值为0,此时key=‘0’[4]。

图7-2扫描键盘的编码方式

6.2.2键盘扫描电路组成

键盘扫描电路由键盘扫描计数器电路、键盘检测电路、键盘消抖动电路以及键盘编码电路组成。

6.3键盘扫描计数器电路

时钟信号clk频率为1KHz,按键(key_pressed)为使能信号,当未按下键盘时key_pressed=‘1’,此时由0~15反复计数,并将计数值作为按键检测电路的输入信号,直到按下键key_pressed=‘0’时计数器停止输出计数值。

扫描计数器电路的关键VHDL程序如下:

process(clk,key_pressed)

ifclk'

ifkey_pressed='

q<

=q+1;

6.4按键检测电路

按键检测电路的输入信号为col和scan_cnt,输出信号为row和key_pressed。

检测电路根据计数值scan_cnt判断row和key_pressed,scan_cnt的低2位用于判断扫描的列,scan_cnt的低2位“00”、“01”、“10”、“11”分别代表第一列、第二列、第三列、第四列;

而scan_cnt的高2位“00”、“01”、“10”、“11”分别代表第一行、第二行、第三行、第四行。

按键检测电路的关键VHDL程序如下:

row<

1110"

whenscan_cnt(3downto2)="

00"

else

"

1101"

01"

1011"

when