eda课程设计报告报告自动售货机的设计.docx

《eda课程设计报告报告自动售货机的设计.docx》由会员分享,可在线阅读,更多相关《eda课程设计报告报告自动售货机的设计.docx(13页珍藏版)》请在冰豆网上搜索。

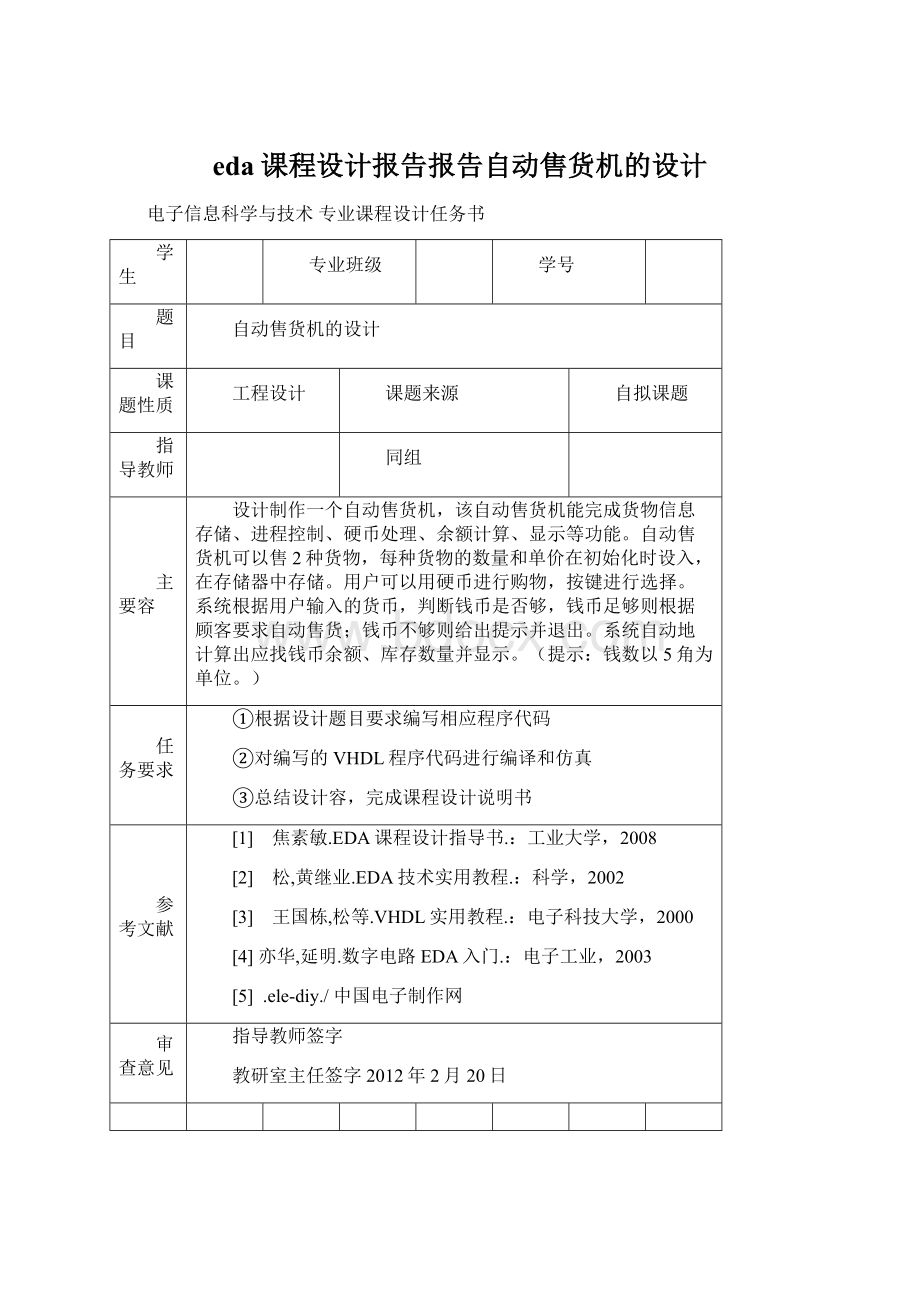

eda课程设计报告报告自动售货机的设计

电子信息科学与技术专业课程设计任务书

学生

专业班级

学号

题目

自动售货机的设计

课题性质

工程设计

课题来源

自拟课题

指导教师

同组

主要容

设计制作一个自动售货机,该自动售货机能完成货物信息存储、进程控制、硬币处理、余额计算、显示等功能。

自动售货机可以售2种货物,每种货物的数量和单价在初始化时设入,在存储器中存储。

用户可以用硬币进行购物,按键进行选择。

系统根据用户输入的货币,判断钱币是否够,钱币足够则根据顾客要求自动售货;钱币不够则给出提示并退出。

系统自动地计算出应找钱币余额、库存数量并显示。

(提示:

钱数以5角为单位。

)

任务要求

①根据设计题目要求编写相应程序代码

②对编写的VHDL程序代码进行编译和仿真

③总结设计容,完成课程设计说明书

参考文献

[1] 焦素敏.EDA课程设计指导书.:

工业大学,2008

[2] 松,黄继业.EDA技术实用教程.:

科学,2002

[3] 王国栋,松等.VHDL实用教程.:

电子科技大学,2000

[4]亦华,延明.数字电路EDA入门.:

电子工业,2003

[5].ele-diy./中国电子制作网

审查意见

指导教师签字

教研室主任签字2012年2月20日

一.设计说明

根据要求可自动出售两种货物,本文设计的自动售货机可销售cola和pepsi两种饮料:

售货机可识别1元和0.5元的两种货币,在一次购买过程中,可购买一个或多个商品,系统会自动计算所需钱数和找零的钱数并自动找零。

另外有3个发光二极管、6个LCD数码管:

两个用来显示所需金额,两个用来显示已付金额,两个用来显示找零数。

1.1.1流程说明

本文设计的自动售货机当通电时,表示一次销售的开始。

顾客选择一种商品或多种商品后就进入投币状态。

若不投币,则自动返回初始状态。

投币后,系统自动计算所投钱数。

若投币够,则出货并找零。

若投币不够,如果顾客没有继续投币,则退币并回到初始状态。

本系统的投币销售流程图如图所示:

1.1.2各模块说明

本文设计的自动售货机总体分三个模块:

总控模块,二进制译码模块、BCD码译码模块。

总控模块:

总控模块是本系统最重要的模块,该模块大体有5个输入端口和6个输出端口。

其输入端口包括clk、coin1(投入一元货币)、coin5(投入0.5元货币)、cola(选择cola)、pepsi(选择pepsi),输出端口有paid(已投入多少钱)、needed(还需多少钱)moneyout(找零)、success(灯亮表示交易成功)、failure(灯亮表示交易失败)、showmoneyout(灯亮表示正在找零)。

该模块实现了本系统最重要的交易过程,包括选择商品、投入货币,计算剩余金额,找零出货等。

二进制译码模块:

该模块有一个输入端口和两个输出端口。

输入端口是一个8位的二进制数输出端口bcd0、bcd1是两个4位的BCD码。

该模块的主要的功能是实现将主控模块输出的二进制数(paid、needed、moneyout)转换成BCD码,以便输出到七段数码管上显示出来。

该模块的原理是将一个8位的二进制转换成2个4位的BCD码,分为高四位和低四位。

BCD码译码模块:

该模块有一个输入端口和一个输出端口

1.1.3程序设计

主控模块完整程序如下:

Libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityshouhuojiis

port(clk:

instd_logic;

coin1:

instd_logic;

coin5:

instd_logic;

cola:

instd_logic;

pepsi:

instd_logic;

paid:

outstd_logic_vector(7downto0);

needed:

outstd_logic_vector(7downto0);

success:

outstd_logic;

failure:

outstd_logic;

showmoneyout:

outstd_logic;

moneyout:

outstd_logic_vector(7downto0));

endshouhuoji;

architecturebehavofshouhuojiis

typestate_typeis(qa,qb,qe,qc,qg,qd,qf);--定义七个状态

signalcurrent_state:

state_type:

=qa;

signalq:

integerrange0to100;

begin

process(clk)

variablepaidtemp:

std_logic_vector(7downto0);--定义变量

variableneededtemp:

std_logic_vector(7downto0);

variablebackmoney:

std_logic_vector(7downto0);

variablepricetemp:

std_logic_vector(7downto0);

begin

ifclk'eventandclk='1'then

casecurrent_stateis

whenqa=>paidtemp:

="00000000";neededtemp:

="00000000";

backmoney:

="00000000";pricetemp:

="00000000";q<=0;

showmoneyout<='0';moneyout<="00000000";paid<="00000000";

needed<="00000000";failure<='0';success<='0';

ifcola='1'orpepsi='1'thencurrent_state<=qb;

ifcola='1'thenpricetemp:

=pricetemp+"00001111";

neededtemp:

=pricetemp;

Else

pricetemp:

=pricetemp+"00010100";

neededtemp:

=pricetemp;

endif;

endif;

paid<=paidtemp;

needed<=neededtemp;

whenqb=>ifcoin1='1'orcoin5='1'then

ifcoin1='1'thenpaidtemp:

=paidtemp+"00001010";

else

paidtemp:

=paidtemp+"00000101";

endif;

ifpaidtemp>=pricetempthenbackmoney:

=paidtemp-pricetemp;

neededtemp:

="00000000";current_state<=qd;

elseneededtemp:

=pricetemp-paidtemp;backmoney:

="00000000";

current_state<=qc;q<=0;

endif;

paid<=paidtemp;

needed<=neededtemp;

endif;

ifq<8thenq<=q+1;

ifcola='1'orpepsi='1'thenq<=0;

ifcola='1'thenpricetemp:

=pricetemp+"00001111";

neededtemp:

=neededtemp+"00001111";

else

pricetemp:

=pricetemp+"00010100";

neededtemp:

=neededtemp+"00010100";

endif;

paid<=paidtemp;

needed<=neededtemp;

endif;

elsecurrent_state<=qe;q<=0;

endif;

whenqe=>failure<='1';

ifq<4thenq<=q+1;

elsecurrent_state<=qa;q<=0;

endif;

whenqc=>ifcoin1='1'orcoin5='1'then

ifcoin1='1'thenpaidtemp:

=paidtemp+"00001010";

else

paidtemp:

=paidtemp+"00000101";

endif;

ifpaidtemp>=pricetempthen

backmoney:

=paidtemp-pricetemp;

neededtemp:

="00000000";current_state<=qd;

elseneededtemp:

=pricetemp-paidtemp;backmoney:

="00000000";

current_state<=qc;

endif;

paid<=paidtemp;

needed<=neededtemp;

endif;

ifcoin1/='1'andcoin5/='1'then

ifq<10thenq<=q+1;

elsecurrent_state<=qg;

endif;

elseq<=0;

endif;

whenqg=>failure<='1';

showmoneyout<='1';moneyout<=paidtemp;

current_state<=qf;q<=0;

success<='0';

whenqd=>success<='1';

ifbackmoney>"00000000"thenshowmoneyout<='1';

moneyout<=backmoney;

endif;

current_state<=qf;q<=0;

whenqf=>ifq<4thenq<=q+1;

elsecurrent_state<=qa;q<=0;

endif;

endcase;

else

endif;

endprocess;

endbehav;

BCD译码模块完整程序如下:

Libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitycode1is

port(

b:

instd_logic_vector(7downto0);

bcd0:

outstd_logic_vector(3downto0);

bcd1:

outstd_logic_vector(3downto0)

);

endcode1;

architectureoneofcode1is

begin

process(b)

begin

casebis

when"00000000"=>bcd0<="0000";bcd1<="0000";--译码“0”;

when"00000001"=>bcd0<="0001";bcd1<="0000";--译码“1”;

when"00000010"=>bcd0<="001