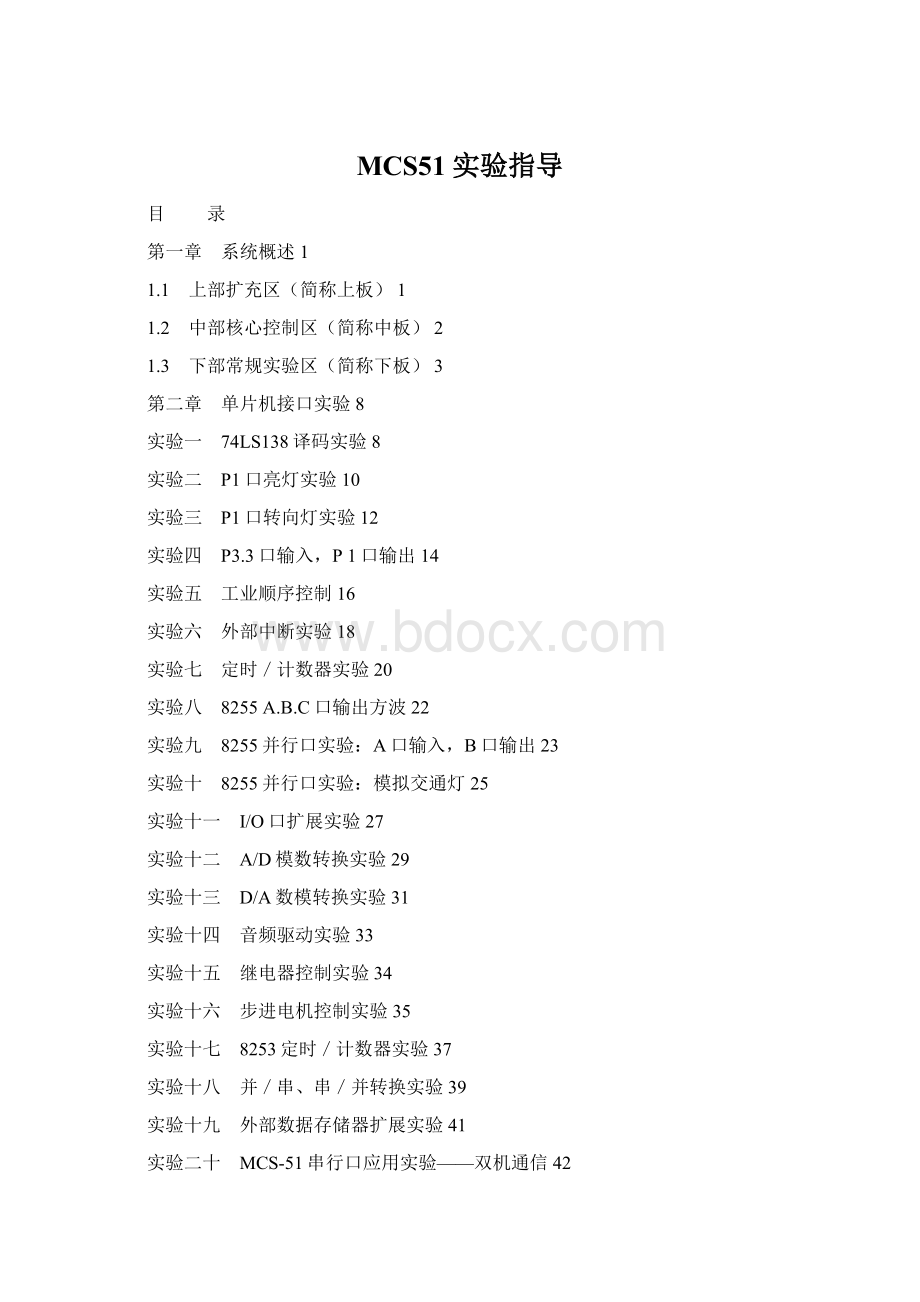

MCS51实验指导Word格式文档下载.docx

《MCS51实验指导Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《MCS51实验指导Word格式文档下载.docx(71页珍藏版)》请在冰豆网上搜索。

实验十 8255并行口实验:

模拟交通灯25

实验十一 I/O口扩展实验27

实验十二 A/D模数转换实验29

实验十三 D/A数模转换实验31

实验十四 音频驱动实验33

实验十五 继电器控制实验34

实验十六 步进电机控制实验35

实验十七 8253定时/计数器实验37

实验十八 并/串、串/并转换实验39

实验十九 外部数据存储器扩展实验41

实验二十 MCS-51串行口应用实验——双机通信42

实验二十一 MCS-51串行口应用实验——与PC通信43

实验二十二 DS18B20数字温度传感器实验45

实验二十三 DS18B20温度闭环实验46

实验二十四 直流电机调速实验48

实验二十五 LED16×

16点阵显示实验50

实验二十六 8255键盘显示实验52

实验二十七 LCD128×

64液晶显示实验54

实验二十八 逻辑加密IC存储卡读写实验55

实验二十九 8251串行通信实验61

实验三十 8259中断控制实验63

实验三十一 串行A/D转换实验65

实验三十二 串行D/A转换实验66

实验三十三 红外遥控实验67

实验三十四 V/F转换实验68

实验三十五 PWM转换实验70

实验三十六 AT24C02串行存储器实验71

实验三十七 X5045P看门狗实验72

实验三十八 DS1302实时时钟实验73

实验三十九 微型打印机实验74

实验四十 RS485差分串行通信实验75

实验四十一 CAN-bus现场总线控制实验77

实验四十二 基于以太网接口的TCP/IP实验79

实验四十三 USB通用串行总线实验85

第一章 系统概述

DTHS-A是由山东理工大学、淄博耐思科技有限公司设计制造的单片机与微机接口通用型实验台,它以常规实验设备的开放式实验环境为基础,增加了在线检测模式,在自定义环节融入轨迹捕捉,影射和展现实验电路搭接的全过程,为互动教学活动的展开创造了一个较为完整与规范的实践平台。

DTHS-A实验台由三个部分组成:

上部为实验台扩充区,适用于课程设计及实验电路与模块的扩展;

中部为实验台核心控制区,主要由通用仿真器、在线控制器、轨迹捕捉器及机电与单总线等实验模块组成;

下部为实验台常规实验区,适用于基础性教学实践活动。

DTHS-A实验台支持NICE自主研发的集成开发环境,并与KEIL/MPLAB/AVRStudio等主流开发环境无缝结合。

1.1 上部扩充区(简称上板)

1)直流电压表

上板右上角配有数字式直流电压表,其量程为±

20V;

电压表左测的钮子开关用于选择电压表的检测来源。

①信号源测量

该钮子开关拨向“外”方向时,位于电压表下方的红孔为电压表输入端(+20V~-20V),其黑孔为电压表直流地端(非负极性输入端),该端与本工位的“GND”己连接互通,仅适用于实验台二工位之间GND的并端,不允许加载负极性或与“GND”相冲突的信号源;

②内置源监视

该钮子开关拨向“内”方向时,由位于钮子开关上方的2×

3波段开关选择与确认当前监视源。

我们强调监视源的选择应在掉电方式下进行,即在关闭直流源的前提下才能拨动波段开关选择当前监视源,否则会引发+5V、+12V、-12V之间的瞬间短接,对低压供电器件的损伤率极高,亦危及开关电源的寿命。

2)微型打印机

上板偏左上方配有智能窗式针型打印机,位于钮子开关下方的双排八芯座为它的总线口,“STB”孔为打印命令控制端,“BUSY”为打印机忙闲标志,“ERR”为打印机出错标志。

3)逻辑加密存储卡

存储卡正下方为该卡读写加密控制端,该卡左边为插卡口,该卡右边定义状态标志指示。

4)CPLD扩展

上板右下方为CPLD逻辑控制器设计与实践区域,选用XilinxXC9572为硬布线控制器,配有下载口,用符合Xilinx标准的下载电缆即可实现针对XC9572的逻辑设计与编程。

5)扩充区

上板左下方为自行设计区域,该区域正下方为阻容件、晶体、三极管、二极管扩充区,该区域左上方为门电路、运放等IC-14以下芯片及集成电阻的扩充区,该区域右上方为IC-40以下集成器件扩充区。

1.2 中部核心控制区(简称中板)

1)CPU单元

中板左上方为实验台CPU选择单元,目前可适配的CPU类型有MCS-51/PIC单片机、以8088为内核的微机接口。

2)总线接口

①数据总线:

双向,来源于仿真器。

当CPU单元挂51时,它是由P0口隔离驱动后形成双向总线。

②地址总线:

输出,来源于仿真器。

当CPU单元挂51时,它的低八位由P0口驱动锁存输出;

它的高八位由P2口隔离驱动输出。

③控制总线

●RD:

当CPU单元挂51时为外部数据读,受P3.7控制

●WD:

当CPU单元挂51时为外部数据写,受P3.6控制

●ALE:

当CPU单元挂51时为地址锁存,受51_ALE控制

●RESET:

复位输出,高电平有效,受仿真器复位电路控制

●MER:

当CPU单元挂88时为内存读,受8088CPU控制

●MEW:

当CPU单元挂88时为内存写,受8088CPU控制

●AEN:

输入,总线出借控制。

当CPU单元挂88时为DMA操作,受8237_AEN控制

●φ:

时钟输出,当CPU单元挂51时,由51CPU第18脚提供

3)并行模块

①LCD液晶显示

其数据线与总线接口中的D7~D0己连接互通,总线连接定义为省缺项。

位于LCD正下方的使能控制端“E”,命令与数据选择端“R/S”及读写选择端“R/W”在自行设计状态定义为实验连接项。

②8255并行口

其数据线与仿真器中的D7~D0己连接互通,总线连接定义为省缺项。

位于8255正右测的“CS”为8255选通控制端。

位于LCD正下方的add1~add0为8255地址端A1~A0,位于下板“直流源指示”上方的RD、WR为8255读写控制端,在自行定义状态它们为实验连接项。

4)单总线模块

单总线模块超越并行总线的寻址规则,局限于I/O端口寻址,不宜在线掌控,只能工作在自定义状态,因此在单总线模块的设计与实现中实验连接项不可省缺。

5)闭环控制

①直流电机

直流电机控制单元定义了“调速”与“测速”两个端口,其中调速端为电机启停。

正反转及转速控制端,它加载的模拟量范围是0~5V,2.5V时电机处停止状态,大于2.5V启动电机正转,小于2.5V启动电机反转,该端达5V或0V时电机处正转或反转最高速。

至于测速端是电机当前状态与转速的反馈端,为电机按设置的参数恒定运作提供依据。

在自行设计状态该两个端口定义为实验连接项。

②温度控制

温度控制单元定义了“调温”与“测温”两个端口,其中调温端口由5V电源控制,至于测温端口是当前温度传递端口,反馈温度参数,为加温与恒温提供依据。

6)步进电机

步进电机控制单元设有四拍控制端口,在自行设计状态该四端口定义为实验连接项。

7)虚拟示波器

实验台提供了一个双通道简易示波器,适用于电位及赫兹级低频信号的测量与观察。

8)扁平链接口

中板下方设有五个扁平链接口,其中二个20芯扁平口为检测口,其余三个8芯扁平口为地址与数据总线延伸接口。

1.3 下部常规实验区(简称下板)

1)下板接口

①检测接口

下板上方二个20芯扁平口为检测口,“在线”态它为控制口,输出常规实验模块的控制信号。

在自定义状态它为状态口,反馈常规实验模块的控制信号。

②总线接口

下板上方三个8芯扁平口为地址与数据总线链接口,该三个接口是主控区(中板)扩展寻址的桥梁,面向下板实验时必须连接。

2)下板总线

①控制线

位于“直流源指示”上方的为下板自定义状态的公共控制总线,以下为它们的定义:

●CLR下板区域淸除控制,在自定义实验中连接中板RESET复位信号。

●WR下板区域写控制,在自定义实验中连接中板控制总线单元WR写信号。

●RD下板区域读控制,在自定义实验中连接中板控制总线单元RD读信号。

●CLK下板区域锁存控制,在自定义实验中连接中板ALE信号。

②地址线

位于“存储器扩展单元”左下测的ADD2~ADD0为下板区域公共地址线,在自定义实验中通常连接中板A2~A0。

遇单模块实验可另行定义,例如0809A/D转换中ADD2~ADD0用于选择通道,可改接中板地址总线单元A2~A0。

③译码器

位于“发光二极管显示单元”正下方的138译码器亦有二种定义途径,“在线”态实验台赋于的定义是译码端口CBA与A5~A3相连,选通控制端口G2A(低电平有效)由A14控制,当A14为零时,138输出端Y7~Y0八中选一,有一个输出端为“0”,其余输出端为“1”。

它的寻址范围为0~3FFFh,8000h~BFFFh。

在自定义方式其选通与译码端口呈悬浮态,属译码控制不可省缺的连接项。

3)存储器扩展

位于下板右上角为“存储器扩展单元”,它的地址与数据总线通过其上方的三个8芯扁平接口融入中板主控CPU的寻址范围,位于该单元左上测的MR、MW及MCS分别为存储器读、写和选通控制端。

自定义态属实验不可省缺的连接项。

在线态由在线控制器掌控,寻址范围为0~0FFFh。

这里需要提示的是不同类型CPU对于并行存储器扩展有其完全不同的寻址路径,中板挂51CPU时,存储器与I/O处同一寻址空间,用相同的控制信号,通常采用译码法分享数据寻址空间;

当挂8088CPU时,存储器与I/O处不同的寻址空间,用不同的控制信号,编各自的指令实现当前的寻址操作。

4)I/O口扩展

①16×

16点阵

16×

16点阵位于“存储器扩展单元”正下方,它的数据总线通过8芯扁平接口(下板上右一)与中板总线单元的D7~D0连接互通,“存储器扩展单元”左下测的ADD1~ADD0定义行与列口地址。

16S为点阵写选通控制,自定义态属实验不可省缺的连接项。

在线态由在线控制器掌控,寻址范围为0ECH~0EFH。

②键盘与八段显示

实验台选用8255为并行键盘与显示接口,定义其A口为字形口,B口为字位与键扫口,PC2~PC0为键入口。

位于并行键盘与显示扩展板左则的8255CS为8255选通控制,它的数据总线通过8芯扁平接口(下板上右一)与中板总线单元的D7~D0连接互通,“存储器扩展单元”左下测的ADD1~ADD0定义其地址线A1~A0,“串并转换单元”右边的RD、WR定义其读写控制信号,自定义态属实验不可省缺的连接项。

在线态由在线控制器掌控,寻址范围为0DCH~0DFH。

③简易I/O

实验台选用244为简易I/O缓冲输入器件,该单元“G”为读选通控制,自定义态属实验不可省缺的连接项。

该单元“PI7~PI0”为八位缓冲输入端口。

实验台选用273为简易I/O锁存输出器件,该单元“CLK”为锁存触发端,自定义态属实验不可省缺的连接项。

该单元“PO7~PO0”为八位锁存输出端口。

④A/D与D/A

并行A/D转换器0809位于“调模拟