导体存储器Word格式文档下载.docx

《导体存储器Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《导体存储器Word格式文档下载.docx(18页珍藏版)》请在冰豆网上搜索。

随机存取存储器简称RAM,也叫做读/写存储器,既能方便地读出所存数据,又能随时写入新的数据。

RAM的缺点是数据的易失性,即一旦掉电,所存的数据全部丢失。

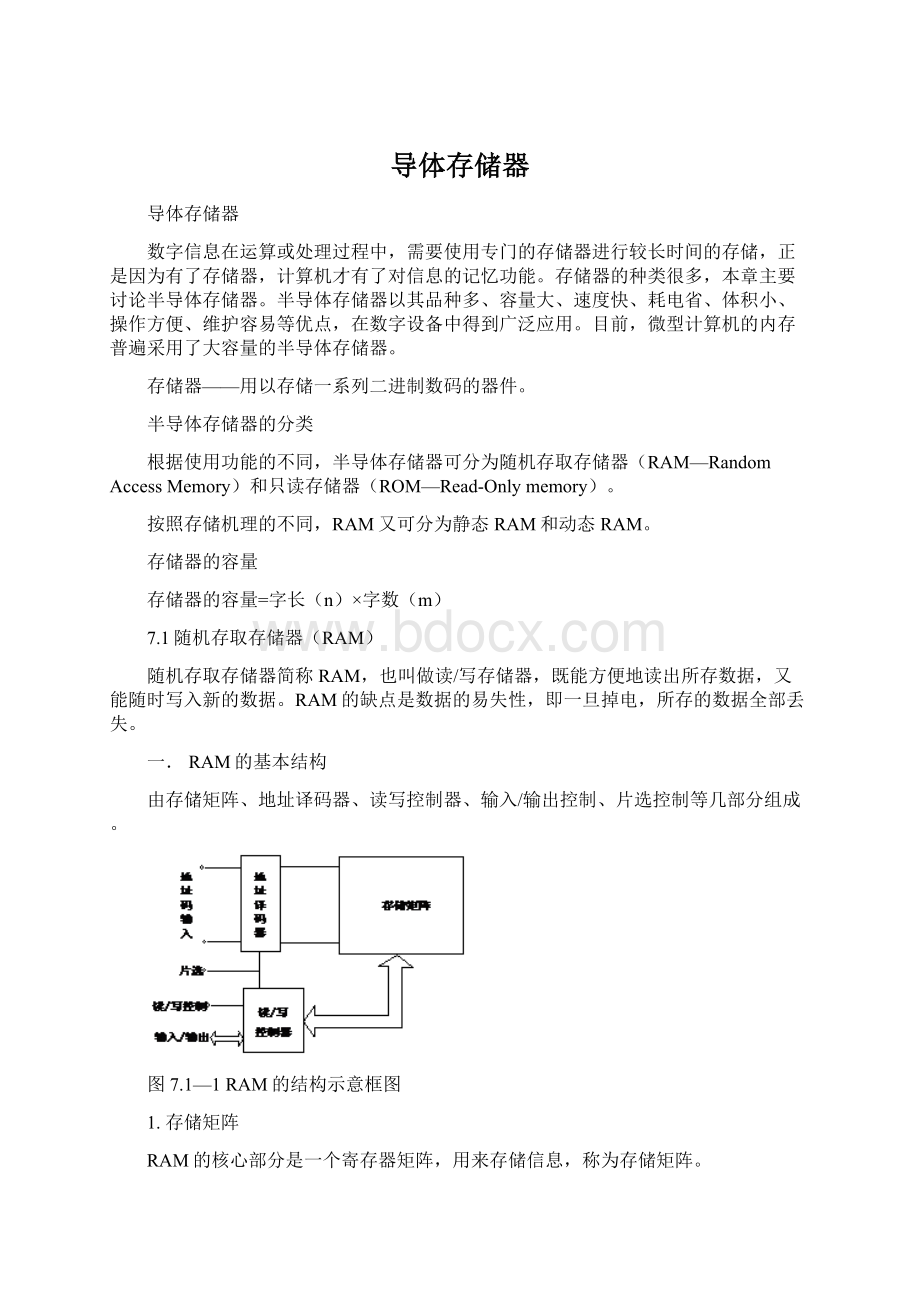

一.RAM的基本结构

由存储矩阵、地址译码器、读写控制器、输入/输出控制、片选控制等几部分组成。

图7.1—1RAM的结构示意框图

1.存储矩阵

RAM的核心部分是一个寄存器矩阵,用来存储信息,称为存储矩阵。

图7.1—5所示是1024×

1位的存储矩阵和地址译码器。

属多字1位结构,1024个字排列成32×

32的矩阵,中间的每一个小方块代表一个存储单元。

为了存取方便,给它们编上号,32行编号为X0、X1、…、X31,32列编号为Y0、Y1、…、Y31。

这样每一个存储单元都有了一个固定的编号(Xi行、Yj列),称为地址。

图7.1-51024×

1位RAM的存储矩阵

2.址译码器

址译码器的作用,是将寄存器地址所对应的二进制数译成有效的行选信号和列选信号,从而选中该存储单元。

存储器中的地址译码器常用双译码结构。

上例中,行地址译码器用5输入32输出的译码器,地址线(译码器的输入)为A0、A1、…、A4,输出为X0、X1、…、X31;

列地址译码器也用5输入32输出的译码器,地址线(译码器的输入)为A5、A6、…、A9,输出为Y0、Y1、…、Y31,这样共有10条地址线。

例如,输入地址码A9A8A7A6A5A4A3A2A1A0=0000000001,则行选线X1=1、列选线Y0=1,选中第X1行第Y0列的那个存储单元。

从而对该寄存器进行数据的读出或写入。

3.读/写控制

访问RAM时,对被选中的寄存器,究竟是读还是写,通过读/写控制线进行控制。

如果是读,则被选中单元存储的数据经数据线、输入/输出线传送给CPU;

如果是写,则CPU将数据经过输入/输出线、数据线存入被选中单元。

一般RAM的读/写控制线高电平为读,低电平为写;

也有的RAM读/写控制线是分开的,一根为读,另一根为写。

4.输入/输出

RAM通过输入/输出端与计算机的中央处理单元(CPU)交换数据,读出时它是输出端,写入时它是输入端,即一线二用,由读/写控制线控制。

输入/输出端数据线的条数,与一个地址中所对应的寄存器位数相同,例如在1024×

1位的RAM中,每个地址中只有1个存储单元(1位寄存器),因此只有1条输入/输出线;

而在256×

4位的RAM中,每个地址中有4个存储单元(4位寄存器),所以有4条输入/输出线。

也有的RAM输入线和输出线是分开的。

RAM的输出端一般都具有集电极开路或三态输出结构。

5.片选控制

由于受RAM的集成度限制,一台计算机的存储器系统往往是由许多片RAM组合而成。

CPU访问存储器时,一次只能访问RAM中的某一片(或几片),即存储器中只有一片(或几片)RAM中的一个地址接受CPU访问,与其交换信息,而其他片RAM与CPU不发生联系,片选就是用来实现这种控制的。

通常一片RAM有一根或几根片选线,当某一片的偏选线接入有效电平时,该片被选中,地址译码器的输出信号控制该片某个地址的寄存器与CPU接通;

当片选线接入无效电平时,则该片与CPU之间处于断开状态。

6.RAM的输入/输出控制电路

图7.1—2给出了一个简单的输入/输出控制电路。

图7.1—2输入/输出控制电路

当选片信号CS=1时,G5、G4输出为0,三态门G1、G2、G3均处于高阻状态,输入/输出(I/O)端与存储器内部完全隔离,存储器禁止读/写操作,即不工作。

当CS=0时,芯片被选通:

当=1时,G5输出高电平,G3被打开,于是被选中的单元所存储的数据出现在I/O端,存储器执行读操作;

当=0时,G4输出高电平,G1、G2被打开,此时加在I/O端的数据以互补的形式出现在内部数据线上,并被存入到所选中的存储单元,存储器执行写操作。

7.RAM的工作时序

为保证存储器准确无误地工作,加到存储器上的地址、数据和控制信号必须遵守几个时间边界条件。

图7.1—3示出了RAM读出过程的定时关系。

读出操作过程如下:

(1)欲读出单元的地址加到存储器的地址输入端;

(2)加入有效的选片信号CS;

(3)在线上加高电平,经过一段延时后,所选择单元的内容出现在I/O端;

(4)让选片信号CS无效,I/O端呈高阻态,本次读出过程结束。

由于地址缓冲器、译码器及输入/输出电路存在延时,在地址信号加到存储器上之后,必须等待一段时间tAA,数据才能稳定地传输到数据输出端,这段时间称为地址存取时间。

如果在RAM的地址输入端已经有稳定地址的条件下,加入选片信号,从选片信号有效到数据稳定输出,这段时间间隔记为tACS。

显然在进行存储器读操作时,只有在地址和选片信号加入,且分别等待tAA和tACS以后,被读单元的内容才能稳定地出现在数据输出端,这两个条件必须同时满足。

图中tRC为读周期,他表示该芯片连续进行两次读操作必须的时间间隔。

图7.1—3RAM读操作时序图

写操作的定时波形如图7.1—4所示。

写操作过程如下:

(1)将欲写入单元的地址加到存储器的地址输入端;

(2)在选片信号CS端加上有效电平,使RAM选通;

(3)将待写入的数据加到数据输入端;

(4)在线上加入低电平,进入写工作状态;

(5)使选片信号无效,数据输入线回到高阻状态。

由于地址改变时,新地址的稳定需要经过一段时间,如果在这段时间内加入写控制信号(即变低),就可能将数据错误地写入其他单元。

为防止这种情况出现,在写控制信号有效前,地址必须稳定一段时间tAS,这段时间称为地址建立时间。

同时在写信号失效后,地址信号至少还要维持一段写恢复时间tWR。

为了保证速度最慢的存储器芯片的写入,写信号有效的时间不得小于写脉冲宽度tWP。

此外,对于写入的数据,应在写信号tDW时间内保持稳定,且在写信号失效后继续保持tDH时间。

在时序图中还给出了写周期tWC,它反应了连续进行两次写操作所需要的最小时间间隔。

对大多数静态半导体存储器来说,读周期和写周期是相等的,一般为十几到几十ns。

图7.1—4RAM写操作时序图

二.RAM的存储单元

存储单元是存储器的核心部分。

按工作方式不同可分为静态和动态两类,按所用元件类型又可分为双极型和MOS型两种,因此存储单元电路形式多种多样。

1、六管NMOS静态存储单元

由六只NMOS管(T1~T6)组成。

T1与T2构成一个反相器,T3与T4构成另一个反相器,两个反相器的输入与输出交叉连接,构成基本触发器,作为数据存储单元。

T1导通、T3截止为0状态,T3导通、T1截止为1状态。

T5、T6是门控管,由Xi线控制其导通或截止,他们用来控制触发器输出端与位线之间的连接状态。

T7、T8也是门控管,其导通与截止受Yi线控制,他们是用来控制位线与数据线之间连接状态的,工作情况与T5、T6类似。

但并不是每个存储单元都需要这两只管子,而是一列存储单元用两只(见图7.1-3)。

所以,只有当存储单元所在的行、列对应的Xi、Yi线均为1时,该单元才与数据线接通,才能对它进行读或写,这种情况称为选中状态。

图7.1-6六管NMOS静态存储单元

2.双极型晶体管存储单元

图7.1-8是一个双极型晶体管存储单元电路,它用两只多发射极三极管和两只电阻构成一个触发器,一对发射极接在同一条字线上,另一对发射极分别接在位线B和上。

在维持状态,字线电位约为0.3V,低于位线电位(约1.1V),因此存储单元中导通管的电流由字线流出,而与位线连接的两个发射结处于反偏状态,相当于位线与存储器断开。

处于维持状态的存储单元可以是T1导通、T2截止(称为0状态),也可以是T2导通、T1截止(称为1状态)。

当单元被选中时,字线电位被提高到2.2V左右,位线的电位低于字线,于是导通管的电流转而从位线流出。

如果要读出,只要检测其中一条位线有无电流即可。

例如可以检测位线,若存储单元为1状态,则T2导通,电流由线流出,经过读出放大器转换为电压信号,输出为1;

若存储单元为0状态,则T2截止,线中无电流,读出放大器无输入信号,输出为0。

如果要写入1,则存储器输入端的1信号通过写入电路使B=1、=0,将位线B切断(无电流),迫使T1截止,T2导通,T2的电流由位线流出。

当字线恢复到低电平后,T2电流再转向字线,而存储单元状态不变,这样就完成了写1;

若要写0,则令B=0,=1,使位线切断,迫使T2截止、T1导通。

图7.1—8双极型晶体管存储单元

3.四管动态MOS存储单元

动态MOS存储单元存储信息的原理,是利用MOS管栅极电容具有暂时存储信息的作用。

由于漏电流的存在,栅极电容上存储的电荷不可能长久保持不变,因此为了及时补充漏掉的电荷,避免存储信息丢失,需要定时地给栅极电容补充电荷,通常把这种操作称作刷新或再生。

图7.1—9所示是四管动态MOS存储单元电路。

T1和T2交叉连接,信息(电荷)存储在C1、C2上。

C1、C2上的电压控制T1、T2的导通或截止。

当C1充有电荷(电压大于T1的开启电压),C2没有电荷(电压小于T2的开启电压)时,T1导通、T2截止,我们称此时存储单元为0状态;

当C2充有电荷,C1没有电荷时,T2导通、T1截止,我们则称此时存储单元为1状态。

T3和T4是门控管,控制存储单元与位线的连接。

T5和T6组成对位线的预充电电路,并且位一列中所有存储单元所共用。

在访问存储器开始时,T5和T6栅极上加“预充”脉冲,T5、T6导通,位线B和被接到电源VDD而变为高电平。

当预充脉冲消失后,T5、T6截止,位线与电源VDD断开,但由于位线上分布电容CB和的作用,可使位线上的高电平保持一段时间。

在位线保持为高电平期间,当进行读操作时,X线变为高电平,T3和T4导通,若存储单元原来为0态,即T1导通、T2截止,G2点为低电平,G1点为高电平,此时CB通过导通的T3和T1放电,使位线B变为低电平,而由于T2截止,虽然此时T4导通,位线仍保持为高电平,这样就把存储单元的状态读到位线B和上。

如果此时Y线亦为高电平,则B、的信号将通过数据线被送至RAM的输出端。

位线的预充电电路起什么作用呢?

在T3、T4导通期间,如果位线没有事先进行预充电,那么位线的高电平只能靠C1通过T4对充电建立,这样C1上将要损失掉一部分电荷。

由于位线上连接的元件较多,甚至比C1还要大,这就有可能在读一次后便破坏了G1的高电平,是存储的信息丢失。

采用了预充电电路后,由于位线的电位比G1的电位还要高一些,所以在读出时,C1上的电荷不但不会损失,反而还会通过T4对C1再充电,使C1上的电荷得到补充,即进行一次刷新。

当进行写操作时,RAM的数据输入端通过数据线、位线控制存储单元改变状态,把信息存入其中。

图7.1—9四管动态MOS存储单元

三.RAM的容量扩展

在实际应用中,经常需要大容量的RAM。

在单片RAM芯片容量不能满足要求时,就需要进行扩展,将多片RAM组合起来,构成存储器系统(也称存储体)。

1.位扩