arm协处理器Word文件下载.docx

《arm协处理器Word文件下载.docx》由会员分享,可在线阅读,更多相关《arm协处理器Word文件下载.docx(15页珍藏版)》请在冰豆网上搜索。

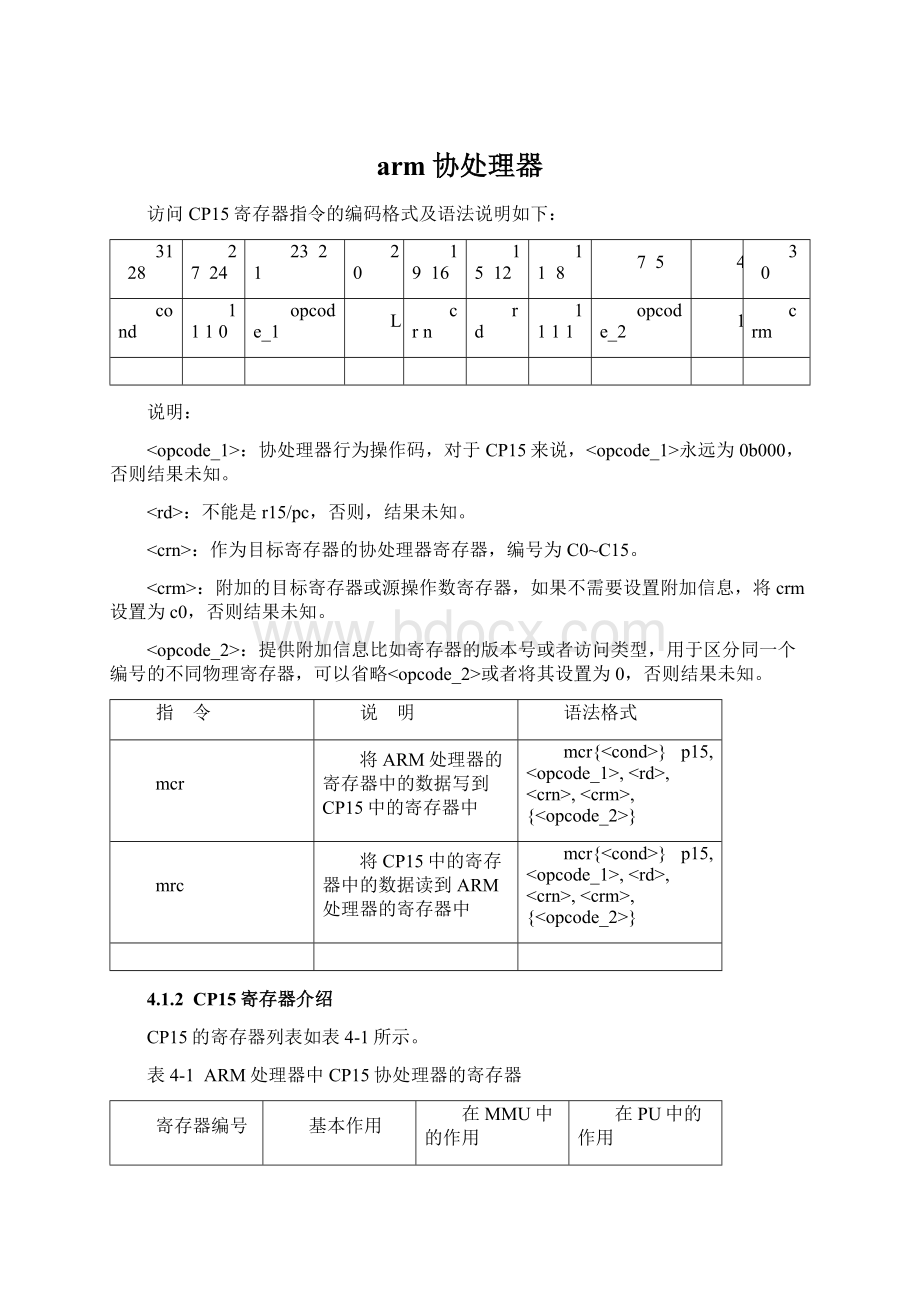

:

协处理器行为操作码,对于CP15来说,<

永远为0b000,否则结果未知。

rd>

不能是r15/pc,否则,结果未知。

crn>

作为目标寄存器的协处理器寄存器,编号为C0~C15。

crm>

附加的目标寄存器或源操作数寄存器,如果不需要设置附加信息,将crm设置为c0,否则结果未知。

opcode_2>

提供附加信息比如寄存器的版本号或者访问类型,用于区分同一个编号的不同物理寄存器,可以省略<

或者将其设置为0,否则结果未知。

指

令

说

明

语法格式

mcr

将ARM处理器的寄存器中的数据写到CP15中的寄存器中

mcr{<

cond>

}

p15,<

<

{<

}

mrc

将CP15中的寄存器中的数据读到ARM处理器的寄存器中

4.1.2

CP15寄存器介绍

CP15的寄存器列表如表4-1所示。

表4-1

ARM处理器中CP15协处理器的寄存器

寄存器编号

基本作用

在MMU中的作用

在PU中的作用

ID编码(只读)

ID编码和cache类型

控制位(可读写)

各种控制位

2

存储保护和控制

地址转换表基地址

Cachability的控制位

3

域访问控制位

Bufferablity控制位

保留

5

内存失效状态

访问权限控制位

6

内存失效地址

保护区域控制

7

高速缓存和写缓存

高速缓存和写缓存控制

8

TLB控制

9

高速缓存锁定

10

TLB锁定

11

12

13

进程标识符

14

15

因不同设计而异

∙CP15的寄存器C0

CP15中寄存器C0对应两个标识符寄存器,由访问CP15中的寄存器指令中的<

指定要访问哪个具体物理寄存器,<

与两个标识符寄存器的对应关系如下所示:

opcode_2编码

对应的标识符号寄存器

0b000

主标识符寄存器

0b001

cache类型标识符寄存器

其他

1)主标识符寄存器

访问主标识符寄存器的指令格式如下所示:

mrcp15,0,r0,c0,c0,0

;

将主标识符寄存器C0,0的值读到r0中

ARM不同版本体系处理器中主标识符寄存器的编码格式说明如下。

ARM7之后处理器的主标识符寄存器编码格式如下所示:

24

20

19

16

4

3

由生产商确定

产品子编号

ARM体系版本号

产品主编号

处理器版本号

位

位[3:

0]

生产商定义的处理器版本号

位[15:

4]

生产商定义的产品主编号,其中最高4位即位[15:

12]可能的取值为0~7但不能是0或7

位[19:

16]

ARM体系的版本号,可能的取值如下:

0x1

ARM体系版本4

0x2

ARM体系版本4T

0x3

ARM体系版本5

0x4

ARM体系版本5T

0x5

ARM体系版本5TE

其他

由ARM公司保留将来使用

位[23:

20]

生产商定义的产品子编号,当产品主编号相同时,使用子编号来区分不同的产品子类,如产品中不同的高速缓存的大小等

位[31:

24]

生产厂商的编号,现在已经定义的有以下值:

0x41

=A

ARM公司

0x44

=D

DigitalEquipment公司

0x69

=I

intel公司

ARM7处理器的主标识符寄存器编码格式如下所示:

22

16

15

A

12]的值为0x7

位[22:

续表

位[23]

ARM7支持下面两种ARM体系的版本号:

0x0

ARM体系版本3

Intel公司

ARM7之前处理器的主标识符寄存器编码格式如下所示:

23

16

生产商定义的产品主编号,其中最高4位即为[15:

2)cache类型标识符寄存器

访问cache类型标识符寄存器的指令格式如下所示:

mrcp15,0,r0,c0,c0,1

将cache类型标识符寄存器C0,1的值读到r0中

ARM处理器中cache类型标识符寄存器的编码格式如下所示:

29

28

25

12

11

0

0

属性字段

S

数据cache相关属性

指令cache相关属性

说明

位[28:

25]

指定控制字段位[24:

0]指定的属性之外的cache的其他属性,详见表4-2

位[24]

定义系统中的数据cache和指令cache是分开的还是统一的:

系统的数据cache和指令cache是统一的;

1

系统的数据cache和指令cache是分开的

12]

定义数据cache的相关属性,如果位[24]为0,本字段定义整个cache的属性

定义指令cache的相关属性,如果位[24]为0,本字段定义整个cache的属性

其中控制字段位[28:

25]的含义说明如下:

表4-2

cache类型标识符寄存器的控制字段位[28:

25]

编

码

cache类型

cache内容清除方法

cache内容锁定方法

0b0000

写通类型

不需要内容清除

不支持内容锁定

0b0001

写回类型

数据块读取

0b0010

由寄存器C7定义

0b0110

支持格式A

0b0111

支持格式B

控制字段位[23:

12]和控制字段位[11:

0]的编码格式相同,含义如下所示:

9

8

6

5

2

1

cache容量

cache相联特性

M

块大小

cache容量字段bits[8:

6]的含义如下所示:

M=0时含义(单位KB)

M=1时含义(单位KB)

0.5

0.75

1.5

0b010

0b011

0b100

0b101

16

24

0b110

32

48

0b111

64

96

cache相联特性字段bits[5:

3]的含义如下所示:

M=0时含义

M=1时含义

1路相联(直接映射)

没有cache

2路相联

3路相联

4路相联

6路相联

8路相联

12路相联

16路相联

24路相联

32路相联

48路相联

64路相联

96路相联

128路相联

192路相联

cache块大小字段bits[1:

0]的含义如下所示:

cache块大小

0b00

2个字(8字节)

0b01

4个字(16字节)

0b10

8个字(32字节)

0b11

16个字(64字节)

∙CP15的寄存器C1

mrcp15,0,r0,c1,c0{,0}

将CP15的寄存器C1的值读到r0中

mcrp15,0,r0,c1,c0{,0}

将r0的值写到CP15的寄存器C1中

CP15中的寄存器C1的编码格式及含义说明如下:

3116

附加

L4

RR

V

I

Z

F

R

B

D

P

W

C

0:

禁止MMU或者PU;

1:

使能MMU或者PU

禁止地址对齐检查;

使能地址对齐