STI及WPE问题及版图注意事项.docx

《STI及WPE问题及版图注意事项.docx》由会员分享,可在线阅读,更多相关《STI及WPE问题及版图注意事项.docx(15页珍藏版)》请在冰豆网上搜索。

STI及WPE问题及版图注意事项

STI及WPE问题及版图注意事项

STI及WPE问题及版图注意

分locos隔离和STI隔离

Locos隔离是厚氧隔离,STI是浅沟道隔离

STI的概念

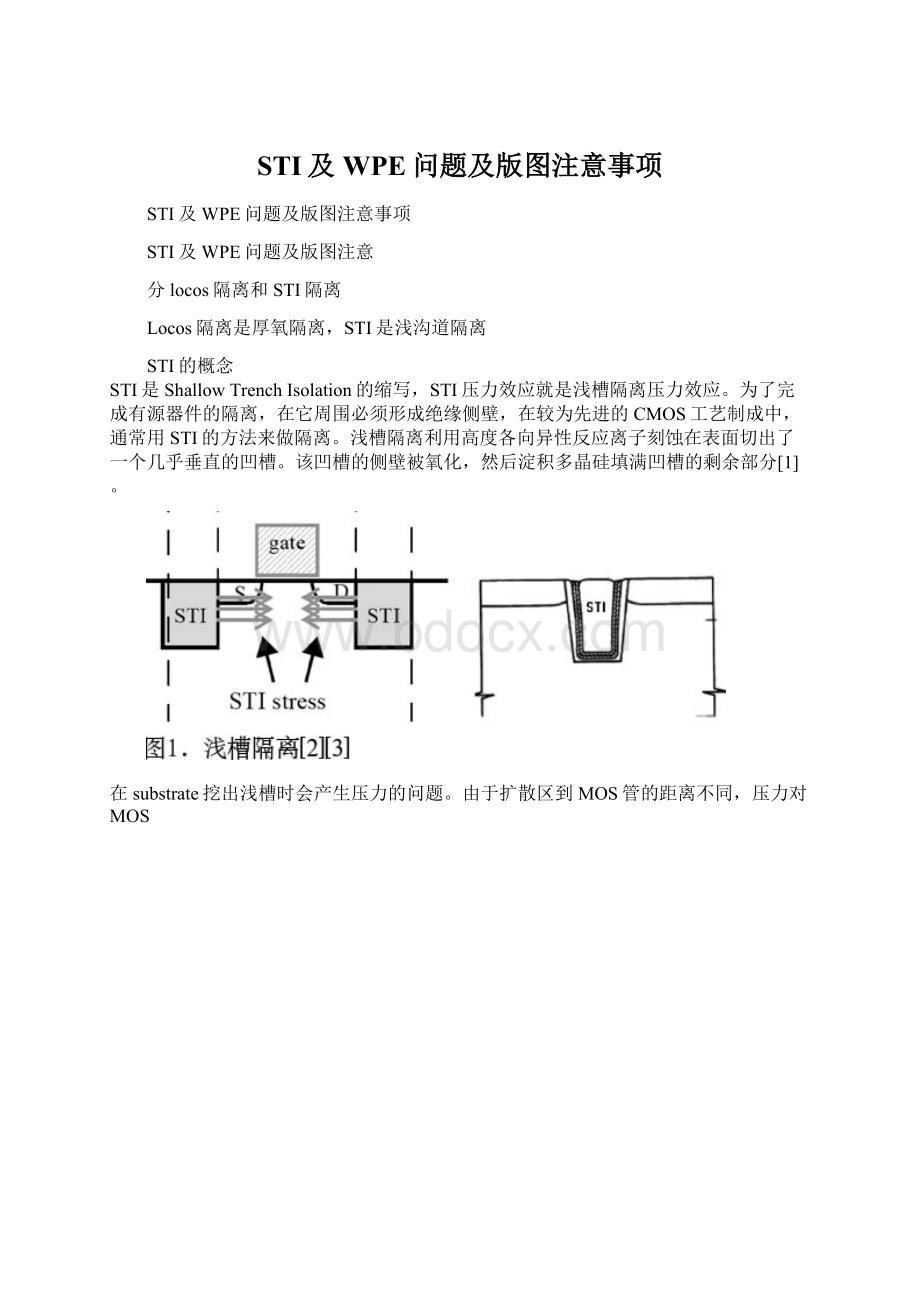

STI是ShallowTrenchIsolation的缩写,STI压力效应就是浅槽隔离压力效应。

为了完成有源器件的隔离,在它周围必须形成绝缘侧壁,在较为先进的CMOS工艺制成中,通常用STI的方法来做隔离。

浅槽隔离利用高度各向异性反应离子刻蚀在表面切出了一个几乎垂直的凹槽。

该凹槽的侧壁被氧化,然后淀积多晶硅填满凹槽的剩余部分[1]。

在substrate挖出浅槽时会产生压力的问题。

由于扩散区到MOS管的距离不同,压力对MOS

数量不一样(虽然不同导体自由电子也不一样,但平均来说,半导体的自由电子量级是远远低于导体),如本征半导体,导电性非常差,因为电子和空穴的数目相等,而掺杂半导体根据掺杂类型的不同,P型中空穴较多,N型中电子较多,这样在电场作用下就会产生电流。

深入到具体理论,需要从能带角度来解释,这个相对要深一些。

本征半导体在绝对零度是不导电的,因为导带中没有电子,在温度、光照等作用下,价带电子跃迁到导带形成自由电子,价带中形成空穴,这就是电子空穴对;掺杂半导体杂质原子提供电子或空穴。

而导体的导带是半满带,本身就有大量自由电子,不需要激发跃迁,所以导电性好。

绝缘体因为禁带宽度很大,因此价带上的电子很难跃过禁带跃迁到导带,导带上没有电子就不导电。

第五组:

什么是Bipolar工艺,什么是Cmos工艺,什么是Bi-cmos工艺,什么是BCD工艺

双极器件,bipolar,是以PN-PN结为基础的器件

CMOS指互补金属氧化物(PMOS管和NMOS管)共同构成的互补型MOS集成电路制造工艺,它的特点是低功耗。

由于CMOS中一对MOS组成的门电路在瞬间看,要么PMOS导通,要么NMOS导通,要么都截至,比线性的三极管(BJT)效率要高得多,因此功耗很低。

BCD工艺概述OverviewofBCDProcess是一种单片集成工艺技术。

1986年由意法半导体(ST)公司率先研制成功,这种技术能够在同一芯片上制作双极管bipolar,CMOS和DMOS器件,称为BCD工艺。

了解BCD工艺的特点,需要先了解双极管bipolar,CMOS和DMOS器件这三种器件的特点,详见表1。

$j&D,P'k1D(g表1双极管Bipolar,CMOS和DMOS器件的特点器件类别器件特点应用双极器件两种载流子都参见导电,驱动能力强,工作频率高,集成度低模拟电路对性能要求较高部分(高速、强驱动、高精度)3~1n${6h#s7YCMOS器件集成度高,功耗低适合做逻辑处理,一些输入,也可以做输出驱动DMOS器件高压大电流驱动(器件结构决定漏端能承受高压,高集成度可在小面积内做超大W/L)模拟电路和驱动,尤其是高压功率部分,不适合做逻辑处理.)BCD工艺把双极器件和CMOS器件同时制作在同一芯片上。

它综合了双极器件高跨导、强负载驱动能力和CMOS集成度高、低功耗的优点,使其互相取长补短,发挥各自的优点。

更为重要的是,它集成了DMOS功率器件,DMOS可以在开关模式下工作,功耗极低。

不需要昂贵的封装和冷却系统就可以将大功率传递给负载。

低功耗是BCD工艺的一个主要优点之一。

整合过的BCD工艺制程,可大幅降低功率耗损,提高系统性能,节省电路的封装费用,并具有更好的可靠性。

第六组:

衬底噪声产生的原因,及解决方法

衬底噪声产生原因:

源、漏-衬底pn结正偏导通,或者电源连线接点引入的串绕,使得衬底电位会产生抖动偏差,这称为衬底噪声。

■解决方法:

●对于轻掺杂的衬底,要用保护环把敏感部分电路包围起来

●把gnd和衬底在片内连在一起,然后由一条线连到片外的全

局地线,使得gnd和衬底的跳动一致,也可以消除衬底噪声。

●场屏蔽作用:

每个block外围一层金属(ptap),使每单元

模块同电势,而且模块之间不相互影响。

第七组:

什么是WPE

WPE的概念

在离子注入制造工艺时,原子从掩模板的边沿开始扩散,在阱边附近的地方硅片表面变得密集,如图2所示。

结果就是,阱表面浓度会随着距离掩模板的边沿的远近而有所不同,因此整个阱的掺杂浓度是不均匀的,如图2中的a)所示。

这种不均匀造成MOS管阈值电压的不同,还有其它的电性能也有所不同,它会随着距离阱边距离的不同而不同,如图2中的b)所示。

这种现象就是我们常说的阱邻近效应(WPE:

WellProximityEffect)[2]。

Wpe:

井邻近效应(welledge–proximity(接近、邻近、感应器)effect)

WPE效应根本的原因是:

植入的离子在光阻材料上发生了散射,在光阻边缘,散射离子进入到阱硅表面,影响了边缘区域的掺杂浓度。

考虑WPE的影响主要表现在三个方面:

阈值电压、迁移率及体效应。

CMC(CompactModelCouncil)紧凑模型协会对WPE模型进行了拓展。

上述定义较为宽泛,因为一般来讲应该有三种情况:

1,形成N型阱;2,形成P型阱;3,形成深N型埋层;在另一资料中有这样的说明:

深阱为闩锁效应保护提供了低电阻路径,并且抑制了双极型增益,深埋层也是NMOSFET隔离三阱的关键。

然而,深埋层影响了光阻边缘器件。

一些离子在光阻上散射到光阻边缘的硅表面上,改变了这些器件的阈值电压。

据观察阈值偏差可以达到20-100mV,横向范围约3-10um,在硼深反型P阱中,磷深反型N阱中及被三阱隔离的P阱中都可以观察到。

需要注意的是:

深埋层的顺序在不同工厂会有所不同,比如IBM:

STI->NW->PW->DNW,TSMC:

STI->DNW->PW->NW。

相对而言,TSMC的深埋层对隔离P型阈值影响要小些。

——如何减少或避免WPE/STI效应对IP模块设计的影响

随着深亚微米工艺的发展,CMOS制造工艺对设计的影响也越来越大。

在0.18um以前都可以忽略的工艺影响,在工艺一步一步发展的情形下,制造工艺所带来的影响变成了芯片设计中不可忽视的因素。

本文诠释了制造工艺的两个重要效应:

STI、WPE。

通过对两种效应的分析,提出了在芯片设计阶段考虑它们的必要性。

特别是针对IP模块级别的设计,本文给出了在电路设计阶段和版图设计阶段时,如何减小或者避免这两种效应的方法,并且分析和讨论这些方法的优缺点。

STI的概念

STI是ShallowTrenchIsolation的缩写,STI压力效应就是浅槽隔离压力效应。

为了完成有源器件的隔离,在它周围必须形成绝缘侧壁,在较为先进的CMOS工艺制成中,通常用STI的方法来做隔离。

浅槽隔离利用高度各向异性反应离子刻蚀在表面切出了一个几乎垂直的凹槽。

该凹槽的侧壁被氧化,然后淀积多晶硅填满凹槽的剩余部分[1]。

在substrate挖出浅槽时会产生压力的问题。

由于扩散区到MOS管的距离不同,压力对MOS管的影响也不同。

所以对于相同长宽两个MOS管,由于对应的扩散区长度的不同而造成器件性能的不同。

WPE的概念

在离子注入制造工艺时,原子从掩模板的边沿开始扩散,在阱边附近的地方硅片表面变得密集,如图2所示。

结果就是,阱表面浓度会随着距离掩模板的边沿的远近而有所不同,因此整个阱的掺杂浓度是不均匀的,如图2中的a)所示。

这种不均匀造成MOS管阈值电压的不同,还有其它的电性能也有所不同,它会随着距离阱边距离的不同而不同,如图2中的b)所示。

这种现象就是我们常说的阱邻近效应(WPE:

WellProximityEffect)[2]。

设计中减小、避免STI、WPE效应的重要性

STI效应

STI带来的压力对器件性能有重要影响,特别是电流Idsat和阈值电压Vth。

而这些效应是非常重要的,在仿真器件性能的时候必须包含在内,而MOS管的特性与版图的设计又是息息相关的(图3)。

下面通过一组实验数据看看STI的压力对于MOS管漏端电流Ids的影响。

横轴是不同的Vgs值(图4)。

测试STI的压力对于PMOS管和NMOS管的漏端电流的影响。

工艺是0.13um,PMOS管和NMOS管为3.3V,length=0.6um,width=24um,此处设置sa=sb。

我们可以看出,这种压力对于PMOS管和NMOS管的影响正好相反。

PMOS管:

电流随SA(SB)的增大而变小;NMOS管:

电流随SA(SB)的增大而增大。

测试STI的压力对于gm的影响,横轴是不同的Vgs值(图5)。

在Sa=Sb=0.345um,Sa=Sb=1.5um,两种条件下,对于一个length=0.15um的PMOS,相差约有3%,对于一个length=0.6um的PMOS,相差约有10%。

而这些差异,仅仅是一个MOS的差异,对于数十个、数百个甚至与数千个MOS的组合会使电路偏差很大,有可能导致不工作。

WPE效应

下面我们再来看看WPE的影响.对于同一个器件,固定的长宽,固定的源漏区(SA、SB)大小,根据将它放置在离阱边界距离不同的地方(图6)。

我们看到了下面的测试结果(图7):

0.13um工艺下,测试3.3VNMOS管的Vth随SC的距离的变化:

我们可以看出,当NMOS管距离阱边比较近的时候,Vth会增大约50mV。

Vth也会随着源漏端的方向而有所不同,达到约有10mV的偏差。

当NMOS管距离阱边比较远的时候,如SC的距离大于3um,Vth基本上就没有多少的偏差了。

通过一系列实验数据,我们可以看出,STI、WPE对器件性能有重要影响,在深亚微米IP模块设计中必须考虑的制造工艺的影响。

那么,对IP模块级别的设计,如何减小或者避免这两种效应呢?

电路设计中如何减小STI、WPE的影响

在电路设计阶段,在版图设计没有进行或还没有完成时,我们并不能准确预测到完成后的版图会对电路带来怎样的影响。

在这个阶段,我们如何尽量避免这些效应呢?

在此,对于IP模块设计者给出几种方法可供参考。

方法一:

预先估计MOS管的SA、SB和SC的值,再进行仿真调试,进而达到理想的设计值。

根据制造工艺的设计规则要求,电路设计者可以预估常规MOS管的SA、SB和SC的值,从而较快的进行较为准确的电路设计。

对于具有大驱动能力的MOS管,这种方法也很适用。

但是由于预估的SA、SB和SC的值不会100%准确,所以会有少量的误差。

比如原始语句是:

******************************

.SUBCKTTOPZA

M1ZAINVSSw=2.000000l=0.130000m=2

……

.ENDSTOP

******************************

在前期仿真阶段,更具所选用的工艺制程所必须的设计规则,加入预估的SA、SB、SC的值(图8),语句如下:

******************************

.SUBCKTTOPZA

M1ZAINVSSw=2.000000l=0.130000m=2sa=0.250000sb=0.63000sc=1.6000000…. [5]

……..

.ENDSTOP

******************************

方法二:

预先放大或缩小MOS管。

PMOS管的电流随SA/SB的增大而变小,所以可以预先放大PMOS管;NMOS管的电流随SA/SB的增大而增大,所以可以预先缩小NMOS管。

这种作用类似于方法一,都是将WPE和STI效应在电路设计阶段就考虑进来,而不是等