Sigma Delta ADC原理简单理解Word文档下载推荐.docx

《Sigma Delta ADC原理简单理解Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《Sigma Delta ADC原理简单理解Word文档下载推荐.docx(8页珍藏版)》请在冰豆网上搜索。

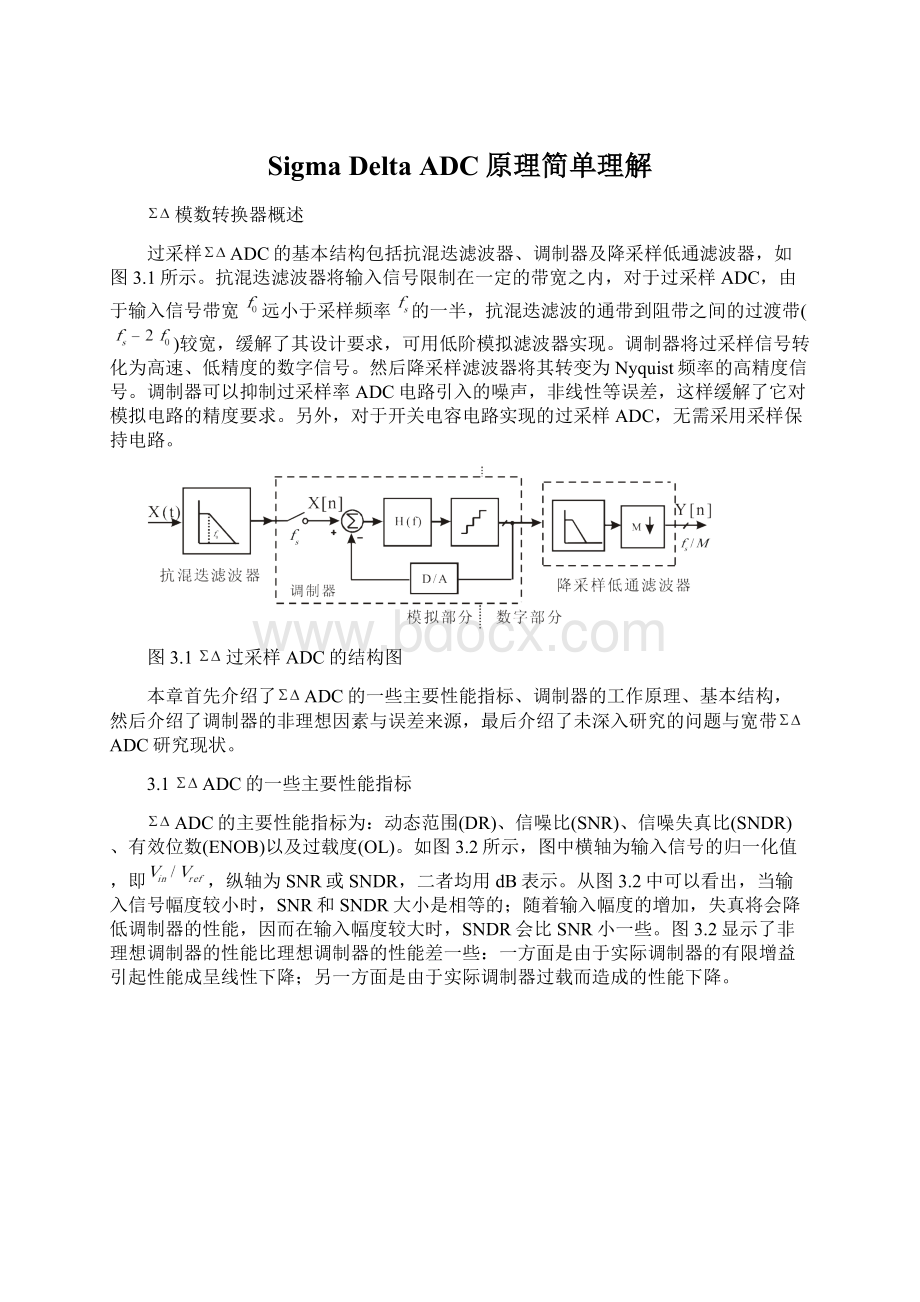

随着输入幅度的增加,失真将会降低调制器的性能,因而在输入幅度较大时,SNDR会比SNR小一些。

图3.2显示了非理想调制器的性能比理想调制器的性能差一些:

一方面是由于实际调制器的有限增益引起性能成呈线性下降;

另一方面是由于实际调制器过载而造成的性能下降。

图3.2典型的转换器的性能图

调制器各相主要性能指标[60]介绍如下:

1.信噪比(SNR):

是指在一定的输入幅度时,转换器输出信号能量与噪声能量的比值。

转换器能获得的最大信噪比为峰值信噪比(PSNR)。

2.信噪失真比(SNDR):

是指在一定的输入幅度时,转换器输出信号能量与噪声、失真之和的比值。

转换器能获得的最大信噪失真比为峰值信噪失真比(PSNDR)。

3.动态范围(DR):

输入动态范围()是指转换器最大输入信号和能检测到的最小输入信号能量的比值,这里最大信号能量定义为PSNR下降6dB时的输入值,而最小信号即为背景噪声能量值。

输出动态范围()定义为最大输出信号能量和最小输出信号能量的比值,等于PSNR。

4.有效位数(ENOB):

是根据实际测量的PSNDR来计算的,如下式所示:

(3.1)

5.过载度(OL):

是指使调制器过载时的最小归一化输入值,其对应的SNR比PSNR小6dB。

与Nyquist速率ADC不同,过采样速率ADC不关心积分非线性(INL)和差分非线性(DNL)两项指标。

这是因为这两项指标都是衡量采样点和采样点之间的精度,而过采样率ADC的输出都与其前一个状态有关,因而INL和DNL在这种情况下是没有意义的。

3.2ADC提高信噪比的方法

转换器主要是通过过采样和噪声整形来提高信噪比的,从而获得高精度。

此外,采用多位量化器也是目前提高宽带转换器信噪比的一种基本方法。

3.2.1过采样

转换器采用远远高于Nyquist频率的时钟对输入信号进行采样,使得量化噪声的功率分布在更宽的频带内,这样就减少了信号频带内的噪声。

这也是过采样ADC的基本原理。

图3.3给出了在过采样率和Nyquist采样率下信号和量化噪声功率频谱图。

由图可见,过采样率下的信号带宽内的量化噪声功率要比Nquist采样率下的小得多。

在对输入信号进行量化时,会引入量化误差。

假设量化噪声e随机均匀分布,且与输入信号无关,即为白噪声,其功率[61]为:

(3.2)式(3.2)中为量化间距。

噪声功率密度为:

(3.3)

其中为采样频率,可见量化噪声总功率与采样频率无关,但噪声功率谱密度却与采样频率有关,提高采样频率可以降低单位频带内的功率谱密度。

我们定义过采样率OSR为:

(3.4)

这样,在过采样率下,输出的信号频带内的总量化噪声功率为:

(3.5)

从式(3.5)可以看出,提高过采样率可以降低信号带宽内的噪声功率。

采样率每提高一倍,信号带宽内的噪声功率降低3dB,在输入信号功率不变的情况下,相当于增加了0.5位的分辨率。

当时,动态范围增加24dB,即相当于提高4位分辨率。

但这种指数式增长的过采样率很快就达到电路实现的极限,因此在实际电路中,通常OSR不会超过512。

图3.3量化器信号和噪声频谱图

3.2.2噪声整形

噪声整形可以进一步提高转换器的信噪比。

利用高通滤波器的特性,将低频部分的量化噪声移到高频,减少了信号带宽内的噪声。

高通滤波器的阶数和采样频率越高,信号带宽内的噪声就越小。

实现噪声整形的一常见方法就是采用调制器。

如图3.4(a)所示,它包括一个滤波器、一个B位ADC和一个B位DAC。

其线性模型如图3.4(b)所示,图中假设D/A是理想的。

调制器的传输函数为:

(3.6)

其中、分别为信号和量化噪声的Z域变换。

定义信号传输STF(z)和噪声传输函数NTF(z)分别为(3.7)-(3.8):

(3.7)

(3.8)

显然,如果选择H(z)在信号带宽内有很大增益,而在信号带宽外增益很小,则趋近于1,趋近于0。

这样输入信号就被直接输出,几乎不受影响,而量化噪声却被整形压缩。

(a)(b)

图3.4调制器及其线性模型

L阶噪声整形调制器的信号和噪声传输函数为:

(3.9)

则信号带宽内的量化噪声能量为:

(3.10)

一般的,过采样率每提高一倍,信号带宽内的噪声功率降低,在输入信号功率不变的情况下,相当于提高了位的分辨率。

图3.5给出了一阶、二阶、三阶调制器的噪声传输函数(公式3.9)的幅频响应曲线。

与一阶调制器相比,二阶调制器的NTF将低频带内的量化噪声进一步压缩,而对高频带内的量化噪声进一步放大,即量化噪声进一步“推”向更高频段,阶数越高,效果越明显。

图3.5一阶、二阶、三阶调制器的噪声传输函数的幅频响应

3.2.3多位量化器

采用多位量化器可以有效的提高信噪比[62~66]。

随着转换信号带宽的不断提高,通过过采样和噪声整形技术不能完全满足设计目标的要求。

将调制器中的量化器位数提高,也即减小了,这样量化噪声的功率谱密度下降了。

实际上,量化器位数每增加一位,调制器的有效位数也增加一位。

此外,量化器位数提高,可以提高高阶调制器的稳定性。

理想的L阶、B位调制器的动态范围如(3.11)式所示[60]:

(3.11)

如果对多位量化器的非线性不作特殊的技术处理,量化器的非线性将直接影响调制器的性能[67]。

后续章节将会分析不同降低量化器非线性的技术。

3.3调制器结构

调制器大致可以分为单环结构和级联结构两种。

单环结构采用一个A/D转换器、一个D/A转换器和一系列串连的积分器组成。

一阶、二阶都属于单环结构。

级联结构(MASH)是由一系列的低阶单环调制器级联而成。

此外,单环和级联结构都可以采用一位或多位ADC和DAC,通过降低量化噪声,达到提高信噪比的目的。

不同结构有不同的优缺点,如表3.1所示。

表3.1调制器结构的比较

单环结构

级联结构

稳定性

有条件稳定

稳定

过采样率(OSR)

适用于高的OSR

适用于低的OSR

动态范围(DR)

与理想DR相差较远

与理想DR接近

对电路的失配及电荷泄漏的敏感性

低

高

电路组成

全模拟

模拟和数字

3.3.1单环结构

最简单、无条件稳定的调制器便是一阶噪声整形实现的单环调制器。

如图3.6所示,它由一个积分器、一个一位的ADC和一个1位的DAC组成。

输入信号与输出信号经DAC转换后的信号相减,经积分器积分后进入量化器。

积分器的传输函数为。

则调制器的输出可以表示为:

(3.12)

图3.6一阶调制器的原理图

噪声传输函数为:

(3.13)

信号带宽内的噪声功率为:

(3.14)

假设满量程正弦输入信号的能量为,得到一阶调制器的最大信噪比为:

(3.15)

由式(3.15)可知,采用一阶噪声整形可以降低带宽内的噪声功率:

过采样率每提高一倍,信噪比提高9dB,相当于提高了1.5位的分辨率。

调制器是一个反馈系统,从时域角度讲,反馈不断使输出逼近输入。

对式(3.12)做差分变换可得输入输出差分方程:

(3.16)

可见,调制器的当前输出等于延迟了一个时钟的输入加上量化误差的一阶差分。

图3.7(a)为一阶调制器输入和输出的瞬态仿真结果。

不考虑实际电路中的非理想因素,采样频率,过采样率,输入信号频率。

很显然,在正弦信号值较大时,输出1的几率就大,反之,出现的几率就大。

(a)

(b)

图3.7一阶调制器的仿真

(a)输入为正弦时调制器的输出;

(b)输出信号的频谱

图3.7(b)为对输出码流的4096点FFT分析结果。

图中,能量最大的频点位置代表了输入信号频率,整个噪声呈30dB/dec衰减,这与一阶噪声整形的衰减相符;

另外,在信号的倍频点出现很多谐波(tones),这说明量化器的输出和输入信号相关性很高,量化噪声不再是白噪声。

大量谐波的出现是一阶调制器的缺点[61,68]。

高阶调制器可以减小输出频谱中的谐波,这是因为高阶调制器可以使量化器输入和输入信号的相关性大大降低。

由于一阶调制器会出现谐波的特性,这种结构很少用于单环调制器。

然而在下章节讲的级联调制器中,第二、第三级经常采用一阶调制器。

这是因为在级联调制器中,第二、三级输入的信号为第一级输出的量化噪声,一阶调制器将不受谐波的影响。