数据通路实验报告Word下载.docx

《数据通路实验报告Word下载.docx》由会员分享,可在线阅读,更多相关《数据通路实验报告Word下载.docx(13页珍藏版)》请在冰豆网上搜索。

当然,独立数据传送通路的数量增加势必提高控制器设计复杂度。

因此,在满足速度指标的前提下,为使数字系统结构尽量简单,一般小型系统中多采用单一总线结构。

在较大系统中可采用双总线结构或者三线结构。

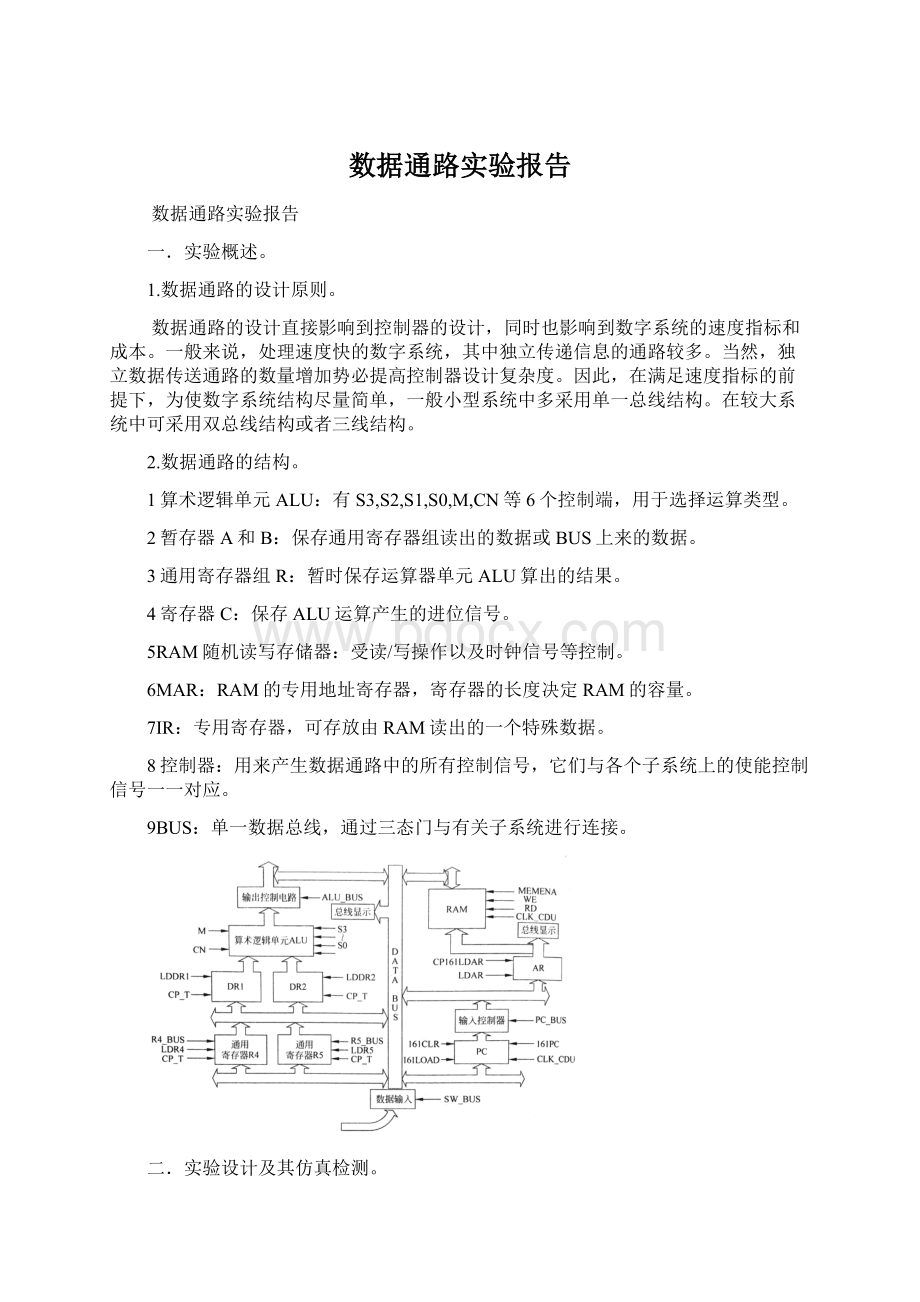

2.数据通路的结构。

1算术逻辑单元ALU:

有S3,S2,S1,S0,M,CN等6个控制端,用于选择运算类型。

2暂存器A和B:

保存通用寄存器组读出的数据或BUS上来的数据。

3通用寄存器组R:

暂时保存运算器单元ALU算出的结果。

4寄存器C:

保存ALU运算产生的进位信号。

5RAM随机读写存储器:

受读/写操作以及时钟信号等控制。

6MAR:

RAM的专用地址寄存器,寄存器的长度决定RAM的容量。

7IR:

专用寄存器,可存放由RAM读出的一个特殊数据。

8控制器:

用来产生数据通路中的所有控制信号,它们与各个子系统上的使能控制信号一一对应。

9BUS:

单一数据总线,通过三态门与有关子系统进行连接。

二.实验设计及其仿真检测。

一,运算器。

8位运算器VHDL

波形仿真

二,存储器。

顶层设计:

其中sw_pc_ar的VHDL语言描述:

三,原仿真实验电路。

仿真结果:

四,修改电路。

因为此次实验结果需要下载到FPGA板中进行操作及观察,而原始电路中,需要输入的变量数量过多,导致电板中的输入按键不够用,所以需要对电路进行修改。

此时我们引入一个计数器PC来代替需要手动输入的指令alu_sel[5..0]以及数据d[7...0]。

同时还需要引入数码管的位选信号译码器choose和段选信号译码器xianshi。

计数器PC的VHDL语言描述

位选信号译码器choose的VHDL语言描述

段选信号译码器的VHDL语言描述

经过修改和完善以后的电路图为

完善后的电路的引脚分配情况

三.实验过程。

a)进行数学运算以及将运算结果储存在某个固定的内存地址处。

然后从该地址处读出结果

i.打开pc_sel[2],重置地址计数器。

ii.打开总线开关bus_sel[0],和PC_sel[2],pc_sel[1],pc_sel[0],让地址计数器开始计数,跳变到某个地址x时关闭。

iii.打开总线开关BUS_SEL[4],打开暂存器r1的开关ld_reg[4],然后打开计数器开关en计数器开始计数,当计数到需要的数字a时,关闭计数器开关en,此时数字a存入暂存器r1,关闭暂存器的开关ld_reg[4],后再关闭总线开关BUS_SEL[4],然后再打开计数器的清零开关clr再关闭。

iv.同理第iii步,在暂存器r2中存入数据b。

v.打开总线开关bus_sel[0].地址计数器开关ld_reg[0]和pc_sel[2],pc_sel[1],pc_sel[0]选择存储地址

vi.打开运算器到总线的开关bus_sel[1],打开计数器en计数开关en当计数器跳变到加法指令011001时,关闭计数开关en,然后代开rom的地址开关pc_sel[2],以及可写开关we_rd[1]。

将从运算器中计算出来的运算结果a+b存储到ram中的x地址中,关闭可写开关we_rd[1],关闭pc_sel[2]和总线开关,最后将计数器清零。

vii.打开ram的可读开关,读取x地址处的数据a+b。

四.实验现象。

输入数据a

输入数据b

进行运算并将运算结果写入内存

从内存中读取计算结果

五.实验心得。

第一次在电板上进行这么多的操作。

操作过程虽然很多,但只要理解操作过程,明白各个按键所设置的引脚作用,实验其实并不难,重点在于要理解过程,明白数据的输入,存入寄存器,运算以及往内存中进行存取值的操作,那么数据通路的按键很容易记住。

在实验过程中还是存在很多问题的,尤其的刚开始做实验的时候,不理解数据通路实验过程中各个门的输入的意义和顺序,但真正懂得的时候,实验就变得简单了。