单元十三稳压电路与定电流源.docx

《单元十三稳压电路与定电流源.docx》由会员分享,可在线阅读,更多相关《单元十三稳压电路与定电流源.docx(12页珍藏版)》请在冰豆网上搜索。

单元十三稳压电路与定电流源

單元十三穩壓電路與定電流源電路

實習13-1:

串聯電壓調節器

一.相關原理

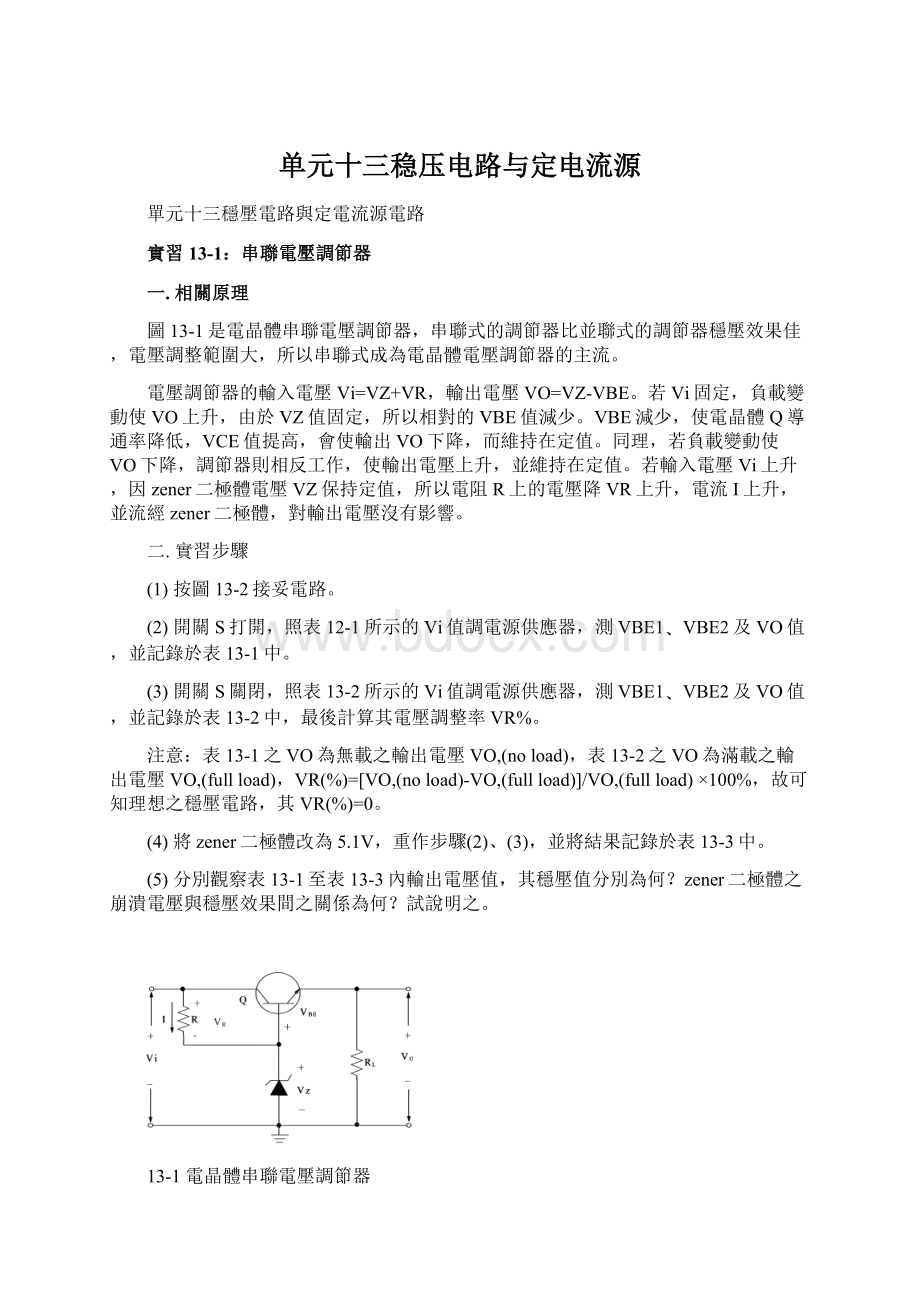

圖13-1是電晶體串聯電壓調節器,串聯式的調節器比並聯式的調節器穩壓效果佳,電壓調整範圍大,所以串聯式成為電晶體電壓調節器的主流。

電壓調節器的輸入電壓Vi=VZ+VR,輸出電壓VO=VZ-VBE。

若Vi固定,負載變動使VO上升,由於VZ值固定,所以相對的VBE值減少。

VBE減少,使電晶體Q導通率降低,VCE值提高,會使輸出VO下降,而維持在定值。

同理,若負載變動使VO下降,調節器則相反工作,使輸出電壓上升,並維持在定值。

若輸入電壓Vi上升,因zener二極體電壓VZ保持定值,所以電阻R上的電壓降VR上升,電流I上升,並流經zener二極體,對輸出電壓沒有影響。

二.實習步驟

(1)按圖13-2接妥電路。

(2)開關S打開,照表12-1所示的Vi值調電源供應器,測VBE1﹑VBE2及VO值,並記錄於表13-1中。

(3)開關S關閉,照表13-2所示的Vi值調電源供應器,測VBE1﹑VBE2及VO值,並記錄於表13-2中,最後計算其電壓調整率VR%。

注意:

表13-1之VO為無載之輸出電壓VO,(noload),表13-2之VO為滿載之輸出電壓VO,(fullload),VR(%)=[VO,(noload)-VO,(fullload)]/VO,(fullload)×100%,故可知理想之穩壓電路,其VR(%)=0。

(4)將zener二極體改為5.1V,重作步驟

(2)、(3),並將結果記錄於表13-3中。

(5)分別觀察表13-1至表13-3內輸出電壓值,其穩壓值分別為何?

zener二極體之崩潰電壓與穩壓效果間之關係為何?

試說明之。

13-1電晶體串聯電壓調節器

圖13-2電晶體串聯電壓調節器實驗電路

三.結果數據

表13-1未加負載之串聯電壓調節器實驗結果

Vi(V)

VBE1(V)

VBE2(V)

VO(V)

10

12

14

16

18

20

22

24

表13-2負載狀況下串聯電壓調節器實驗結果

Vi(V)

VBE1(V)

VBE2(V)

VO(V)

VR%

10

12

14

16

18

20

22

24

表13-3串聯電壓調節器使用不同zener二極體之穩壓效果

Vi(V)

VBE1(V)

VBE2(V)

VO(V)

VR(%)

4V

6V

8V

10V

12V

14V

16V

實習13-2:

回授式串聯電壓調節器

一.相關原理

圖13-3是回授式串聯電壓調節器,VO=Vi-VCE2,其中電晶體Q2是射極隨耦器,因為所有的負載電流都流經Q2,所以Q2也稱為傳送電晶體。

當VO上升時,回授電壓VF上升,VBE1也上升,則IB1增大,並使得IC1增加,VCE1下降。

VCE1下降使Q2的基極電壓VB2減少,VBE2下降,最後Q2的IB2、IC2減少,VCE2上升,即輸出電壓VO減少。

同理,若VO減少,回授電壓VF減少,VBE1就會減少,IB1減小,VCE1會增大。

VCE1增大使Q2的基極電壓VB2增大,VCE2降低,結果VO上升。

所以無論負載怎麼改變,電壓調節器的輸出電壓VO都不變。

圖13-3的輸出電壓VO:

且VF=(VBE+VZ)

(13-1)

由(13-1)式看出,適當的調整R3與R4的比值,便可調整所需的輸出電壓VO值。

圖13-3的傳送電晶體Q2是和負載RL串聯的,故稱為串聯調節器。

它的缺點是功率消耗都在傳送電晶體Q2上,即

PD=VCE2×IC2=(Vi-VO)IC(13-2)

若負載電流太大,Q2勢必消耗很多電源,所以必須提供大的散熱槽及較高的電源供給。

二.實習步驟

(1)按圖13-4接妥電路,其中Vi為電源供應器之輸出電壓。

(2)開關S打開,調整電源供應器為15V,即為Vi。

(3)調可變電阻VR1,測得VO(min)和VO(max),記錄於表12-4內。

(4)R3=3.3k﹑R4=1k,重作步驟(3)。

(5)R3=1k﹑R4=3.3k,重作步驟(3)。

(6)開關S關閉,重作步驟(3)至(5)。

圖13-3電晶體回授式串聯電壓調節器

圖13-4電晶體回授式串聯電壓調節器實驗電路

三.結果數據

表13-4回授式串聯電壓調節器穩壓效果

VO(min)

VO(max)

VO(min)

理論值

VO(max)

理論值

R3=1k

R4=1k

R3=3.3k

無RL

R4=1k

R3=1k

R4=3.3k

R3=1k

R4=1k

R3=3.3k

有RL

R4=1k

R3=1k

R4=3.3k

實習13-3:

定電流源電路

一.相關原理

定電流源顧名思義就是輸出電流為一定值,無論負載RL如何改變,其通過之電流IL都保持不變,如圖13-5(a)電路,其特性曲線如圖13-5(b)所示。

定電流源電路在我們現今工業上用途極廣,如用於蓄電池充電器,電鍍工業上。

圖13-6為一簡單定電流電路,其電路是由一個電流源和輸出電阻並聯而成,電流源所供給的電流即為輸出電阻上的電流IS與負載電阻電流IL之和,若電流源之輸出電阻遠大於負載電阻,則大部分之電流便將流過負載,而構成一定電流源。

(a)定電流電路(b)特性

圖13-5理想的定電流電路

圖13-6簡單的定電流電路

若1A之電流源,其輸出電阻為200k,則流過1k與10k不同之負載電阻時,其電流分別為

負載變動量=錯誤!

內嵌物件無效。

,但電流變化量僅=,但若負載變化加大,如200k,則:

,可知當負載電阻RL愈大或電流源輸出電阻愈小,便無法構成一理想之定電流源,故負載電阻應甚小於電流源之輸出電阻(RL<在電子電路中可利用OPA或BJT來組成定流源電路。

其電路與工作原理分述如下:

(一)OPA定電流源電路

圖12-7為基本OP.AMP構成的定電流源電路,其電路是利用一電壓源(VIN)經過電阻器(Ri)以提供一定電流(Ii),因為OP.AMP的反相輸入端為一虛擬接地點,因此輸入電流,由於OP.AMP輸入阻抗非常高,幾乎沒有電流可以流進OPA內部,所以全部Ii流經RL即IL=Ii=VIN/Ri。

由此只要VIN及Ri保持常數,即使RL再怎樣改變,IL仍為定值

圖13-7基本OPAMP的定電流源電路

圖12-8中,輸入電壓改由一稽納二極體來提供,因Zener之穩壓作用,可得一固定之OPA輸入電壓,正常工作下,其Ii之電流仍相當於IL之電流,構成定電流源之條件。

若欲改變定電流源輸出電流大小,則改變R1電阻值即可。

圖12-9是利用加法器和一反相器組成定電流電路,從此電路中

令Va=VL,由OP.AMPA2之反相放大組態增益得知Vb/Va=-Rb/Ra=-1,故Va=-Vb=VL,可得

VC=-VS+VL

而Ra電阻之壓降

VR=VC-VL=-VS+VL-VL=-VS

所以流過Ra之電流IR為

IR=IC=-VC/RC=VR/Ra

在電路中,IR=Ia+IL,圖13-9中OP.AMPA2反向輸入端為虛擬接地,故

如使用較大之Rb,則Ia?

0,故

圖13-8Zener二極體與OPA合成定電流源電路

圖13-9加法器與反相器合成之OPA定電流源電路

(二)BJT定電流電路

利用BJT電晶體作成之定電流源電路,如圖12-10。

圖中VBE幾為一固定值,故VE亦為固定值。

若欲改變定電流源之輸出電流大小,只要改變RE亦可。

(RE小則IL大;反之,RE大則IL小)。

圖13-10BJT電晶體定電流源電路

二.實習步驟

工作一:

Zener二極體與OPA合成定電流源電路

(1)按圖13-8接線。

(2)依表13-5之電阻值改變R1與RL,分別測量VA,VB,VO之電壓,並記錄於表13-5中。

(3)依I1=(VA-VB)/R1、IL=(VB-VO)/RL公式,計算出I1及IL之電流值,並作比較,I1是否等於IL?

為甚麼?

(4)由表13-5之數據說明此電路電流一旦由R1決定後,不論負載電阻RL如何變化,負載電流IL均幾乎不受影響。

工作二:

加法器與反相器合成之OPA定電流源電路

(1)按圖13-9接線,其中Ra,RL先接2kΩ固定電阻,VS接電源供應器或函數產生器DC2V。

(2)以示波器DC檔或三用電表量VC與VL電壓,並記錄於表13-6中。

(3)依IR=(VC-VL)/Ra、IL=VL/RL,計算IR與IL之電流值,並比較其差異。

(4)將Ra,RL換成10k可變電阻器,依表13-6所列之電阻值,依序調整10k可變電阻器,改變Ra及RL,重覆

(2)、(3)步驟,並記錄於表13-6中。

(5)依表13-6所列之VS電壓值,調整電源供應器或函數產生器,依序再重覆

(2)~(4)之步驟,並記錄於表13-6中。

工作三:

BJT電晶體定電流源電路

(1)按圖13-10接線,直流電壓源E供給DC12V,RL接4k固定電阻。

(2)以三用電表DCmA檔串聯於RL與RE上,測量IL與IE之大小,或以示波器、三用電表DC電壓檔量測電壓後,再除以RL與RE電阻,亦可得IL與IE之大小。

(3)依表13-7計算IL與IE之差異。

(4)將RL換成10k可變電阻器,依表13-7所列之電阻值,依序調整10k可變電阻器,改變RL,重覆

(2)、(3)步驟,並將結果記錄於表13-7中。

三.結果數據

表13-5Zener二極體與OPA合成定電流源電路實驗結果

R1

0.5k

1k

2k

VA

VB

VO

I1

IL

VA

VB

VO

I1

IL

VA

VB

VO

I1

IL

0.2k

1k

4k

10k

20k

表13-6加法器與反相器合成之OPA定電流源電路實驗結果

VS

+2V

+4V

-2V

VC

VL

IR

IL

Vc

VL

IR

IL

Vc

VL

IR

IL

2k

2k

1k

2k

2k

4k

3