数字电路复习题含解答.docx

《数字电路复习题含解答.docx》由会员分享,可在线阅读,更多相关《数字电路复习题含解答.docx(39页珍藏版)》请在冰豆网上搜索。

数字电路复习题含解答

一、填空题:

1.在计算机内部,只处理二进制数;二制数的数码为1、0两个;写出从(000)2依次加1的所有3位二进制数:

000、001、010、011、100、101、110、111。

2.13=(1101)2;(5A)16=(1011010)2;(10001100)2=(8C)16。

完成二进制加法(1011)2+1=(1100)2

3.写出下列公式:

=1;=B;=A+B;=。

4.含用触发器的数字电路属于时序逻辑电路(组合逻辑电路、时序逻辑电路)。

TTL、CMOS电路中,工作电压为5V的是TTL;要特别注意防静电的是CMOS。

5.要对256个存贮单元进行编址,则所需的地址线是8条。

6.输出端一定连接上拉电阻的是OC门;三态门的输出状态有1、0、高阻态三种状态。

7.施密特触发器有2个稳定状态.,多谐振荡器有0个稳定状态。

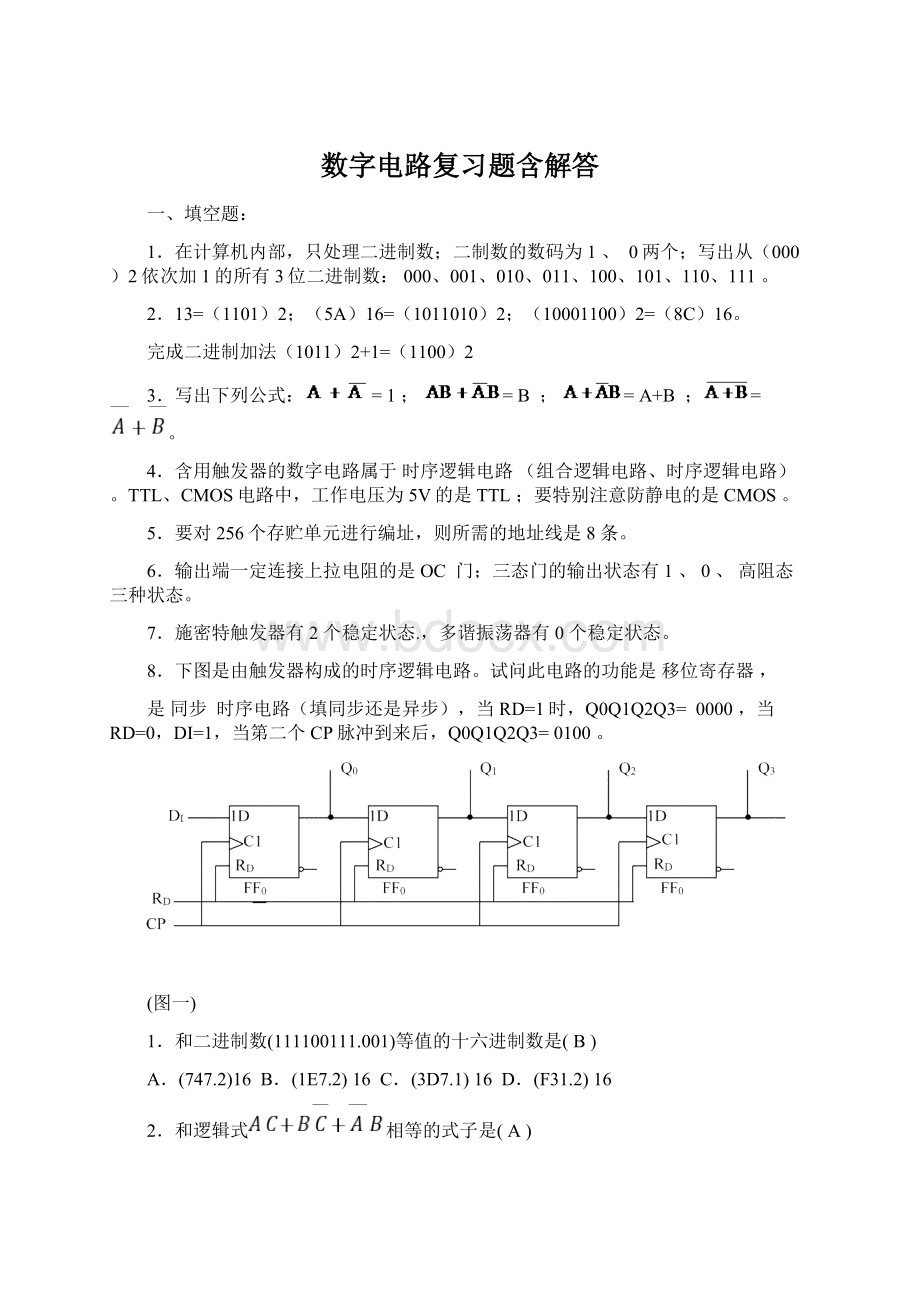

8.下图是由触发器构成的时序逻辑电路。

试问此电路的功能是移位寄存器,

是同步时序电路(填同步还是异步),当RD=1时,Q0Q1Q2Q3=0000,当RD=0,DI=1,当第二个CP脉冲到来后,Q0Q1Q2Q3=0100。

(图一)

1.和二进制数(111100111.001)等值的十六进制数是(B)

A.(747.2)16B.(1E7.2)16C.(3D7.1)16D.(F31.2)16

2.和逻辑式相等的式子是(A)

A.AC+BB.BCC.BD.

3.32位输入的二进制编码器,其输出端有(D)位。

A.256B.128C.4D.5

4.n位触发器构成的扭环形计数器,其无关状态数为个(B)

A.2n-nB.2n-2nC.2nD.2n-1

5.4个边沿JK触发器,可以存储(A)位二进制数

A.4B.8C.16

6.三极管作为开关时工作区域是(D)

A.饱和区+放大区B.击穿区+截止区

C.放大区+击穿区D.饱和区+截止区

7.下列各种电路结构的触发器中哪种能构成移位寄存器(C)

A.基本RS触发器B.同步RS触发器C.主从结构触发器

8.施密特触发器常用于对脉冲波形的(C)

A.定时B.计数C.整形

1.八进制数(34.2)8的等值二进制数为 11100.01 ;十进制数98的8421BCD码为 10011000 。

2.试写出下列图中各门电路的输出分别是什么状态(高电平、低电平)?

(其中(A)(B)为TTL门电路,而(C)为CMOS门电路)

(A)(B)(C)

Y1=02Y2=1Y3=1

3.一个JK触发器有 2 个稳态,它可存储 1 位二进制数。

4.单稳态触发器有一个稳定状态和一个暂稳状态。

施密特触发器有两个稳定状态、有两个不同的触发电平,具有回差特性。

多谐振荡器没有稳定状态,只有两个暂稳态。

以上三种电路均可由555定时器外接少量阻容元件构成。

A

B

F1

F2

F3

0

0

1

1

0

0

1

0

1

1

1

0

0

1

1

1

1

1

0

1

5.常用逻辑门电路的真值表如右图所示,则F1、F2、F3分别属于何种常用逻辑门。

F1同或,F2与非门,F3或非。

6.OC门的输出端可并联使用,实现__线与____功能;三态门的输出状态有______0________、1、

高阻三种状态。

7.时序逻辑电路的输出不仅和____输入___有关,而且还与___电路原来状态____有关。

1.(11001101011.101)2=1647.62510=1011001000111.0110001001018421BCD

2.已知N的补码是1.10110101,则N的原码是1.01001011,反码是1.10110100。

3.假设Zi为电路的输出,xi为电路的输入,yi为电路的状态,Zi=fi(x1…xn,y1…yn),

i=1,2…r,Zi描述的是组合逻辑电路;Zi=fi(x1…xn),i=1,2…r,Zi描述的

是时序逻辑电路。

4.5位扭环形计数器的无效状态为22。

5.如用0V表示逻辑1,-10V表示逻辑0,这属于正逻辑。

6.不会出现的变量取值所对应的最小项叫约束项。

7.对160个符号进行二进制编码,则至少需要8位二进制数。

8.逻辑函数F=的最小项之和表达式为。

9.三态门除了输出高电平和低电平之外,还有第三种输出状态,即高阻态状态。

10.RS触发器的特性方程为、_SR=0__。

1.二进制码11011010表示的十进制数为218,十六进制为DA。

2.D触发器的特征方程为,JK触发器的特征方程为。

3.在数字电路中三极管工作在0和1状态,所以数字电路只有两个状态。

4.A=(-59)10,A的原码是1111011,补码是1000101。

5.使用与非门时多余的输入端应接高电平,或非门多余的输入端应接低电平。

6.如果对72个符号进行二进制编码,则至少要7位二进制代码。

7.函数,其反函数为,对偶式为。

8.逻辑符号如图一所示,当输入,输入B为方波时,则输出F应为方波。

9.电路如图二所示,则输出F的表达式为Y=ABC。

图二

10.逻辑函数的表示方法真值表、逻辑表达式、逻辑图、卡诺图。

11.欲构成能记最大十进制数为999的计数器,至少需要三片十进制加法计数器,

或三片4位二进制加法计数器芯片。

12.时序逻辑电路中一定是含触发器。

13.五位扭环开计数器的无效状态有22。

14.若一个逻辑函数由三个变量组成,则最小项共有8。

学号:

1.=(D5=(213

=(100101=(111011

=(01000111=(00010100)8421BCD码

2.对于JK触发器的两个输入端,当输入信号相反时构成D触发器,当输入信号相同时构成T触发器。

3.组合逻辑电路的冒险现象是由竞争引起,表现为尖峰脉冲。

班级:

4.常见的脉冲产生电路有多谐振荡器,常见的脉冲整形电路

有施密特触发器。

5.触发器有2个稳态,存储8位二进制信息要8个触发器。

6.米利型时序电路输出信号与输入和触发器状态有关,没有输入变量的时序电路又称穆尔型电路。

7.如果某计数器中的触发器不是同时翻转,这种计数器称为异步计数器,n进制计数器中的n表示计数器的计数状态个数,最大计数值是n-1。

二、选择题:

(选择一个正确答案填入括号内,每题2分,共20分)

1.在四变量卡诺图中,逻辑上不相邻的一组最小项为:

(D)

A.m1与m3B.m4与m6

C.m5与m13D.m2与m8

2.L=AB+C的对偶式为:

(B)

A.A+BCB.(A+B)CC.A+B+CD.ABC

3.属于组合逻辑电路的部件是(A)。

A.编码器B.寄存器C.触发器D.计数器

4.T触发器中,当T=1时,触发器实现(C)功能。

A.置1B.置0C.计数D.保持

5.指出下列电路中能够把串行数据变成并行数据的电路应该是(C)。

A.JK触发器B.3/8线译码器

C.移位寄存器D.十进制计数器

6.某电路的输入波形uI和输出波形uO下图所示,则该电路为(C)。

A.施密特触发器B.反相器

C.单稳态触发器D.JK触发器

7.三极管作为开关时工作区域是(D)

A.饱和区+放大区B.击穿区+截止区

C.放大区+击穿区D.饱和区+截止区

8.已知逻辑函数与其相等的函数为(D)。

A.B.C.D.

9.一个数据选择器的地址输入端有3个时,最多可以有(C)个数据信号输出。

A.4B.6C.8D.16

10.用触发器设计一个24进制的计数器,至少需要(D)个触发器。

A.3B.4C.6D.5

1.下列电路中不属于时序电路的是C。

A.同步计数器B.异步计数器C.组合逻辑电路D.数据寄存器

2.CT74LS290计数器的计数工作方式有C种。

A.1B.2C.3D.4

3.3线—8线译码器有A。

A.3条输入线,8条输出线B.8条输入线,3条输出线

C.2条输入线,8条输出线D.3条输入线,4条输出线

4.一个五位的二进制加法计数器,初始状态为00000,问经过201个输入脉冲后,此计数器的状态为D。

A.00111B.00101C.01000D.01001

5.若将一TTL异或门输入端A、B当作反相器使用,则A、B端的连接方式为A。

A.A或B中有一个接1B.A或B中有一个接0

C.A和B并联使用D.不能实现

6.下列各种电路结构的触发器中哪种能构成移位寄存器(C)

A.基本RS触发器B.同步RS触

C.主从结构触发器D.SR锁存器

7.逻辑函数F(A,B,C)=AB+BC+AC'的最小项标准式为(D)。

A.F(A,B,C)=∑m(0,2,4)B.F(A,B,C)=∑m(1,5,6,7)

C.F(A,B,C)=∑m(0,2,3,4)D.F(A,B,C)=∑m(3,4,6,7)

8.设计一个把十进制转换成二进制的编码器,则输入端数M和输出端数N分别为(C)

A.M=N=10B.M=10,N=2C.M=10,N=4D.M=10,N=3

9.数字电路中的工作信号为(B)。

A.直流信号B.脉冲信号

C.随时间连续变化的电信号

10.L=AB+C的对偶式为:

(A)

A.A+BCB.(A+B)CC.A+B+CD.ABC

1.数字电路中的工作信号为(B)。

A.随时间连续变化的电信号B.脉冲信号C.直流信号

2.逻辑符号如图一所示,当输入,输入B为方波时,则输出F应为(C)。

A.“1”B.“0”C.方波

3.逻辑图和输入A,B的波形如图二所示,分析在t1时刻输出F为(A)。

A.“1”B.“0”C.任意

4.图三逻辑电路为(A)。

A.与非门B.与门C.或门D.或非门

图四

图三

5.逻辑电路如图四所示,输入A=0,B=1,C=1,则输出F1和F2分别为(D)。

A.B.C.D.

6.AB+BC+CA的“与非”逻辑式为(B)。

A.B.C.

7.逻辑电路如图五所示,其逻辑功能相当于一个(C)。

A.“与”非门B.“导或”门C.“与或非”门

图五

8.与二进制数10101010相应的十进制数为(C)。

A.110B.)210C.170

9.时序逻辑电路中一定是含(A)

A.触发器B.组合逻辑电路C.移位寄存器D