版图设计中的寄生参数分析Word格式文档下载.docx

《版图设计中的寄生参数分析Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《版图设计中的寄生参数分析Word格式文档下载.docx(5页珍藏版)》请在冰豆网上搜索。

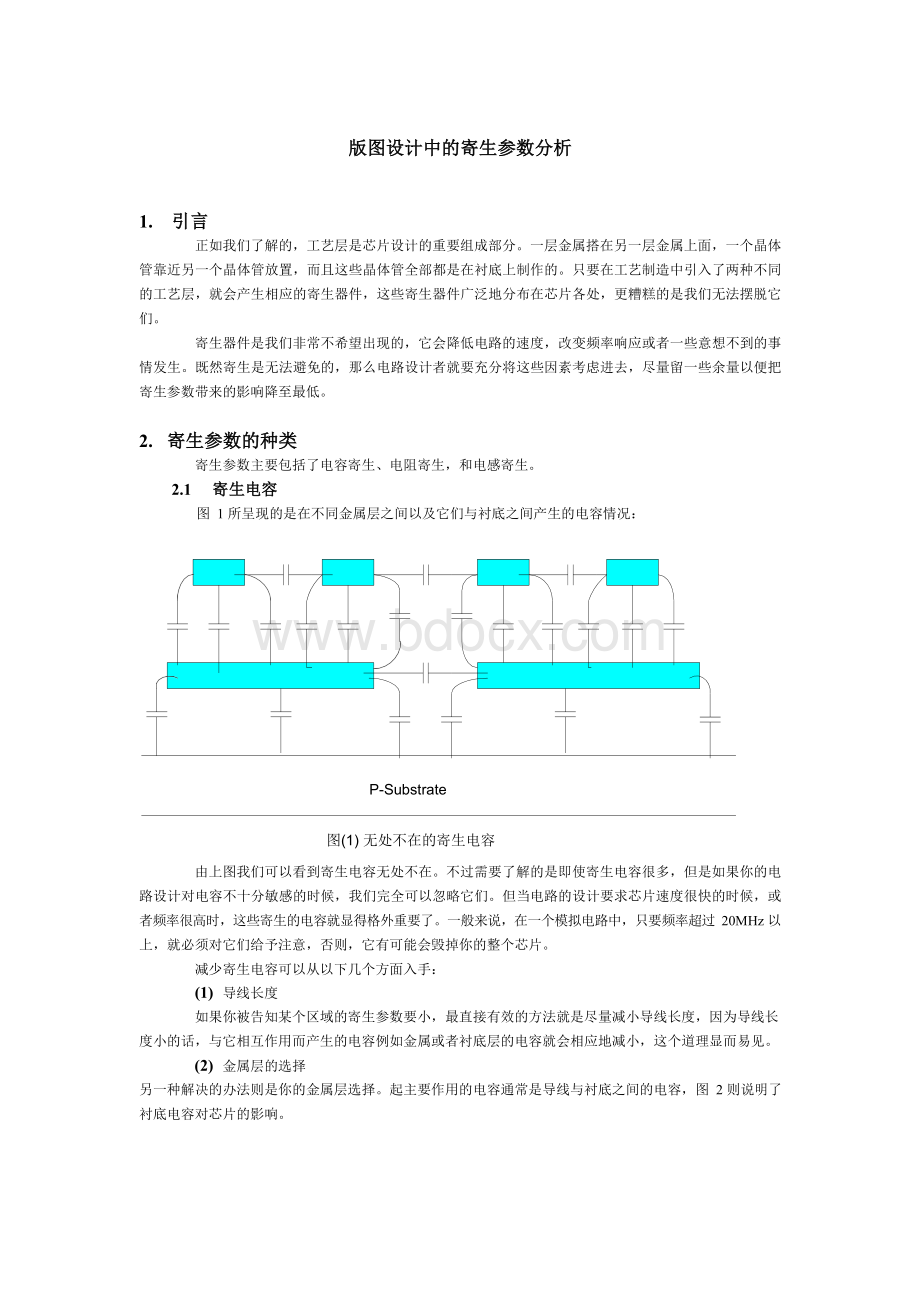

图

(1)无处不在的寄生电容

由上图我们可以看到寄生电容无处不在。

不过需要了解的是即使寄生电容很多,但是如果你的电路设计对电容不十分敏感的时候,我们完全可以忽略它们。

但当电路的设计要求芯片速度很快的时候,或者频率很高时,这些寄生的电容就显得格外重要了。

一般来说,在一个模拟电路中,只要频率超过20MHz以上,就必须对它们给予注意,否则,它有可能会毁掉你的整个芯片。

减少寄生电容可以从以下几个方面入手:

(1)导线长度

如果你被告知某个区域的寄生参数要小,最直接有效的方法就是尽量减小导线长度,因为导线长度小的话,与它相互作用而产生的电容例如金属或者衬底层的电容就会相应地减小,这个道理显而易见。

(2)金属层的选择

另一种解决的办法则是你的金属层选择。

起主要作用的电容通常是导线与衬底之间的电容,图2则说明了衬底电容对芯片的影响。

P-

Circuit2

Circuit1

Noisy Quiet

图

(2)衬底电容产生的噪声影响

如上所示,电路1和电路2都对地产生了一个衬底电容,衬底本身又有一个寄生电阻,这样一来电路1

的噪声就通过衬底耦合到电路2上面,这是我们不希望看到的。

(设法使所有的噪声都远离衬底)

因此我们改变一下金属层,通常情况下,最高金属层所形成的电容总是最小的。

电容大小与平板的间距成反比,一点距离的变化就能引起很大的差别。

另外值得注意的是并不是所有工艺的最高层金属与衬底产生的寄生电容都最小,它还与金属层的宽度等其它因素有关。

有些工艺中或许是M2对地的电容要比M4的对地电容大,所以我们不能只凭直觉来判断,一定要通过具体的计算来确认。

(3)金属叠加

在某些电路的上面布金属线,这是在数字自动布局布线中经常会遇到的情况。

各层金属相互交叠,所以在反相器、触发器等都存在寄生电容。

如果不加以干预的话,只是由布线器来操作,那么就有可能毁了你的芯片。

在模拟电路版图设计中,我们经常会人为的将敏感信号隔离开来,尽量避免在敏感电路上面走线,而只是将金属线走在电路之间,这样寄生的参数就小一些且相对容易控制。

2.2寄生电阻

寄生参数中另一个比较麻烦的要数寄生电阻了。

翻开工艺手册,我们经常能看到每层金属线能够承载的电流。

通过这个参数我们可以计算所需要的金属层宽度。

例如,有一根信号线需要承载1毫安的电流,而工艺手册注明每微米可以走0.5毫安的电

流,那么这根金属层的宽度至少要2微米,如图3所示。

2mm

1mA

图(3)电流通过导线连接

下面我们来计算一下这根导线因为寄生电阻而产生的IR压降。

导线的方块电阻Rsqu是0.05Ω,R=RsquL/W,V=IR所以计算得知电压为50毫伏。

它对于一个电压非常敏感的电路来讲就会有很大的影响。

如果这条导线的压降不能超过10毫伏,显然这个设计就是失

败的。

所以这就意味着我们必须将导线宽度增加5倍才能满足这一要求。

为了降低寄生电阻,就需要确保使用最厚的金属层。

正如我们了解的,一般情况下,最厚的金属线具有最低的方块电阻。

如果遇到相同的金属层厚度,也可以将这几条金属重叠形成并联结构,大大降低了电阻。

因此,并联布线是降低大电流路径电阻的有效方法,而且还能节省一定的面积。

如图3所示。

多晶(Poly)

P

N

M3

器件

M1

M2

压焊块

图(3)金属并联结构降低电阻

2.3寄生电感

当你的电路是在一个真正的高频的情况下工作时,导线也开始存在了电感效应。

解决寄生电感的方法就是试着去模拟它,把它当成电路中的一部分。

首先你需要尽早的完成你的布局,好让电路设计者较早的看到导线究竟能有多长,然后估计出可能引起的电感。

版图设计过程中尤其注意不要因为电感耦合而影响其它部分。

2.4器件的寄生参数

器件本身就具有寄生参数

(1)CMOS晶体管的例子

图(4)CMOS器件的寄生电容

当源或漏上的电压发生变化时,阱电容会使这一变化变慢。

当有一个电压加到栅上时,栅电容会使它变慢。

多晶硅栅的串联电阻与栅电容一起形成了一个RC时间常数,它使器件进一步变慢。

几乎器件的每一个部分都有某种电容以某种方式使器件的操作变慢。

减少CMOS器件寄生参数的技术就是减少栅的串联电阻。

任何其它在内的寄生参数是没有办法改变的。

如果我们降低了多晶硅栅的串联电阻,就降低了RC时间常数,从而改善了器件的速度。

我们可以通过把多晶硅栅分成多个“指状“结构,然后用导线将它们并联起来以降低电阻。

例如把器件分为两个就可以把RC时间常数降低4倍。

通过分成多个器件以及源漏共享可以大大减小CMOS晶体管上的寄生参数影响。

(2)双极型晶体管的例子

在双极晶体管中,集电极从注入的N区直接向下到衬底也存在寄生电容。

需要明白的是,对于双极晶体管器件来说,我们几乎没有什么手段加以改进。

不过,由于事先我们已经对器件进行了精确的测量并建立了模型,所以当电路设计者在进行设计的时候已经把这些因素都考虑进去了。

需要了解的是两个晶体管相互靠近时会对电路不利。

如图5所示,两个双极器件的集电极靠近放置,集电极和衬底之间不可避免地存在着寄生电容,而衬底本身也存在着寄生电阻将两个双极器件连接起来。

采用全定制技术可以把器件做得小一些。

通常是把一些较小的器件做成一个大的器件,将它们放在同一个阱里面,减少对衬底的寄生电容。

例如你有许多并联的双极型晶体管而不是许多单个的晶体管需要布线,可以考虑把它们的集电极合成一个。

N+

N P+

NPN

P

P+

B E C B E C

图(5)两个Bipolar器件的寄生参数

闩锁效应就是由于器件寄生而产生的典型电路,我们不妨分析一下它的产生原因以及如何更好地采取措施防范它的发生。

G2

输出

G1

V+

R2

R1

图(6)aCMOS对 图(6)bPN结的截面图

图(6)cPN结电路图

当两个MOS晶体管被制造的时候形成两个寄生双极型晶体管:

一个平行的NPN和一个垂直的PNP。

在正常情况下,结构中的PN结应为反向偏置。

然而,如果两个双极型晶体管因某种原因工作在放大区,电路会出现很多的正反馈,引起两个双极型晶体管传导剧烈。

我们来假设晶体管都是有源的而且NPN晶体管的基极电流因某种原因增加了I,那么NPN晶体管的集电极电流则增加了βI,如果R2被忽略,这个电流又由PNP晶体管的基极流入。

结果,PNP晶体管集电极电流增加到βnpnβpnpI,最后,如果R1被忽略,这个电流流回NPN晶体管的基极。

这个分析说明电路

产生一个与开始的扰动同向的增长电流,因此反馈是正向的。

在这种情况下,在电源和地之间就产生了巨大的电流通过,一直到电源关闭或者电路烧毁。

预防闩锁效应的方法:

(1)使用Guardring:

一方面可以降低Rwell和Rsub的阻值,另一方面可以阻止载子到达BJT的基极。

(2)Substratecontact和wellcontact应该尽量靠近source,并且Substratecontact和wellcontact的孔间距都应该尽量小,以降低Rwell和Rsub的阻值。

(3)使nmos尽量靠近GND,pmos尽量靠近VDD,保持足够的距离在pmos和nmos之间,以降低引发闩锁效应的可能。