基于AD9680的高速数据接口设计Word格式文档下载.docx

《基于AD9680的高速数据接口设计Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《基于AD9680的高速数据接口设计Word格式文档下载.docx(2页珍藏版)》请在冰豆网上搜索。

同时根据协议设计了扰码解扰模块,有效的提高了传输过程中的抗干扰性,最后对采集数据进行了分析。

关键词:

JESD204B;

高速串口;

解扰

DOI:

10.16640/ki.37-1222/t.2016.17.093

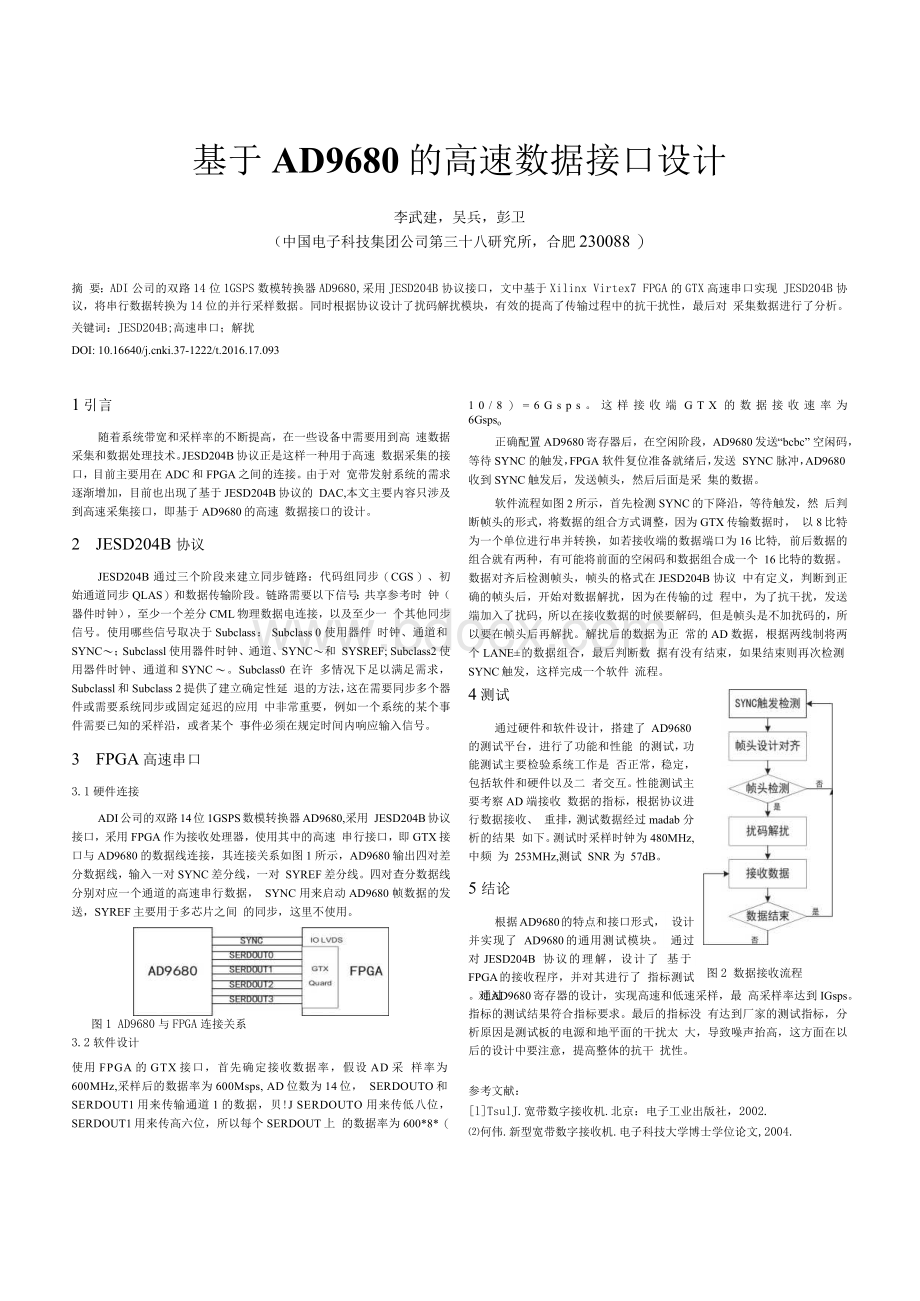

图2数据接收流程

1引言

随着系统带宽和采样率的不断提高,在一些设备中需要用到高速数据采集和数据处理技术。

JESD204B协议正是这样一种用于高速数据采集的接口,目前主要用在ADC和FPGA之间的连接。

由于对宽带发射系统的需求逐渐增加,目前也出现了基于JESD204B协议的DAC,本文主要内容只涉及到高速采集接口,即基于AD9680的高速数据接口的设计。

2 JESD204B协议

JESD204B通过三个阶段来建立同步链路:

代码组同步(CGS)、初始通道同步QLAS)和数据传输阶段。

链路需要以下信号:

共享参考时钟(器件时钟),至少一个差分CML物理数据电连接,以及至少一个其他同步信号。

使用哪些信号取决于Subclass:

Subclass0使用器件时钟、通道和SYNC〜;

Subclassl使用器件时钟、通道、SYNC〜和SYSREF;

Subclass2使用器件时钟、通道和SYNC〜。

Subclass0在许多情况下足以满足需求,Subclassl和Subclass2提供了建立确定性延退的方法,这在需要同步多个器件或需要系统同步或固定延迟的应用中非常重要,例如一个系统的某个事件需要已知的采样沿,或者某个事件必须在规定时间内响应输入信号。

3 FPGA高速串口

3.1硬件连接

ADI公司的双路14位1GSPS数模转换器AD9680,采用JESD204B协议接口,采用FPGA作为接收处理器,使用其中的高速串行接口,即GTX接口与AD9680的数据线连接,其连接关系如图1所示,AD9680输出四对差分数据线,输入一对SYNC差分线,一对SYREF差分线。

四对查分数据线分别对应一个通道的高速串行数据,SYNC用来启动AD9680帧数据的发送,SYREF主要用于多芯片之间的同步,这里不使用。

图1AD9680与FPGA连接关系

3.2软件设计

使用FPGA的GTX接口,首先确定接收数据率,假设AD采样率为600MHz,采样后的数据率为600Msps,AD位数为14位,SERDOUTO和SERDOUT1用来传输通道1的数据,贝!

JSERDOUTO用来传低八位,SERDOUT1用来传高六位,所以每个SERDOUT上的数据率为600*8*(10/8)=6Gsps。

这样接收端GTX的数据接收速率为

6Gspso

正确配置AD9680寄存器后,在空闲阶段,AD9680发送“bcbc”空闲码,等待SYNC的触发,FPGA软件复位准备就绪后,发送SYNC脉冲,AD9680收到SYNC触发后,发送帧头,然后后面是采集的数据。

软件流程如图2所示,首先检测SYNC的下降沿,等待触发,然后判断帧头的形式,将数据的组合方式调整,因为GTX传输数据时,以8比特为一个单位进行串并转换,如若接收端的数据端口为16比特,前后数据的组合就有两种,有可能将前面的空闲码和数据组合成一个16比特的数据。

数据对齐后检测帧头,帧头的格式在JESD204B协议中有定义,判断到正确的帧头后,开始对数据解扰,因为在传输的过程中,为了抗干扰,发送端加入了扰码,所以在接收数据的时候要解码,但是帧头是不加扰码的,所以要在帧头后再解扰。

解扰后的数据为正常的AD数据,根据两线制将两个LANE±

的数据组合,最后判断数据有没有结束,如果结束则再次检测SYNC触发,这样完成一个软件流程。

4测试

通过硬件和软件设计,搭建了AD9680的测试平台,进行了功能和性能的测试,功能测试主要检验系统工作是否正常,稳定,包括软件和硬件以及二者交互。

性能测试主要考察AD端接收数据的指标,根据协议进行数据接收、重排,测试数据经过madab分析的结果如下。

测试时采样时钟为480MHz,中频为253MHz,测试SNR为57dB。

5结论

根据AD9680的特点和接口形式,设计并实现了AD9680的通用测试模块。

通过对JESD204B协议的理解,设计了基于FPGA的接收程序,并对其进行了指标测试。

通过对AD9680寄存器的设计,实现高速和低速采样,最高采样率达到IGsps。

指标的测试结果符合指标要求。

最后的指标没有达到厂家的测试指标,分析原因是测试板的电源和地平面的干扰太大,导致噪声抬高,这方面在以后的设计中要注意,提高整体的抗干扰性。

参考文献:

[l]TsulJ.宽带数字接收机.北京:

电子工业出版社,2002.

⑵何伟.新型宽带数字接收机.电子科技大学博士学位论文,2004.