100千赫MOSFET感应加热电源的电路设计Word文档格式.docx

《100千赫MOSFET感应加热电源的电路设计Word文档格式.docx》由会员分享,可在线阅读,更多相关《100千赫MOSFET感应加热电源的电路设计Word文档格式.docx(12页珍藏版)》请在冰豆网上搜索。

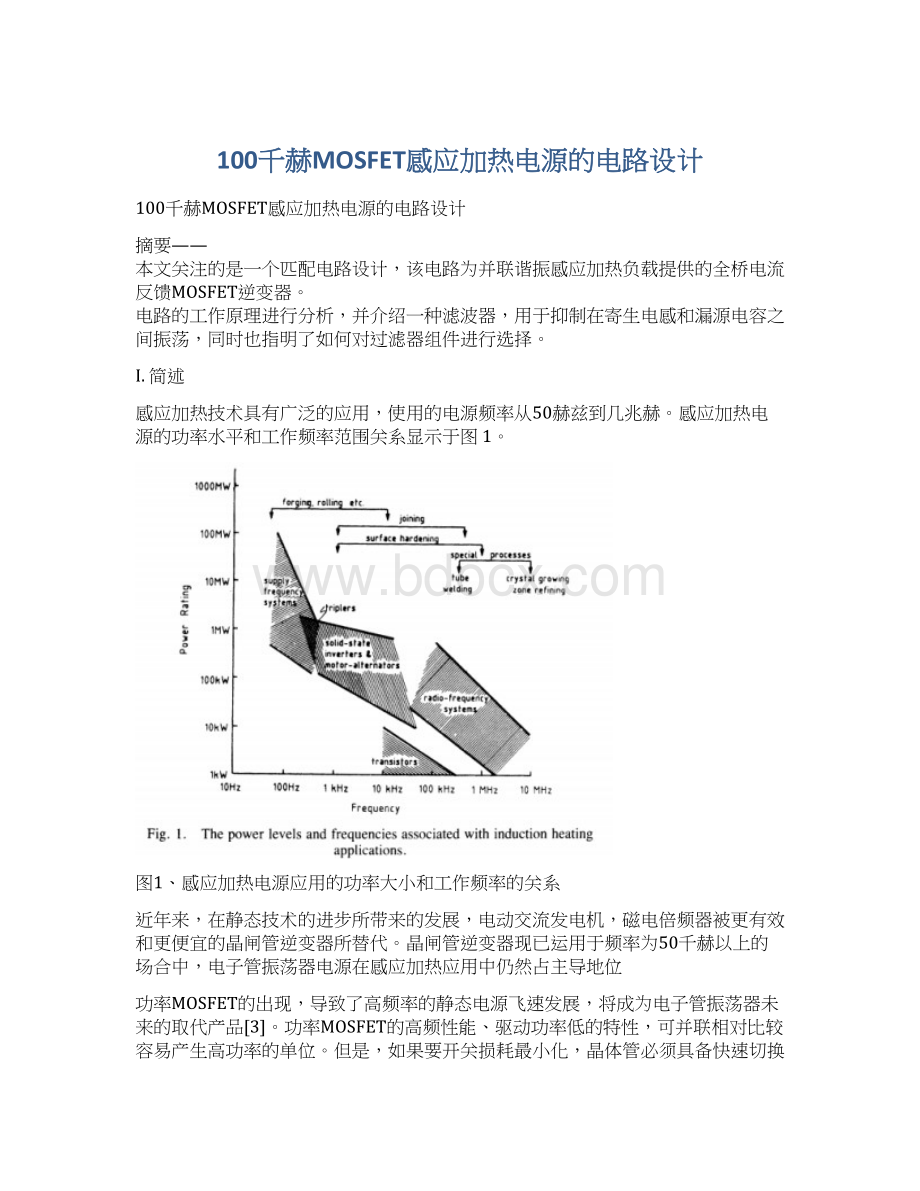

MOSFET只有少量的功率损耗(一个500-V8A的MOSFET通常为60瓦),这样一矩形开关配置必须具备快速切换时间,由此才能有较低的开关损耗。

图2所示的是想并联谐振感应加热负载提供的全桥电流反馈逆变器的电路结构。

流经储能电路的iL的电流波形如图3所示。

储能电路具有高Q值,因此它两端的电压波形近视为正弦,每个MOSFET两端的电压也应该是一个理想的对应的半正弦波。

对iL波形可以用傅里叶级数表示:

(Where—其中)

当所有开关接通时,重叠期间

必须防止阻塞器开路。

如果阻塞器和MOSFET的功率损失足够的小,可以认为是微不足道的,那么可以忽视频率高出基本频率值的那部分,储能电路功率可以表达为:

图2、基本的电流反馈逆变器

图3、储能电路iL的波形

其中,

是储能电路两端的电压峰值,并且

是阻塞器中的电流。

上述5千瓦的逆变器样机拓扑已建成。

每个开关示意图如图2所示,并由两个并连的晶体管来实现(类型IRF450)。

该晶体管的(在100℃外壳温度)最大电压电流值分别为500V和8A,对于开关频率为125千赫的电路,最大功率输出的计算为:

最大功率=

为使输出功率最大,逆变器需要提供储能电路一个阻抗

,

阻抗值的计算为:

对于5kw供应,这意味着提供一个阻值为

的阻抗

III.漏源极振荡的抑制

当MOSFET开关关闭时,寄生电感储存的能量将转移到两个MOSFET器件S1的漏源电容,流过CT和MOSFET固有的寄生二极管。

典型的波形如图4所示。

可以看出,振荡通过每个MOSFET漏源极两端,而没有在出现的储能电路。

为了降低MOSFET两端产生的电压尖峰,可以使用一个电阻电容缓冲器。

但在100千赫的频率下,损耗是相当大的,例如,一个10nF的电容与1

电阻串联,会导致6.25瓦特损耗,电阻器的发热提取和电阻的安装问题,,使其连接线较短,电感较低。

选择一个齐纳二极管钳位电压峰值MOSFET的将不得不为的钳位电压比正常运行时的振荡电流额定值更低的反向耐压可能的水平。

。

这个比例通常为1:

5。

齐纳管钳位存在保持导线长度短的问题,就想钼氧化物压敏电阻器使用一样。

如果单独使用一个电容,其值必须保持自身及典型寄生电感的谐振频率,低于最低的振荡电流谐波频率。

在振荡电流通过的电路中插入滤波器ZF,看起来像高频寄生电感感应产生的高频谐波,接在MOSFET两端的电容的尺寸要适当减小。

这形成一个抑制方法,包含由过滤器和电容器的阻断系列。

这样做的好处是,在过滤器使用时,这种方法是不可缺少的无损高Q值组件。

在电容和MOSFET要求导线长度短,这并不困难。

与振荡电流路径中的其他电感相比,这些导线的电感必须是很小的。

对于其他的抑制方法,这指的仅仅是寄生电感,但对如上所述过滤器ZF,导线电感应当比过滤器的有效电感要小。

IV.滤波器

滤波器ZF的目的是要维持承受本身的电压尖峰,从而保持该电压尖峰远离MOSFET器件。

滤波器ZF需要对开关频率有最低阻抗,同时对高频率的谐波有最大阻抗。

如果ZF是有效地做到这一点,它不应该包含电阻成分和Q值较高的有效成分。

串联谐振电路将满足以上特定的共振频率,其谐振频率的大小在开关频率值附近。

串联谐振电路的组件是C'

和L'

在电流反馈逆变器,开关S1和S2,S3可能在不同的时间导通,这是因为驱动电路元件特性的不同、,MOSFET本身的特性,或驱动器电路与MOSFET之间导线长度的细微差别引起的。

这将导致直流成分的产生和对电容C进行充电,直到超过其击穿电压,为克服这个问题,电感L“必须构成并联连接的L'

C'

系列组合,从而防止直流电压在C的出现。

这个预防措施,为了防止在电压反馈逆变器的变压器和主变压器与电容器串联时,直流电压的饱和。

电感L的并联,意味着滤波器ZF有效阻抗高于串联谐振频率下的C'

,其表达式为:

从图5中的滤波器ZF的阻抗轨迹图可以看出,并联谐振频率为w1,串联谐振频率为w2。

由于负载电流是通过ZF切换,对于电路中电流高频谐波成分,ZF可以通过一个高频电感Leff表示,并且该滤波器产生的电压尖峰就是V1,通过Leff切换谐波电流幅值比通过寄生电感的电流更大。

设计Leff时,其阻抗值应远大于寄生电感。

这意味着,在MOSFET上,由流经滤波器ZF的开关负载电流造成的振荡将远远超过寄生电感切换电流产生振荡。

在MOSFET的漏源极之间连接一个小电容可以克服这个问题。

一个MOSFET器件漏源极之间内电容大约为400pF,比漏源极之间外部电容CDS的值要小。

因此,在本质上,过滤器ZF是由一个跨接在每个的MOSFET漏源极之间的电容和一个与L'

和C'

组合系列并联的谐振电路电感L构成的(见图6。

)。

A、电压振荡的分析

通过对电压V1和MOSFET两端的电压的谐波成分分析,可以很好的理解过滤器的运行性能。

滤波器ZF产生的电压V1,可以假定的认为流经两个电路元件,第一个元件是Leff,第二个是集总电容,该电容是储能电路电容CT串联于四个外部相连的漏源电容并联组合。

当桥型电路两臂上的MOSFET处于导通时,另外两臂上的漏源电容就与滤波器ZF元件组合系列和储能电路并行连接。

漏源电容的总大小是4CDS,因此,Leff和电容的谐振频率即Wres,Wres的计算公式为:

其中Ws是叫开关频率。

由于储能电路的阻抗轨迹能在该频率下达到最大值,在此以后V1的一次谐波分量就会衰减。

并且,滤波器ZF在此开关频率下,阻抗值比较小,因此,只有iL的二次和高次谐波分量才能对V1产生可观的影响效果。

由此V1的一个函数表达式为:

其中,Ws是角开关频率。

图6、逆变器的原理图---储能电路、滤波器、静态电感、和外端漏源电容

图7、逆变器原理图的储能电路、滤波器

括号中的项的差别是两个余弦波的幅值大小不同,而不是频率的差异。

随着n从2变化到无穷大,括号中的项在n等于2是取最大值。

这个表达式在n=2时取得的最大值大小取决于tDB和T的大小。

tDB的大小取决于MOSFET的通断时间和驱动电路和功率电路元件的属性值。

为确保在不同负载和驱动电路情况下,滤波器能正常可靠的运行,需要考虑括号中的这项在最坏的情况。

MOSFET两端的电压振荡n次谐波分量为:

其中,V1,n是V1的n次谐波分量。

V.滤波器的实验验证

在商用感应加热装置中,逆变桥开关频率各不相同,因此,储能电路常常处于谐振状态。

这种变化是必要的,因为工作线圈的电路参数在整个加热回路中各不相同,同时储能电路的谐振频率也会由此发生改变。

储能电路和滤波器ZF的共同作用,避免滤波器ZF不再出现低阻抗的问题,这是因为在加热周期循环中,这个值是会发生变化的。

结合滤波器ZF和储能电路的使用,可以减少元件的数量。

修改后的振荡电路如图8所示。

显示了矩形负载电流的基本组成部分。

Ls是MOSFET和连接在储能电路之间的寄生电感。

修正后的储能电路YMOD为:

其中QL是工作线圈的负载Q值,Qu是电感

的Q值。

B.工作线圈的估算

非负载工作线圈与一个并联电容发生谐振。

通过测量电抗器直流分量、线圈两端的电压分量、储能电路谐振阻抗值,工作线圈的Q值由此可以计算。

另外,工作的线圈的Q值需要进一步的计算。

50nF的工作线圈在250KHZ发生谐振,因此,它的电感是8.1

电路的电压电流波形如图4所示。

(波形在低电压下,充分利用示波器的带宽而取得)二元并联谐振电路的谐振阻抗ZD为:

要调整逆变器的频率为储能电路的共振频率,这一频率就发生变化,止动器的直流电流分量也将被监视。

当直流电流最低,其中一个并联谐振频率将反馈给储能电路。

由于直接电流是0.1A和线圈电压28V,工作线圈Q值是24。

C.实验结果

修正后的储能电路中,LT=8.1uH(Q=24)、L"

=9.8uH(Q=16),CT=50nF、CDs=20nF.电压和电流如图9中所示。

图9(a)表明,MOSFET的端电压不受振荡的影响。

图4(a)和图9(a)相比,过滤器的掺入提高了晶体管的维持电压利用率的能力,至少提高了百分之三十。

对于24v相同的直流母线电压,图4(b)中的电流峰值大约是图9(b),这是因为如图8中在这个并联谐振频率下,修正后的储能电路阻抗值比初始的二元并联储能电路中的阻抗值更低。

相比于图9(b)中的波形,如图4(b)中MOSFET漏极电流的均方根计算较为困难。

但通过检验,难度就几乎减半了。

因此,利用修正后的储能电路,MOSFET开关容量的使用率就提高了30%,并且漏极电流的波形也可以预测,将变的更好。

电路布局的优化问题已减少,因为漏电流波形取决于集总电路元件,而不是导致寄生电感。

该单位的设计也简化了,因为MOSFET的电流波形,等等,都更适合进行分析。

Ls的估计可以从MOSFET漏源两端到工作线圈两端的基本组成元件的工作电压比。

Ls可以是

波形是在储能电路的最低并联谐振频率取得的。

通过监视母线电流的最小值,可以得到这个谐振频率。

修正后的储能电路存在两个并联谐振频率,如图8所示,务必要注意较小的那个频率值。

在这个频率条件下,Ls的电抗值要比4CDS的电抗值要低,例如,在140kHz时,前者为0.6欧,后者为5.5欧。

在忽略Ls的情况下,通过使用电脑,修改后的振荡电路(9)准许导纳轨迹的问题已经得到解决,较低的并联谐振频率被认为是140KHz。

这几乎与实验结果完全相同(见图9。

),从而支持在图8提出使用的电路模型。

在图9(d)可以看出电感L“维持高次谐波的电压。

对于高次谐波成分,电容CT是一个低阻抗,因而在高次谐波电压情况下,电容CT相对于电感L“的影响作用非常小,如图示9(e)。

以这种方式减少振荡的缺点有:

第一,MOSFET的总漏源电容不再是微不足道,而是构成的储能电路的一部分。

流经4CDs(IcM)的环流元件是有MOSFET器件实现的,如果tDB被认为是可以忽略的,那么它的均方根的值可以有以下公式计算:

单个MOSFET管的电流峰值

计算公式为:

由于ID的值在0.2时,作为修改后的储能电路反馈电流,

的计算结果为0.8A,与实验值相一致(见图9(b))。

这种方法的第二个缺点是在L"

的额外损耗,虽然工作中使用了电脑Spice软件包对电路L"

和LT在工件中的耦合情况进行软件仿真分析研究,这个不足对高Q线圈和紧密耦合到负载的