可编程单脉冲发生器设计FPGA.docx

《可编程单脉冲发生器设计FPGA.docx》由会员分享,可在线阅读,更多相关《可编程单脉冲发生器设计FPGA.docx(16页珍藏版)》请在冰豆网上搜索。

可编程单脉冲发生器设计FPGA

可编程单脉冲发生器设计

一、功能描述:

本设计实现一个可编程单脉冲发生器,具体功能如下:

1.异步信号复位,复位后信号输出重新开始。

2.复位后5个时钟周期时,产生一个脉冲,对输入的脉冲宽度参数读取。

3.当有按键使能时,输出脉冲信号,重复再按使能键,无效。

4.使能按键后产生的单脉冲的上升沿与时钟取得同步。

5.产生的脉冲信号的最大宽度为255。

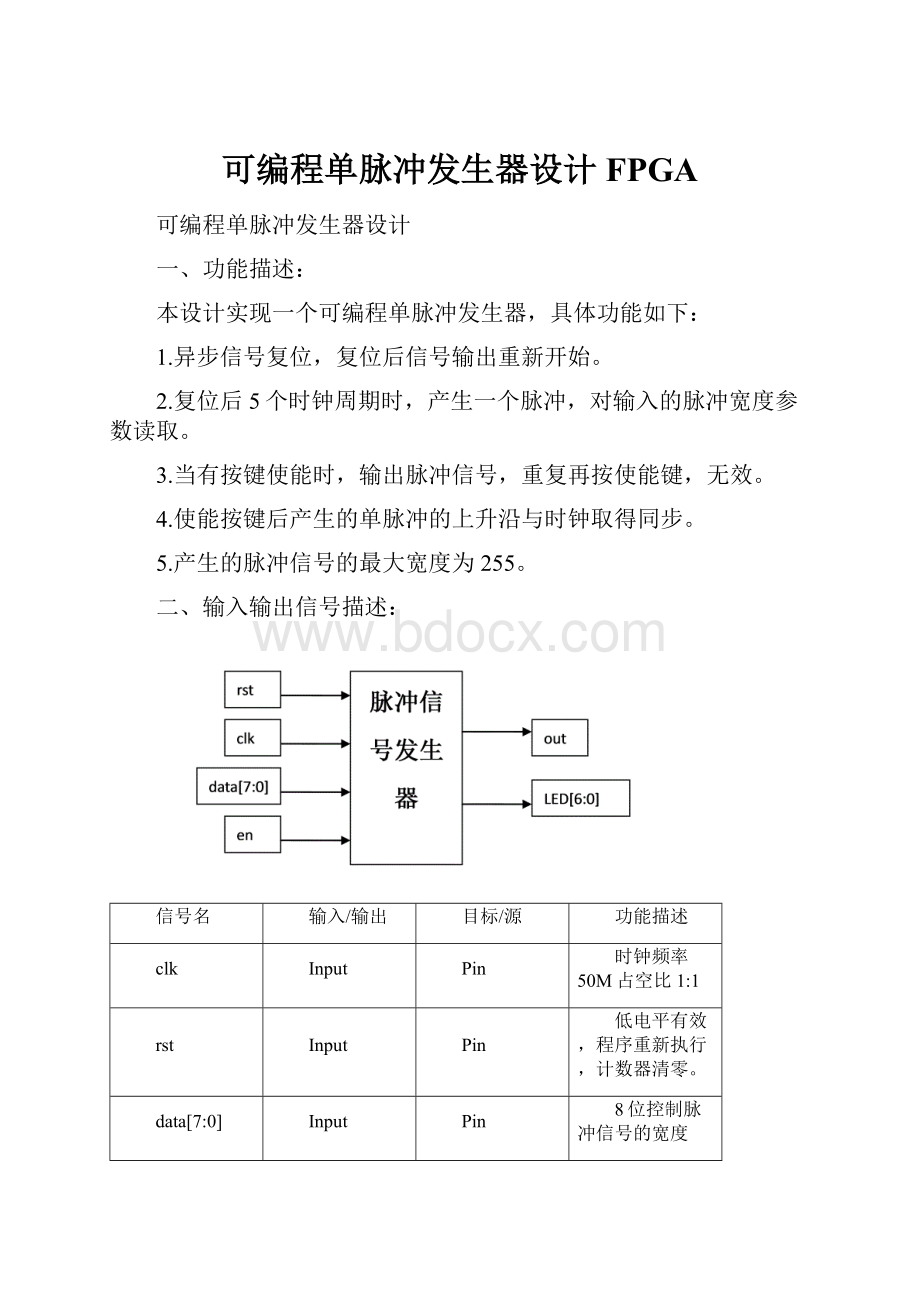

二、输入输出信号描述:

信号名

输入/输出

目标/源

功能描述

clk

Input

Pin

时钟频率50M占空比1:

1

rst

Input

Pin

低电平有效,程序重新执行,计数器清零。

data[7:

0]

Input

Pin

8位控制脉冲信号的宽度

out

Output

Pin

输出信号

LED[6:

0]

Output

Pin

接入数码管显示data输入值

三、顶层划分:

系统结构框图

顶层模块说明:

1、counter:

计数比较,确保输出信号宽度为输入data值;

2、sync:

将按键产生的单脉冲的上升沿与时钟取得同步;

3、T_trigger:

T触发器模块,锁按键信号,使按键只能第一次有效;

4、preset_parameter:

预置脉冲参数;

5、LED:

将输入data用数码管输出显示。

设计说明:

设计分为计数比较、按键同步、预置脉冲参数、T触发器模块、LED显示五个模块。

计数比较模块:

计数延时,由输入的宽度参数data的不同而得到不同宽度的脉冲。

按键同步模块:

使按键产生的单脉冲的上升沿与时钟取得同步。

预置脉冲参数:

在系统进行复位操作的5个时间单位后,将输入的脉冲参数data预置到flag_data中。

T触发器模块:

T触发器模块,锁按键信号,使按键只能第一次有效。

LED显示模块:

将脉冲宽度的预置值和计数模块的计数值转换为数码管输出显示。

四、子模块描述:

4.1、counter:

计数判断输出模块

1、功能描述

计数延时,由输入的宽度参数data的不同而得到不同宽度的脉冲。

2、管脚描述

信号名称

输入/输出

源

目标

功能描述

clk

Input

Pin

时钟信号50MHz

rst

Input

Pin

复位信号,低电平有效

data_in[7:

0]

Input

Pin

脉冲宽度参数

Q_in

Input

Pin

按键使能标志

out

Output

Pin

脉冲输出

3、实现说明

复位后输出out为0。

当Q_in按键使能标志有效时,cnt[7:

0]从零开始计数,当cnt4、模块验证

1.正常运行观测其输出变化;复位观测。

2.将cnt接数码管显示,观测脉冲宽度。

4.2、sync:

同步按键与时钟信号模块

1、功能描述

使按键产生的单脉冲的上升沿与时钟取得同步。

2、管脚描述

信号名称

输入/输出

源

目标

功能描述

clk

Input

Pin

时钟信号50MHz

rst

Input

Pin

复位信号,低电平有效

en_in

Input

Pin

按键使能

en_out

Output

Pin

同步后的按键使能

3、实现说明

当按键被按下(即en_in=0)时,将Q1<=1,在clk为高电平时将Q2<=Q1,en_out<=Q2;clr=en_in&en_out,当clr有效时Q1<=0。

复位信号rst有效时,Q1<=0,Q2<=0,en_out<=0。

sync结构图:

4、模块验证

1.复位验证。

4.3、T_trigger:

T触发器模块

1、功能描述

T触发器模块,锁按键信号,使按键只能第一次有效。

2、管脚描述

信号名称

输入/输出

源

目标

功能描述

rst

Input

Pin

复位信号,低电平有效

in

Input

Pin

T触发器输入

Q_out

Output

Pin

T触发器输出

3、实现说明

当复位时,Q_out<=0;其他时输出结果为Q_out<=in^Q_out。

4、模块验证

复位验证。

4.4、preset_parameter:

预置脉冲参数模块

1、功能描述

在系统进行复位操作的5个时间单位后,将输入的脉冲参数data预置到flag_data中。

2、管脚描述

信号名称

输入/输出

源

目标

功能描述

clk

Input

Pin

时钟信号50MHz

rst

Input

Pin

复位信号,低电平有效

data[7:

0]

Input

Pin

输入的脉冲宽度参数

flag_data[7:

0]

Output

Pin

预置脉冲宽度值

3、实现说明

系统复位后sum从零开始计数,当sum=5时,将flag_data<=data

4、模块验证

复位后检测sum值和flag_data值。

4.5、LED:

数码管显示模块

1、功能描述

将脉冲宽度的预置值和计数模块的计数值转换为数码管输出显示。

2、管脚描述

信号名称

输入/输出

源

目标

功能描述

rst

Input

Pin

复位信号,低电平有效

data[2:

0]

Input

Pin

输入数值

cnt_num[7:

0]

Input

Pin

计数模块中cnt值

led1[6:

0]

Output

Pin

接数码管显示输入的data百位

Led2[6:

0]

Output

Pin

接数码管显示输入的data十位

Led3[6:

0]

Output

Pin

接数码管显示输入的data个位

Led4[6:

0]

Output

Pin

接数码管显示计数模块中cnt的百位

Led5[6:

0]

Output

Pin

接数码管显示计数模块中cnt的十位

Led6[6:

0]

Output

Pin

接数码管显示计数模块中cnt的个位

3、实现说明

将data和cnt的输入值转换为数码管显示输出。

对百位取余作为百位的值,对百位取余再对十位取整作为十位的值,对个位取余作为个位的值。

五、验证方案:

1、结果验证

将程序下载至实验板,接示波器后,先设置脉冲宽度再复位,最后按键,观测示波器显示的波形信号。

2、复位验证

下载到实验板,让其运行一段时间,进行复位,观测变化。

3、仿真验证

六、实验截图:

前仿真波形:

QuartusII综合:

后仿真波形:

分配管脚:

程序运行最高速度:

七、源程序代码:

顶层模块:

modulepulser(data,en,rst,clk,out,led1,led2,led3,led4,led5,led6);

input[7:

0]data;

inputen,rst,clk;

outputout;

output[6:

0]led1,led2,led3,led4,led5,led6;

wirex,m;

wire[7:

0]d,y;

syncS(.clk(c),.rst(rst),.en_in(en),.en_out(m));

counterC(.Q_in(x),.clk(clk),.rst(rst),.data_in(d),.out(out),.cnt(y));

preset_parameterP(.clk(clk),.rst(rst),.data(data),.flag_data(d));

T_triggerT(.rst(rst),.in(m),.Q_out(x));

LEDL(.led_data(d),.cnt_num(y),.rst(rst),.led1(led1),.led2(led2),.led3(led3),.led4(led4),

.led5(led5),.led6(led6));

endmodule

计数判断输出模块:

counter

modulecounter(Q_in,clk,rst,data_in,out,cnt);

input[7:

0]data_in;

inputQ_in,clk,rst;

output[7:

0]cnt;

outputout;

regout;

reg[7:

0]cnt;

always@(posedgeclkornegedgerst)

begin

if(!

rst)

begin

cnt<=0;

out<=0;

end

elseif(Q_in&&cntbegin

out<=1;

cnt<=cnt+1;

end

else

begin

out<=0;

end

end

endmodule

同步按键与时钟信号模块:

sync

modulesync(clk,rst,en_in,en_out);

inputen_in,clk,rst;

outputen_out;

regQ1,Q2,en_out;

wireclr;

assignclr=en_in&en_out;

always@(en_inorrstorclk)

begin

if(!

rst)

begin

Q1<=0;

Q2<=0;

en_out<=0;

end

elseif(!

en_in)Q1<=1;

elseif(clr)Q1<=0;

elseif(clk)

begin

Q2<=Q1;

en_out<=Q2;

end

end

endmodule

T触发器模块:

T_trigger

moduleT_trigger(rst,in,Q_out);

inputrst,in;

outputQ_out;

regQ_out;

always@(inorrst)

begin

if(!

rst)Q_out<=0;

elseQ_out<=in^Q_out;

end

endmodule

预置脉冲参数模块:

preset_parameter

modulepreset_parameter(clk,rst,data,flag_data);

inputclk,rst;

input[7:

0]data;

output[7:

0]flag_data;

reg[7:

0]flag_data;

reg[2:

0]sum;

regflag_sum;

always@(posedgeclkornegedgerst)

begin

if(!

rst)

begin

sum<=0;

flag_sum<=0;

flag_data<=0;

end

elseif(flag_sum==0&&sum==5)

begin

flag_data<=data;

flag_sum<=flag_sum+1;

end

elseif(flag_sum==0&&sum<5)sum<=sum+1;

end

endmodule

数码管显示模块:

LED

moduleLED(led_data,cnt_num,rst,led1,led2,led3,led4,led5,led6);

input[7:

0]led_data,cnt_num;

inputrst;

output[6:

0]led1,led2,led3,led4,led5,led6;

reg[6:

0]led1,led2,led3,led4,led5,led6;

reg[6:

0]LED[9:

0];

always@(rstorcnt_numorled_data)

begin

LED[0]=7'b1000000;LED[1]=7'b1111001;LED[2]=7'b0100100;LED[3]=7'b0110000;

LED[4]=7'b0011001;LED[5]=7'b0010010;LED[6]=7'b0000010;LED[7]=7'b1111000;

LED[8]=7'b0000000;LED[9]=7'b0010000;

if(!

rst)

begin

led1<=0;

led2<=0;

led3<=0;

led4<=0;

led5<=0;

led6<=0;

end

else

begin

led1<=LED[led_data/100];

led2<=LED[led_data%100/10];

led3<=LED[led_data%10];

led4<=LED[cnt_num/100];

led5<=LED[cnt_num%100/10];

led6<=LED[cnt_num%10];

end

end

endmodule

测试激励模块:

`timescale10ns/1ns

moduletest;

regclk,rst,en;

reg[7:

0]data;

wireout;

wire[6:

0]led1,led2,led3,led4,led5,led6;

pulserP(data,en,rst,clk,out,led1,led2,led3,led4,led5,led6);

initial

begin

clk='b1;

forever#1clk=~clk;

end

initial

begin

rst='b0;en=1;data='d14;#1rst=0;

#1rst='b1;

#6en=0;#1en=1;

#50data='d220;#1rst=0;#1rst='b1;#6en=0;#1en=1;

#500data='d113;#1rst=0;#1rst='b1;#6en=0;#1en=1;

end

endmodule