ARM处理器CACHE详解.docx

《ARM处理器CACHE详解.docx》由会员分享,可在线阅读,更多相关《ARM处理器CACHE详解.docx(23页珍藏版)》请在冰豆网上搜索。

ARM处理器CACHE详解

ARM920T的MMU与Cache

目录

虚拟地址和物理地址的概念

虚拟内存管理ﻫ ARM920T的CP15协处理器

MMUﻫ Cache

操作MMU和Cache的内核启动代码

参考资料索引

虚拟地址和物理地址的概念

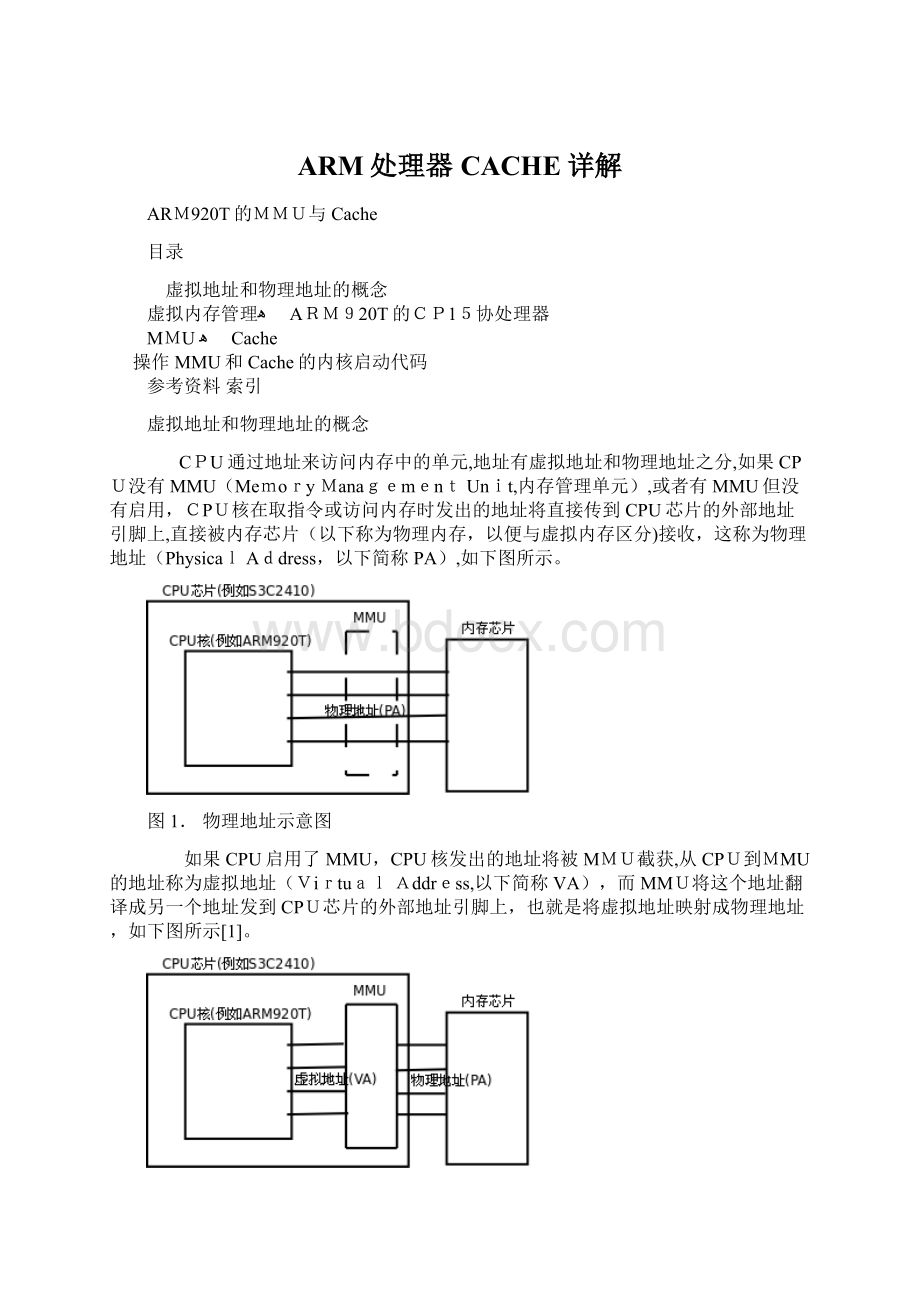

CPU通过地址来访问内存中的单元,地址有虚拟地址和物理地址之分,如果CPU没有MMU(MemoryManagementUnit,内存管理单元),或者有MMU但没有启用,CPU核在取指令或访问内存时发出的地址将直接传到CPU芯片的外部地址引脚上,直接被内存芯片(以下称为物理内存,以便与虚拟内存区分)接收,这称为物理地址(PhysicalAddress,以下简称PA),如下图所示。

图1.物理地址示意图

如果CPU启用了MMU,CPU核发出的地址将被MMU截获,从CPU到MMU的地址称为虚拟地址(VirtualAddress,以下简称VA),而MMU将这个地址翻译成另一个地址发到CPU芯片的外部地址引脚上,也就是将虚拟地址映射成物理地址,如下图所示[1]。

图2.虚拟地址示意图

MMU将虚拟地址映射到物理地址是以页(Page)为单位的,对于32位CPU通常一页为4K。

例如,虚拟地址0xb700 1000~0xb7001fff是一个页,可能被MMU映射到物理地址0x2000~0x2fff,物理内存中的一个物理页面也称为一个页框(Page Frame)。

虚拟内存管理

现代操作系统充分利用MMU提供的VA到PA的映射机制来做内存管理,以下称为虚拟内存管理(VirtualMemoryManagement)。

首先看下面的例子:

例 1.进程的地址空间

这是bash进程的虚拟地址空间,32位CPU的虚拟地址空间是4GB,也就是0x00000000-0xffffffff,该进程占用的地址范围近似为0x00000000-0xbfffffff,地址范围0xc0000000-0xffff ffff由内核占用,用户进程不允许访问。

在这个bash进程的地址空间中,从0x0804 8000开始的668K的权限为r-x--,表示代码段,从0x080ef000开始的24K的权限是rw---,表示数据段,从0x080f 5000开始的2056K的权限也是rw---,但是没有对应任何磁盘文件,而是用[ anon](anonymous,匿名)来表示,这是堆所占的空间,从0xb7c6d000开始是共享库和资源文件的映射空间,每个共享库也分为代码段和数据段,用不同的权限表示,可以看到,从堆空间到下面的共享库映射空间之间有很大的地址空洞,最末从0xbfad4000开始的84K是栈空间。

为什么需要虚拟内存管理呢?

可以从以下几个方面来理解。

第一,让每个进程有独立的地址空间是引入虚拟内存管理的最主要目的。

所谓独立的地址空间是指,不同进程中的同一个VA被MMU映射到不同的PA,并且在某一个进程中访问任何地址都不可能访问到另外一个进程的数据,这样使得任何一个进程由于程序BUG或恶意代码所导致的非法内存访问都不会意外改写其它进程的数据,不会影响其它进程的运行,从而保证了整个系统的稳定性。

另一方面,每个进程都认为自己独占4GB的地址空间,编写程序会比较方便,不必为每个进程分配一个地址范围,而是每个进程都可以使用一个完整的地址空间中的任何地址。

我们继续用上面的例子来理解,再打开一个shell窗口,用pmap命令看一下这个新的bash进程的地址空间,可以发现和刚才的地址空间布局差不多:

该进程也占用了0x0000 0000-0xbfffffff的地址空间,代码段也是从0x0804 8000开始的668K,数据段也是从0x080ef000开始的24K,共享库的内存布局也差不多。

这个进程和刚才的例子是同一个系统中同时运行着的两个进程,它们都认为自己占有0x00000000-0xbfff ffff的地址空间,并且它们的数据段的地址范围是重合的,但是两个进程各自干各自的事情,显然数据段中的数据是不同的,正是因为不同进程中的同一个VA被映射到了不同的PA,所以两个进程的数据段其实是在不同的物理地址上,如下图所示。

图 4.进程地址空间是独立的

从图中还可以看到,两个进程都是bash进程,代码段是一样的,并且代码段是只读的,不会被改写,因此操作系统会安排两个进程的代码段共享相同的物理内存。

由于每个进程都有自己的一套VA到PA的映射表,整个地址空间中的任何VA都在每个进程自己的映射表中查找相应的物理地址,因此不可能访问到其它进程的地址,也就没有可能意外改写其它进程的数据。

第二,引入VA到PA的映射也会给分配和释放内存带来方便,物理上不连续的空间可以映射为逻辑上连续的虚拟地址空间。

比如要malloc一块很大的内存空间,而物理内存虽然有足够的空闲内存,却没有足够大的连续空闲内存,这时就可以分配多个不连续的物理页面,而映射为连续的虚拟地址范围。

如下图所示。

图5.不连续的PA可以映射为连续的VA

第三,一个系统如果同时运行着很多进程,为各进程分配的内存之和可能会大于实际可用的物理内存,虚拟内存管理使得这种情况下各进程仍然能够正常运行。

因为各进程分配的只不过是虚拟内存的页,这个页的内容可以映射到物理内存的页框,也可以临时保存到磁盘上而不占用物理内存的页框,磁盘上这一部分称为交换设备(S),可能是一个磁盘分区,也可能是一个磁盘文件。

当物理内存不够时将物理内存中不常用的页框临时保存到磁盘上,而当用到这些页框时再从磁盘加载回内存,这称为换页(Paging)因此:

ﻫ 系统中可分配的内存总量= 物理内存的大小 + 交换设备的大小

如下图所示。

第一张图是换出(Pageout),将物理页面的内容保存到磁盘,并解除地址映射,释放物理页面。

第二张图是换入(Pagein),从空闲的物理页面中分配一个,将磁盘暂存的页面加载回内存,并建立地址映射。

图6. 换页

第四,虚拟内存管理可以控制物理页面的访问权限。

物理内存本身是不限制访问的,任何地址都可以读写,而操作系统要求实现各种不同的访问权限,在先前的例子中我们已经看到,代码段要求是rx的,数据段要求是rw的,用户进程不能访问属于内核的地址空间,这些都是操作系统和MMU配合实现的。

MMU中还实现了一种访问限制是关于Cache的。

Cache(高速缓存)是CPU内的一小块高速RAM,用来缓存最近访问过的内存数据,CPU访问Cache的速度是访问内存速度的数十倍,所以有效地利用Cache可以大大提高计算机的整体性能。

CPU核要访问数据时首先发出VA,Cache利用VA查找相应的数据有没有被缓存[2],如果有就通知CPU核,如果是读操作就直接将Cache中的数据传给CPU核中的寄存器,如果是写操作就直接改写Cache中的数据,而不需要访问物理内存。

但是,有些VA所对应的PA并不是物理内存中的地址而是设备寄存器的地址,对这些寄存器进行读写并不是为了保存数据,而是对设备做特殊操作,这种VA通常是不允许缓存的,因为如果缓存了,对VA的读写将只在Cache中起作用,而不会传到设备寄存器对设备进行操作。

以串口的收发寄存器为例,如果收发寄存器地址被缓存了会出现什么问题呢?

如下图所示。

如果发送寄存器的地址被缓存起来,CPU核往发送寄存器的地址做写操作都写到Cache中去了,发送寄存器并没有及时得到数据,也就不能及时发送,此外,CPU核先后发出的1、2、3三个数据都会写到Cache中的同一个地址,最后Cache中只保存了第3个数据,如果这时Cache的数据写回到发送寄存器去,只能把第3个数据发送出去,前两个数据就丢失了。

与此类似,如果接收寄存器的地址被缓存起来,CPU核在读第1个数据时,Cache会从接收寄存器读进来缓存,然而接收寄存器后面收到2、3两个数据Cache并不知道,因为Cache把接收寄存器当作内存,并且相信内存中的数据是不会自己变的,所以以后每次CPU核读接收寄存器时,Cache都提供给CPU核第1个数据。

ARM920T的CP15协处理器

ARM920T的MMU和Cache都集成在CP15协处理器中,MMU和Cache的联系非常密切,本节首先从总体上介绍MMU、Cache和CPU核是如何协同工作的,后面两节分别讲解MMU和Cache的细节。

三星公司的S3C2410是一种很常见的采用ARM920T的芯片,涉及到具体的芯片时我们以S3C2410为例。

以下是CP15协处理器的寄存器列表(摘自[S3C2410用户手册]),和CPU核的r0到r15寄存器一样,协处理器寄存器也是用0到15来编号,在指令中用4个bit来表示寄存器编号,有些协处理器寄存器有影子寄存器,这种情况下对同一个编号的寄存器使用不同的选项读或者写实际上访问的是不同的寄存器,后文用到某个寄存器时会详细说明它的功能。

表1. CP15协处理器的寄存器列表

对CP15协处理器的操作使用mcr和mrc两条协处理器指令,这两条指令的记法是从后往前看:

mcr是把r(CPU核寄存器)中的数据传送到c(协处理器寄存器)中,mrc则是把c(协处理器寄存器)中的数据传送到r(CPU核寄存器)中。

对CP15协处理器的所有操作都是通过CPU核寄存器和CP15寄存器之间交换数据来完成的。

下图是协处理器的指令格式(摘自[S3C2410用户手册])。

图 8.协处理器指令格式

和其它ARM指令一样,Cond是条件码,bit20是L位,表示该指令是读还是写,如果L=1就表示Load,从外面读到CPU核中,也就是mrc指令,如果L=0就表示Store,也就是mcr指令。

[11:

8]这四个位是协处理器编号,CP15的编号是15,因此是4个1。

CRn是CP15寄存器编号,Rd是CPU核寄存器编号,各占4个位。

对于CP15协处理器,规定opcode1应该为0,opcode2和CRm是指令的选项,具体含义取决于不同的寄存器。

虽然这里介绍了协处理器的寄存器编号和相关指令,但读者只需了解对协处理器是这样进行操作的就可以了,我们的重点是讲解MMU和Cache的基本概念,具体各种操作的指令该怎么写可以参考[S3C2410用户手册]。

MMU是如何把VA映射成PA的呢?

从图4“进程地址空间是独立的”来看,好像是有一张VA转PA的表,给一个VA查表就可以查到PA,实际上并不是这么简单,通常要有一个多级的查表过程,对于ARM体系结构是两级查表,对于一些64位体系结构则需要更多级。

看下面的图示。

图9.Translation Table Walk

首先将32位的VA[3]分成三段,前两段[31:

20]和[19:

12]作为两次查表的索引,第三段[11:

0]作为页内的偏移。

查表的步骤如下:

1CP15协处理器的TTB寄存器(看看表 1“CP15协处理器的寄存器列表”中这是第几个寄存器?

C2)中保存着第一级页表(TranslationTable)的基地址,这个基地址指的是PA,也就是说页表是直接按这个地址存在物理内存中的。

2以TTB中的内容为基地址,以VA[31:

20]为索引在表中查出一项(想一下这个表中一共有多少项?

4096项),这个表项中保存着第二级页表(CoarsePageTable)的基地址,同样是物理地址,也就是说第二级页表也是直接按这个地址存在物理内存中的。

3以VA[19:

12]为索引在第二级页表中查出一项(想一下这个表中一共有多少项?

256项),这个表项中就保存着物理页面的基地址,先前我们说虚拟内存管理是以页为单位的,一个虚拟内存的页映射到一个物理内存的页框,从这里就可以得到印证,因为查表是以页为单位来查的。

4有了物理页面的基地址之后,加上VA[11:

0]这个偏移量就可以取出相应地址上的数据(想一下一个页是多少字节?

4K)。

这个过程称为Translation TableWalk,Walk这个词用得非常形象。

从TTB走到一级页表,又走到二级页表,又走到物理页面,一次寻址其实是三次访问物理内存。

注意这个“走”的过程完全是硬件做的,每次CPU寻址时MMU就自动完成以上四步,不需要编写指令指示MMU去做,前提是操作系统要维护页表项的正确性,每次分配内存时填写相应的页表项,每次释放内存时清除相应的页表项,在必要的时候分配或释放整个页表。

有了以上基本概念,我们来看CPU访问内存时的硬件操作顺序(摘自[ARM参考手册])。

图10.CPU访问内存时的硬件操作顺序

我们以CPU读内存为例解释一下图中的步骤,各步骤在图中有对应的标号。

1CPU核(图中的“ARM”框)发出VA请求读数据,TLB(TranslationLookaside Buffer)接收到该地址。

TLB是MMU中的一块高速缓存(也是一种Cache),它缓存最近查找过的VA对应的页表项,如果TLB里缓存了当前VA的页表项就不必做TranslationTable Walk了,否则去物理内存中读出页表项保存在TLB中,TLB缓存可以减少访问物理内存的次数。

2页表项中不仅保存着物理页面的基地址,还保存着权限位和是否允许Cache的标志。

MMU首先检查权限位,如果没有访问权限,就引发一个异常给CPU核。

然后检查是否允许Cache,如果允许Cache就启用Cache和CPU核互操作,图中的“C,Bbits”可以理解为直写和回写线,后面再详细解释这两个位的作用。

3如果不允许Cache,则直接发出PA从物理内存中读取数据到CPU核。

4 如果允许Cache,则以VA为索引到Cache中查找是否缓存了要读取的数据,如果Cache中已经缓存了该数据(称为CacheHit)则直接返回给CPU核,如果Cache中没有缓存该数据(称为Cache Miss),则发出PA从物理内存中读取数据并缓存到Cache中,同时返回给CPU核。

然而Cache并不是只取CPU核所要的数据,而是把相邻的数据都取上来缓存,这称为一个Cache Line。

ARM920T的CacheLine是32字节,例如CPU核要读取地址0x134-0x137的4字节数据,Cache会把地址0x120-0x13f(对齐到32字节地址边界)的32字节都取上来缓存。

MMU

我们已经简单了解了一下查页表的过程,实际上ARM920T支持多种尺寸规格的页表,图 9 “TranslationTable Walk”所示的只是其中一种情况。

下图示意了所有可能的情况(本节的图表均摘自[S3C2410用户手册])。

图 11.查页表的过程

回顾一下查表的过程,首先从CP15的TTB寄存器找到一级页表的基地址,再把VA[31:

20](共4096项)作为索引从表中找出一项,这个表项称为一级页描述符(Level1 Descriptor),一个这样的表项占4个字节,可以是以下四种格式之一:

图12. 一级页描述符

如果描述符的最低两位是00,属于Fault格式,表示该范围的VA没有映射到PA。

如果描述符的最低两位是10,属于Section格式,这种格式没有二级页表而是直接映射到物理页面,一个Section是1M的大页面,描述符中[31:

20]位就是这个页面的基地址,基地址的[19:

0]低位全为0,对齐到1M地址边界,描述符中的Domain和AP位控制访问权限,C、B两位控制缓存,后面再详细解释每个位的含义。

如果描述符的最低两位是01或11,则分别对应两种不同规格的二级页表(VA[19:

12则为256项])。

根据地址对齐的规律想一下,这两种页表分别是多大?

从一级描述符中取出二级页表的基地址,再把VA的一部分作为索引去查二级描述符(Level2Descriptor)(如果是CoarsePage Table则VA[19:

12]是索引,如果是Fine PageTable则VA[19:

10]是索引),二级描述符可以是以下四种格式之一:

图13.二级页描述符

描述符最低两位是00属于Fault格式,其它三种情况分别对应三种不同规格的物理页面。

Large Page和SmallPage有四组AP权限位,每组两个bit,这样可以为每1/4个物理页面分别设置不同的权限,也就是说,LargePage可以为每16K设置不同的权限,SmallPage可以为每1K设置不同的权限。

ARM920T提供了多种页表和页面规格,但操作系统只采用其中一种,Linux采用的就是图9 “Translation Table Walk”所示的规格,一级描述符是CoarsePageTable格式,二级描述符是SmallPage格式,每个物理页面4K。

我们以此为例,结合前面的的解释和页描述符的格式,再看一下TranslationTableWalk的详细过程:

图14.TranslationTableWalk的详细过程

从上到下依次解释如下:

1VA被划分为三段用于地址映射过程,各段的长度取决于页描述符的格式。

2TTB寄存器中只有[31:

14]位有效,低14位全为0,因此一级页表的基地址对齐到16K地址边界,而一级页表的大小也是16K。

3一级页表的基地址加上VA[31:

20]左移两位组装成一个物理地址。

想一想为什么VA[31:

20]要左移两位占据[13:

2]的位置,而空出[1:

0]两位呢?

类型?

4 用这个组装的物理地址从物理内存中读取一级页描述符,这是一个Coarse PageTable格式的描述符。

5通过Domain权限检查后,CoarsePageTable的基地址再加上VA[19:

12]左移两位组装成一个物理地址。

6用这个组装的物理地址从物理内存中读取二级页描述符,这是一个SmallPage格式的描述符。

7通过AP权限检查后,SmallPage的基地址再加上VA[11:

0]就是最终的物理地址。

想一想为什么这次不左移两位了呢?

下面解释一下Domain和AP位。

CP15的Domain访问控制寄存器(见表1“CP15协处理器的寄存器列表”寄存器3)表示了16个域(Domain),每两位表示一个Domain的访问权限,以下是该寄存器的格式:

图15.Domain Access ControlRegister

每个Domain的两个位可以取值为00、01、10或11,如果取值为00或10则表示该Domain不可访问,如果取值为01则表示访问该Domain需要进一步检查AP位,如果取值为11则表示可以直接访问该Domain而无需检查AP位。

回想一下,一级页描述符中的Domain字段由4个位组成,可以有16个不同的取值,就表示该描述符所描述的二级页表或Section属于这16个Domain中的哪一个。

快速上下文切换、Domain和多种规格的页表是ARM特有的机制,是针对嵌入式系统软件的特点而设计的,其它处理器不一定有类似的机制,例如也许没有Domain和快速上下文切换的概念,也许只有一种规格的页表。

为了能够在多种不同的平台上移植,Linux内核代码不会利用ARM特有的这些机制。

除了这些特例之外,我们在这里介绍的其它机制都具有普遍性,读者应重点把握具有普遍意义的基本原理和基本概念。

CP15的控制寄存器(见表 1“CP15协处理器的寄存器列表”寄存器1)中的S和R位与页描述符的AP位合在一起决定访问权限,如下所示:

图16.AP权限检查

可见,同样的AP、S、R位对用户模式和特权模式来说具有不同的意义,特权模式的权限都不低于用户模式的权限。

最后将各种由内存访问产生的异常总结如下:

AlignmentFault——以Word为单位的数据访问指令地址未对齐到4字节边界,或者以Half Word为单位的数据访问指令地址未对齐到2字节边界。

Translation Fault——页描述符的[1:

0]为00,属于Fault格式,无效表项。

Domain Fault——一级页描述符或Section所属Domain的权限位为00或10。

PermissionFault——根据AP位和CP15寄存器1的S、R位检查访问权限,若所属Domain的权限位为11则跳过这一步检查。

ExternalAbort——总线异常,例如此物理地址上没有挂RAM芯片,或者其它硬件故障。

Cache

ARM920T有16K的数据Cache和16K的指令Cache,这两个Cache是基本相同的,数据Cache多了一些写回内存的机制,后面我们以数据Cache为例来介绍Cache的基本原理。

我们已经知道,Cache中的存储单位是CacheLine,ARM920T的一个CacheLine是32字节,因此16K的Cache由512条CacheLine组成。

要了解Cache的基本原理,我们从如何设计Cache这个问题入手。

设计Cache的一种最朴素的想法是,把VA分成以32字节为单位,从任何一个对齐到32字节地址边界的VA开始连续的32个字节(比如0x00-0x1f,0x20-0x3f,0x40-0x5f等等)都可以缓存到512条CacheLine中的任何一条。

那么一条CacheLine中的32个字节怎么知道是来自哪个VA的呢?

这就需要把VA也保存在Cache中,由于这32字节的起始地址是对齐到32字节地址边界的,末5位全为0,因此只需要保存VA[31:

5]即可,这称为VA Tag[4],Tag是VA的一部分,是CacheLine中数据的标识,表明这32字节数据来自哪个VA。

这样设计的Cache称为全相联Cache(FullyAssociativeCache),图示如下:

图17. 全相联Cache

给定一个VA,如何在Cache中查找对应的数据呢?

首先到Cache中比较查找哪一行的Tag等于VA[31:

5],找到对应的CacheLine后,再根据VA[4:

0]决定要访问的是该CacheLine缓存的32个字节中的哪一个字节。

由于有512条CacheLine,如果这个VA没有缓存在Cache中则需要比较512次才知道,这是最坏的情况,也是最常见的情况,下面我们要改进Cache的设计来解决这个问题。

全相联Cache的特点是任何VA都可以缓存到任何一条Cache Line,给定一个VA做查找时,由于它有可能缓存在512条CacheLine中的任何一条,就只好全部都找一遍了。

如果限定某一个VA只允许缓存在某一条CacheLine中,那么查找的过程就快多了:

检查一下应该缓存这个VA的那条CacheLine,看Tag一致不一致,如果一致就是CacheHit,如果不一致就是CacheMiss,可以直接访问物理内存而不必再找其它Cache Line了。

这种设计称为直接映射Cache(DirectMappedCache),如下图所示:

图18.直接映射Cache

地址0~31应该缓存在第1条Cache Line中,地址32~63应该缓存在第2条CacheLine中,依此类推,地址16352~16383应该缓存在第512条CacheLine中,下一个地址应该是16384(16K)了,我们又回到开头,地址16K