SDRAM verilog 串口例程.docx

《SDRAM verilog 串口例程.docx》由会员分享,可在线阅读,更多相关《SDRAM verilog 串口例程.docx(32页珍藏版)》请在冰豆网上搜索。

SDRAMverilog串口例程

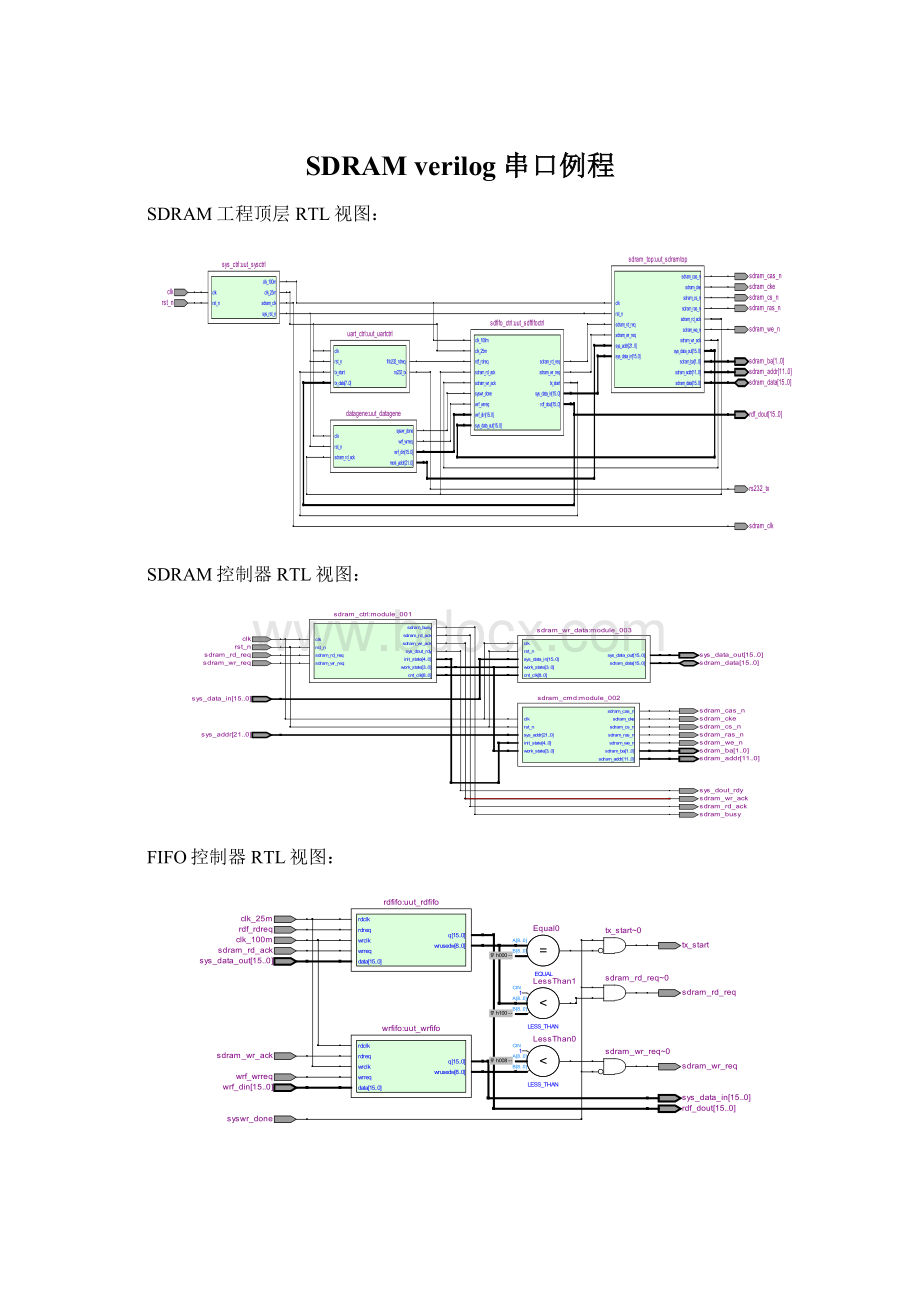

SDRAM工程顶层RTL视图:

SDRAM控制器RTL视图:

FIFO控制器RTL视图:

/*************************SDRAM顶层模块*********************************/

modulesdr_test(

clk,rst_n,

sdram_clk,sdram_cke,sdram_cs_n,sdram_ras_n,sdram_cas_n,sdram_we_n,

sdram_ba,sdram_addr,sdram_data,//sdram_udqm,sdram_ldqm

rs232_tx,

/*sdram_rd_req,sdram_wr_ack,sdram_rd_ack,

sys_data_out,sdram_busy,sys_data_in,sys_dout_rdy,

*/rdf_dout/*,rdf_rdreq*/

);

inputclk;//系统时钟,100MHz

inputrst_n;//复位信号,低电平有效

//FPGA与SDRAM硬件接口

outputsdram_clk;//SDRAM时钟信号

outputsdram_cke;//SDRAM时钟有效信号

outputsdram_cs_n;//SDRAM片选信号

outputsdram_ras_n;//SDRAM行地址选通脉冲

outputsdram_cas_n;//SDRAM列地址选通脉冲

outputsdram_we_n;//SDRAM写允许位

output[1:

0]sdram_ba;//SDRAM的L-Bank地址线

output[11:

0]sdram_addr;//SDRAM地址总线

//outputsdram_udqm;//SDRAM高字节屏蔽

//outputsdram_ldqm;//SDRAM低字节屏蔽

inout[15:

0]sdram_data;//SDRAM数据总线

outputrs232_tx;//RS232发送数据信号

////////////////////////////////////////////////

//SDRAM的封装接口测试引出

/*outputsdram_rd_req;//系统读SDRAM请求信号

outputsdram_wr_ack;//系统写SDRAM响应信号

outputsdram_rd_ack;//系统读SDRAM响应信号

output[15:

0]sys_data_in;//写SDRAM时数据暂存器,4个突发读写字数据,默认为00地址bit15-0;01地址bit31-16;10地址bit47-32;11地址bit63-48

output[15:

0]sys_data_out;//读SDRAM时数据暂存器,(格式同上)

outputsdram_busy;//SDRAM忙标志,高表示SDRAM处于工作中

outputsys_dout_rdy;//SDRAM数据输出完成标志

*/

output[15:

0]rdf_dout;//sdram数据读出缓存FIFO输出数据总线

//outputrdf_rdreq;//sdram数据读出缓存FIFO数据输出请求,高有效

////////////////////////////////////////////////

//SDRAM的封装接口

wiresdram_wr_req;//系统写SDRAM请求信号

wiresdram_rd_req;//系统读SDRAM请求信号

wiresdram_wr_ack;//系统写SDRAM响应信号,作为wrFIFO的输出有效信号

wiresdram_rd_ack;//系统读SDRAM响应信号,作为rdFIFO的输写有效信号

wire[21:

0]sys_addr;//读写SDRAM时地址暂存器,(bit21-20)L-Bank地址:

(bit19-8)为行地址,(bit7-0)为列地址

wire[15:

0]sys_data_in;//写SDRAM时数据暂存器

wire[15:

0]sys_data_out;//sdram数据读出缓存FIFO输入数据总线

wiresdram_busy;//SDRAM忙标志,高表示SDRAM处于工作中

wiresys_dout_rdy;//SDRAM数据输出完成标志

//wrFIFO输入控制接口

wire[15:

0]wrf_din;//sdram数据写入缓存FIFO输入数据总线

wirewrf_wrreq;//sdram数据写入缓存FIFO数据输入请求,高有效

//rdFIFO输出控制接口

wire[15:

0]rdf_dout;//sdram数据读出缓存FIFO输出数据总线

wirerdf_rdreq;//sdram数据读出缓存FIFO数据输出请求,高有效

//系统控制相关信号接口

wireclk_25m;//PLL输出25MHz时钟

wireclk_100m;//PLL输出100MHz时钟

wiresys_rst_n;//系统复位信号,低有效

//------------------------------------------------

//例化系统复位信号和PLL控制模块

sys_ctrluut_sysctrl(

.clk(clk),

.rst_n(rst_n),

.sys_rst_n(sys_rst_n),

.clk_25m(clk_25m),

.clk_100m(clk_100m),

.sdram_clk(sdram_clk)

);

//------------------------------------------------

//例化SDRAM封装控制模块

sdram_topuut_sdramtop(//SDRAM

.clk(clk_100m),

.rst_n(sys_rst_n),

.sdram_wr_req(sdram_wr_req),

.sdram_rd_req(sdram_rd_req),

.sdram_wr_ack(sdram_wr_ack),

.sdram_rd_ack(sdram_rd_ack),

.sys_addr(sys_addr),

.sys_data_in(sys_data_in),

.sys_data_out(sys_data_out),

.sys_dout_rdy(sys_dout_rdy),

//.sdram_clk(sdram_clk),

.sdram_busy(sdram_busy),

.sdram_cke(sdram_cke),

.sdram_cs_n(sdram_cs_n),

.sdram_ras_n(sdram_ras_n),

.sdram_cas_n(sdram_cas_n),

.sdram_we_n(sdram_we_n),

.sdram_ba(sdram_ba),

.sdram_addr(sdram_addr),

.sdram_data(sdram_data)

//.sdram_udqm(sdram_udqm),

//.sdram_ldqm(sdram_ldqm)

);

//------------------------------------------------

//读写SDRAM数据缓存FIFO模块例化

sdfifo_ctrluut_sdffifoctrl(

.clk_25m(clk_25m),

.clk_100m(clk_100m),

.wrf_din(wrf_din),

.wrf_wrreq(wrf_wrreq),

.sdram_wr_ack(sdram_wr_ack),

//.sys_addr(sys_addr),

.sys_data_in(sys_data_in),

.sdram_wr_req(sdram_wr_req),

.sys_data_out(sys_data_out),

.rdf_rdreq(rdf_rdreq),

.sdram_rd_ack(sdram_rd_ack),

.rdf_dout(rdf_dout),

.sdram_rd_req(sdram_rd_req),

.syswr_done(syswr_done),

.tx_start(tx_start)

);

//------------------------------------------------

//例化模拟写入数据到sdram模块

wiresyswr_done;//所有数据写入sdram完成标志位

datageneuut_datagene(

.clk(clk_25m),

.rst_n(sys_rst_n),

.wrf_din(wrf_din),

.wrf_wrreq(wrf_wrreq),

.moni_addr(sys_addr),

.syswr_done(syswr_done),

.sdram_rd_ack(sdram_rd_ack)

);

//------------------------------------------------

//例化串口数据发送控制模块

wiretx_start;//串口发送数据启动标志位,高有效

uart_ctrluut_uartctrl(

.clk(clk_25m),

.rst_n(sys_rst_n),

.tx_data(rdf_dout[7:

0]),

.tx_start(tx_start),///////////

.fifo232_rdreq(rdf_rdreq),

.rs232_tx(rs232_tx)

);

endmodule

/***************系统复位信号和PLL控制模块******************************/

moduleuart_ctrl(

clk,rst_n,

tx_data,tx_start,

fifo232_rdreq,

rs232_tx

);

inputclk;//25MHz主时钟

inputrst_n;//低电平复位信号

input[7:

0]tx_data;//待发送数据

inputtx_start;//串口发送数据启动标志位,高有效

outputfifo232_rdreq;//FIFO读请求信号,高有效

outputrs232_tx;//RS232发送数据信号

//----------------------------------------------------------------

//串口发送底层模块和串口波特率选择模块接口

wireclk_bps;//发送数据标志位,高有效

wirebps_start;//波特率时钟计数器启动信号,高有效

//----------------------------------------------------------------

//例化串口数据发送底层模块

uart_txuut_tx(

.clk(clk),

.rst_n(rst_n),

.tx_data(tx_data),

.tx_start(tx_start),

.clk_bps(clk_bps),

.rs232_tx(rs232_tx),

.bps_start(bps_start),

.fifo232_rdreq(fifo232_rdreq)

);

//例化串口数据发送波特率控制模块

uart_speed_selectuut_ss(

.clk(clk),

.rst_n(rst_n),

.bps_start(bps_start),

.clk_bps(clk_bps)

);

endmodule

/*****************模拟写入数据到SDRAM的datagene模块*******************/

moduledatagene(

clk,rst_n,

wrf_din,wrf_wrreq,

moni_addr,syswr_done,

sdram_rd_ack

);

inputclk;//FPAG输入时钟信号25MHz

inputrst_n;//FPGA输入复位信号

//wrFIFO输入控制接口

output[15:

0]wrf_din;//sdram数据写入缓存FIFO输入数据总线

outputwrf_wrreq;//sdram数据写入缓存FIFO数据输入请求,高有效

output[21:

0]moni_addr;//sdram读写地址产生

outputsyswr_done;//所有数据写入sdram完成标志位

inputsdram_rd_ack;//系统读SDRAM响应信号,作为rdFIFO的输写有效信号,这里捕获它的下降沿作为读地址自增加标志位

regsdr_rdackr1,sdr_rdackr2;

//------------------------------------------

//捕获sdram_rd_ack下降沿标志位

always@(posedgeclkornegedgerst_n)

if(!

rst_n)begin

sdr_rdackr1<=1'b0;

sdr_rdackr2<=1'b0;

end

elsebegin

sdr_rdackr1<=sdram_rd_ack;

sdr_rdackr2<=sdr_rdackr1;

end

wireneg_rdack=~sdr_rdackr1&sdr_rdackr2;

//------------------------------------------

//上电500us延时等待sdram就绪

reg[13:

0]delay;//500us延时计数器

always@(posedgeclkornegedgerst_n)

if(!

rst_n)delay<=14'd0;

elseif(delay<14'd12500)delay<=delay+1'b1;

wiredelay_done=(delay==14'd12500);//1ms延时结束

//每640ns写入8个16bit数据到sdram,

//上电后所有地址写入完毕时间需要不到360ms时间

reg[5:

0]cntwr;//写sdram定时计数器

always@(posedgeclkornegedgerst_n)

if(!

rst_n)cntwr<=6'd0;

elseif(delay_done)cntwr<=cntwr+1'b1;

//------------------------------------------

//读写sdram地址产生

reg[18:

0]addr;//sdram地址寄存器

always@(posedgeclkornegedgerst_n)

if(!

rst_n)addr<=19'd0;

elseif(!

wr_done&&cntwr==6'h3f)addr<=addr+1'b1;//写地址产生

elseif(wr_done&&neg_rdack)addr<=addr+1'b1;//读地址产生////////////test

assignmoni_addr={addr,3'b000};

regwr_done;//所有数据写入sdram完成标志位

always@(posedgeclkornegedgerst_n)

if(!

rst_n)wr_done<=1'b0;

elseif(addr==19'h7ffff)wr_done<=1'b1;

assignsyswr_done=wr_done;

//------------------------------------------

//写sdram请求信号产生,即wrfifo的写入有效信号

regwrf_wrreqr;//wrfifo的写入有效信号

reg[15:

0]wrf_dinr;//wrfifo的写入数据

always@(posedgeclkornegedgerst_n)

if(!

rst_n)wrf_wrreqr<=1'b0;

elseif(!

wr_done)begin//上电0.5ms延时完成

if(cntwr==6'h05)wrf_wrreqr<=1'b1;//写请求信号产生

elseif(cntwr==6'h0d)wrf_wrreqr<=1'b0;//请求信号撤销

end

always@(posedgeclkornegedgerst_n)

if(!

rst_n)wrf_dinr<=16'd0;

elseif(!

wr_done&&((cntwr>6'h05)&&(cntwr<=6'h0d)))begin//上电0.5ms延时完成

wrf_dinr<=wrf_dinr+1'b1;//写入数据递增

end

assignwrf_wrreq=wrf_wrreqr;

assignwrf_din=wrf_dinr;

endmodule

/********************sdfifo_ctrl控制模块*********************/

//fifo由quratusIPCORE生成,只写控制fifo模块即可

modulesdfifo_ctrl(

clk_25m,clk_100m,

wrf_din,wrf_wrreq,

sdram_wr_ack,/*sys_addr,*/sys_data_in,sdram_wr_req,

sys_data_out,rdf_rdreq,sdram_rd_ack,rdf_dout,sdram_rd_req,

syswr_done,tx_start

);

inputclk_25m;//PLL输出25MHz时钟

inputclk_100m;//PLL输出100MHz时钟

//wrfifo

input[15:

0]wrf_din;//sdram数据写入缓存FIFO输入数据总线

inputwrf_wrreq;//sdram数据写入缓存FIFO数据输入请求,高有效

inputsdram_wr_ack;//系统写SDRAM响应信号,作为wrFIFO的输出有效信号

//output[21:

0]sys_addr;//读写SDRAM时地址暂存器,(bit21-20)L-Bank地址:

(bit19-8)为行地址,(bit7-0)为列地址

output[15:

0]sys_data_in;//sdram数据写入缓存FIFO输出数据总线,即写SDRAM时数据暂存器

outputsdram_wr_req;//系统写SDRAM请求信号

//rdfifo

input[15:

0]sys_data_out;//sdram数据读出缓存FIFO输入数据总线

inputrdf_rdreq;//sdram数据读出缓存FIFO数据输出请求,高有效

inputsdram_rd_ack;//系统读SDRAM响应信号,作为rdFIFO的输写有效信号

output[15:

0]rdf_dout;//sdram数据读出缓存FIFO输出数据总线

outputsdram_rd_req;//系统读SDRAM请求信号

inputsyswr_done;//所有数据写入sdram完成标志位

outputtx_start;//串口发送数据启动标志位,高有效

//------------------------------------------------

wire[8:

0]wrf_use;//sdram数据写入缓存FIFO已用存储空间数量

wire[8:

0]rdf_use;//sdram数据读出缓存FIFO已用存储空间数量

//assignsys_addr=22'h1a9e21;//测试用

assignsdram_wr_req=((wrf_use>=9'd8)&~syswr_done);//FIFO(8个16bit数据)即发出写SDRAM请求信号

assignsdram_rd_req=((rdf_use<=9'd256)&syswr_done);//sdram写入完成且FIFO半空(256个16bit数据)即发出读SDRAM请求信号

assigntx_start=((rdf_use!

=9'd0)&syswr_done);//启动串口发送数据

//------------------------------------------------

//例化SDRAM写入数据缓存FIFO模块

wrfifouut_wrfifo(

.data(wrf_din),

.rdclk(clk_100m),

.rdreq(sdram_wr_ack),

.wrclk(clk_25m),

.wrreq(wrf_wrreq),

.q(sys_data_in),

.wrusedw(w