西南交大EDA期末报告.docx

《西南交大EDA期末报告.docx》由会员分享,可在线阅读,更多相关《西南交大EDA期末报告.docx(48页珍藏版)》请在冰豆网上搜索。

西南交大EDA期末报告

EDA实验报告

班级:

微电子2班

指导老师:

XXXX

学号:

XXXXXXXXXX

姓名:

XXX

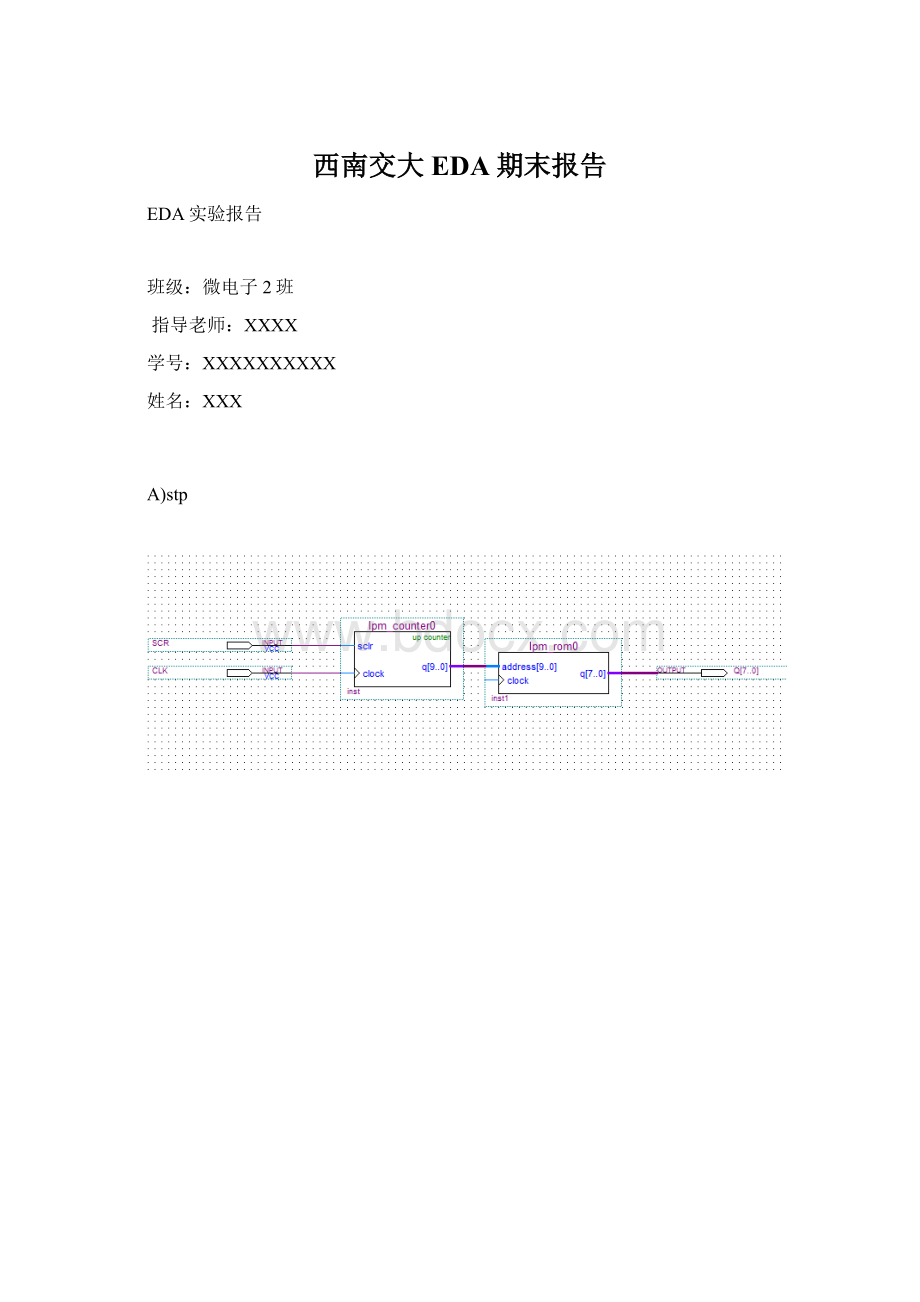

A)stp

B)5959

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

useieee.std_logic_unsigned.all;

USEwork.li_20112913_cipher_5959_99_pkg.ALL;

ENTITYli_20112913_cipher_updown_5959_textIS

PORT

(clk:

INSTD_LOGIC;

res_in:

INSTD_LOGIC;

ena_in:

INSTD_LOGIC;

cout_final:

OUTSTD_LOGIC;

hex0:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

hex1:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

hex2:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

hex3:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

hex4:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

hex5:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

cipher_in:

INSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDli_20112913_cipher_updown_5959_text;

ARCHITECTUREbdf_typeOFliu_20112910_cipher_updown_5959_textIS

SIGNALclk_100hz_clk_cnt10_0:

STD_LOGIC;

SIGNALclk_cnt10_1:

STD_LOGIC;

SIGNALclk_cnt10_2:

STD_LOGIC;

SIGNALclk_cnt10_4:

STD_LOGIC;

SIGNALclk_cnt6_3:

STD_LOGIC;

SIGNALclk_cnt6_5:

STD_LOGIC;

SIGNALseg7_m0:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNALseg7_m1:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNALseg7_m2:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNALseg7_m3:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNALseg7_m4:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNALseg7_m5:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

b2v_inst:

hsu_div_to_100

GENERICMAP(N=>500000

)

PORTMAP(clk=>clk,

outclk=>clk_100hz_clk_cnt10_0);

b2v_inst1:

hsu_count10_updown

PORTMAP(CLK=>clk_100hz_clk_cnt10_0,

RST=>res_in,

ENA=>ena_in,

COUT=>clk_cnt10_1,

OUTY=>seg7_m0,

cipher=>cipher_in);

b2v_inst10:

hsu_2011am_seg7

PORTMAP(data_in=>seg7_m3,

q_out=>hex3);

b2v_inst11:

hsu_2011am_seg7

PORTMAP(data_in=>seg7_m4,

q_out=>hex4);

b2v_inst12:

hsu_2011am_seg7

PORTMAP(data_in=>seg7_m5,

q_out=>hex5);

b2v_inst2:

hsu_count10_updown

PORTMAP(CLK=>clk_cnt10_1,

RST=>res_in,

ENA=>ena_in,

COUT=>clk_cnt10_2,

OUTY=>seg7_m1,

cipher=>cipher_in);

b2v_inst3:

hsu_count10_updown

PORTMAP(CLK=>clk_cnt10_2,

RST=>res_in,

ENA=>ena_in,

COUT=>clk_cnt6_3,

OUTY=>seg7_m2,

cipher=>cipher_in);

b2v_inst4:

hsu_count6_updown

PORTMAP(CLK=>clk_cnt6_3,

RST=>res_in,

ENA=>ena_in,

COUT=>clk_cnt10_4,

OUTY=>seg7_m3,

cipher=>cipher_in);

b2v_inst5:

hsu_count10_updown

PORTMAP(CLK=>clk_cnt10_4,

RST=>res_in,

ENA=>ena_in,

COUT=>clk_cnt6_5,

OUTY=>seg7_m4,

cipher=>cipher_in);

b2v_inst6:

hsu_count6_updown

PORTMAP(CLK=>clk_cnt6_5,

RST=>res_in,

ENA=>ena_in,

COUT=>cout_final,

OUTY=>seg7_m5,

cipher=>cipher_in);

b2v_inst7:

hsu_2011am_seg7

PORTMAP(data_in=>seg7_m0,

q_out=>hex0);

b2v_inst8:

hsu_2011am_seg7

PORTMAP(data_in=>seg7_m1,

q_out=>hex1);

b2v_inst9:

hsu_2011am_seg7

PORTMAP(data_in=>seg7_m2,

q_out=>hex2);

ENDbdf_type;

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

entityhsu_div_to_100is

GENERIC(N:

integer:

=500000);

port(clk:

instd_logic;

outclk:

outstd_logic);

endhsu_div_to_100;

architecturertlofhsu_div_to_100is

signalcount:

integer;

begin

process(clk)

begin

if(clk'eventandclk='1')then

if(count=N-1)then

count<=0;

else

count<=count+1;

ifcount<(integer(N/2))then

outclk<='0';

else

outclk<='1';

endif;

endif;

endif;

endprocess;

endrtl;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYhsu_count10_updownIS

PORT(CLK,RST,ENA:

INSTD_LOGIC;

OUTY:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

COUT:

OUTSTD_LOGIC;

cipher:

INSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDhsu_count10_updown;

ARCHITECTUREbehave_cnt10OFhsu_count10_updownIS

SIGNALCQI:

STD_LOGIC_VECTOR(3DOWNTO0):

="0000";

SIGNALflag1_2:

STD_LOGIC_VECTOR(1DOWNTO0);

SIGNALcipher_temp:

STD_LOGIC_VECTOR(7DOWNTO0);

BEGIN

cipher_temp<=cipher;

P_COUNT10_VT:

PROCESS(CLK,RST,ENA,flag1_2)

BEGIN

IFRST='1'THENCQI<="0000";

ELSIFCLK'EVENTANDCLK='1'THEN

IFENA='1'THEN

if(flag1_2="00")then

IFCQI<9THEN

CQI<=CQI+1;

ELSE

CQI<="0000";

ENDIF;

elsif(flag1_2="01")then

IFCQI>0THEN

CQI<=CQI-1;

ELSE

CQI<="1001";

ENDIF;

endif;

ENDIF;

ENDIF;

OUTY<=CQI;

IF(flag1_2="00")THEN

COUT<=NOT(CQI(3)ANDCQI(0));

ELSIF(flag1_2="01")THEN

COUT<=CQI(3)ORCQI

(2)ORCQI

(1)ORCQI(0);

ENDIF;

ENDPROCESSP_COUNT10_VT;

p1:

Process(clk,cipher_temp)

BEGIN

IF(clk'EVENTANDclk='1')THEN

IF(cipher_temp="00001111")THEN

flag1_2<="00";

ELSIF(cipher_temp="11110000")THEN

flag1_2<="01";

ELSIF(cipher_temp="11001100")THEN

flag1_2<="10";

ENDIF;

ENDIF;

ENDPROCESSp1;

p2:

Process(clk,flag1_2,CQI)

BEGIN

IF(clk'EVENTANDclk='1')THEN

IF(flag1_2="10")THEN

CQI<=CQI;

ENDIF;

ENDIF;

ENDPROCESSp2;

ENDbehave_cnt10;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYhsu_count6_updownIS

PORT(CLK,RST,ENA:

INSTD_LOGIC;

OUTY:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

COUT:

OUTSTD_LOGIC;

cipher:

INSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDhsu_count6_updown;

ARCHITECTUREbehave_cnt6OFhsu_count6_updownIS

SIGNALCQI:

STD_LOGIC_VECTOR(3DOWNTO0):

="0000";

SIGNALflag1_2:

STD_LOGIC_VECTOR(1DOWNTO0);

SIGNALcipher_temp:

STD_LOGIC_VECTOR(7DOWNTO0);

BEGIN

cipher_temp<=cipher;

P_COUNT10_VT:

PROCESS(CLK,RST,ENA)

BEGIN

IFRST='1'THENCQI<="0000";

ELSIFCLK'EVENTANDCLK='1'THEN

IFENA='1'THEN

if(flag1_2="00")then

IFCQI<5THEN

CQI<=CQI+1;

ELSE

CQI<="0000";

ENDIF;

elsif(flag1_2="01")then

IFCQI>0THEN

CQI<=CQI-1;

ELSE

CQI<="0101";

ENDIF;

endif;

ENDIF;

ENDIF;

OUTY<=CQI;

IF(flag1_2="00")THEN

COUT<=NOT(CQI

(2)ANDCQI(0));

ELSIF(flag1_2="01")THEN

COUT<=CQI(3)ORCQI

(2)ORCQI

(1)ORCQI(0);

ENDIF;

ENDPROCESSP_COUNT10_VT;

p1:

Process(clk,cipher_temp)

BEGIN

IF(clk'EVENTANDclk='1')THEN

IF(cipher_temp="00001111")THEN

flag1_2<="00";

ELSIF(cipher_temp="11110000")THEN

flag1_2<="01";

ELSIF(cipher_temp="11001100")THEN

flag1_2<="10";

ENDIF;

ENDIF;

ENDPROCESSp1;

p2:

Process(clk,flag1_2,CQI)

BEGIN

IF(clk'EVENTANDclk='1')THEN

IF(flag1_2="10")THEN

CQI<=CQI;

ENDIF;

ENDIF;

ENDPROCESSp2;

ENDbehave_cnt6;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYhsu_2011am_seg7IS

PORT(data_in:

INSTD_LOGIC_VECTOR(3DOWNTO0);

q_out:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDhsu_2011am_seg7;

ARCHITECTURErt1OFhsu_2011am_seg7IS

SIGNALtemp_data_in:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

display_process:

PROCESS(data_in)

BEGIN

temp_data_in<=data_in;

CASEtemp_data_inIS

WHEN"0000"=>q_out<="1000000";

WHEN"0001"=>q_out<="1111001";

WHEN"0010"=>q_out<="0100100";

WHEN"0011"=>q_out<="0110000";

WHEN"0100"=>q_out<="0011001";

WHEN"0101"=>q_out<="0010010";

WHEN"0110"=>q_out<="0000010";

WHEN"0111"=>q_out<="1111000";

WHEN"1000"=>q_out<="0000000";

WHEN"1001"=>q_out<="0010000";

WHEN"1010"=>q_out<="0001000";

WHEN"1011"=>q_out<="0000011";

WHEN"1100"=>q_out<="1000110";

WHEN"1101"=>q_out<="0100001";

WHEN"1110"=>q_out<="0000110";

WHEN"1111"=>q_out<="0001110";

WHENOTHERS=>q_out<="1111111";

ENDCASE;

ENDPROCESSdisplay_process;

ENDrt1;

C)sopc1

E)Hello

LIBRARYieee;

USEieee.std_logic_1164.all;

usework.li_20112913_hello_pkg.all;

ENTITYli_20112913_hello_topIS

PORT

(

clr:

INSTD_LOGIC;

clk:

INSTD_LOGIC;

hex0:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

hex1:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

hex2:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

hex3:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

hex4:

OUTSTD_LOGIC_VECTOR(6DOWNTO0)

);

ENDli_20112913_hello_top;

ARCHITECTUREbdf_typeOFli_20112913_hello_topIS

SIGNALclk_1s:

STD_LOGIC;

SIGNALm0_to_hex0:

STD_LOGIC_VECTOR(2DOWNTO0);

SIGNALm1_to_hex1:

STD_LOGIC_VECTOR(2DOWNTO0);

SIGNALm2_to_hex2:

STD_LOGIC_VECTOR(2DOWNTO0);

SIGNALm3_to_hex3:

STD_LOGIC_VECTOR(2DOWNTO0);

SIGNALm4_to_hex4:

STD_LOGIC_VECTOR(2DOWNTO0);

BEGIN

b2v_inst:

hsu_freqency_to_one_s

GENERICMAP(N=>50000000

)

PORTMAP(clk=>clk,

outclk=>clk_1s);

b2v_inst1:

hsu_mux_3bit_5to1

PORTMAP(clk_5to1=>clk_1s,

clr=>clr,

m0=>m0_to_hex0,

m1=>m1_to_hex1,

m2=>m2_to_hex2,

m3=>m3_to_hex3,

m4=>m4_to_hex4);

b2v_inst2:

hsu_seg7n_hello

PORTMAP(data_in=>m4_to_hex4,

data_hexn=>hex4);

b2v_inst3:

hsu_seg7n_hello

PORTMAP(data_in=>m3_to_hex3,

data_hexn=>hex3);

b2v_inst4:

hsu_seg7n_hello

PORTMAP(data_in=>m2_to_hex2,

data_hexn=>hex2);

b2v_inst5:

hsu_seg7n_hello

PORTMAP(data_in=>m1_to_hex1,

data_hexn=>hex1);

b2v_inst6:

hsu_seg7n_hello

PORTMAP(data_in=>m0_to_hex0,

data_hexn=>hex0);

ENDbdf_type;

libraryieee;

useieee.std_logic_1164.all;

entityhsu_seg7n_hellois

port(data_in:

instd_logic_vector(2downto0);

data_hexn:

outstd_logic_vector(6downto0));

endhsu_seg7n_hello;

architecturebehavior_seg7nofhsu_seg7n_hellois

begin

p2:

process(data_in)

begin

casedata_inis

when"000"=>data_hexn<="0001001";

when"001"=>data_hexn<="0000110";

when"010"=>data_hexn<="1000111";

when"011"=>data_hexn<="1000000";

whenothers=>data_hexn<="1111111";

endcase;

endprocessp2;

endbehavior_seg7n;

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityhsu_mux_3bit_5to1is

port(clk_5to1,clr:

instd_logic;

m4,m3,m2,m1,m0:

outstd_logic_vector(2downto0));

endhsu_mux_3bit_5to1;

architecturebehavior_mux_3bit_5to1ofhsu_mux_3bit_5to1is

signalu:

std_logic_vector(2downto0):

="000";

signalv:

std_logic_vector(2downto0):

="001";