基于FPGA串口控制器设计报告.docx

《基于FPGA串口控制器设计报告.docx》由会员分享,可在线阅读,更多相关《基于FPGA串口控制器设计报告.docx(12页珍藏版)》请在冰豆网上搜索。

基于FPGA串口控制器设计报告

基于FPGA的串口控制器设计

简介

使用硬件描述语言(HDL)设计和开发验证FPGA的成为当前的主流因素。

使用行为级描述不只增加了产品的设计效率,也在设计中有独特的验证方式。

目前最流行的HDL语言为Verilog和VHDL。

这篇文章将会举例说明用Verilog语言的设计和验证数字异步串行收发器UART。

UART介绍

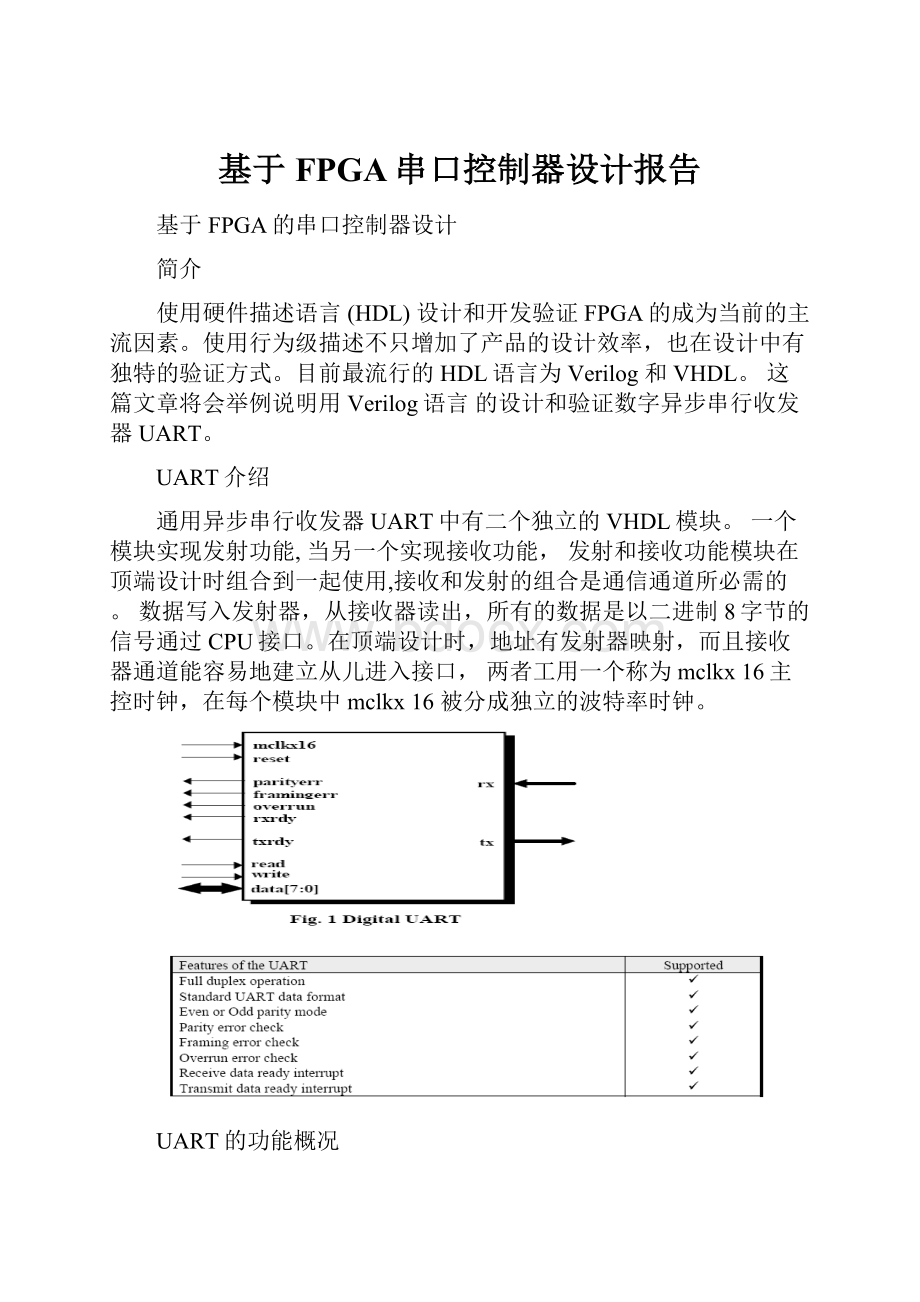

通用异步串行收发器UART中有二个独立的VHDL模块。

一个模块实现发射功能,当另一个实现接收功能,发射和接收功能模块在顶端设计时组合到一起使用,接收和发射的组合是通信通道所必需的。

数据写入发射器,从接收器读出,所有的数据是以二进制8字节的信号通过CPU接口。

在顶端设计时,地址有发射器映射,而且接收器通道能容易地建立从儿进入接口,两者工用一个称为mclkx16主控时钟,在每个模块中mclkx16被分成独立的波特率时钟。

UART的功能概况

UART的基本功能概况见下表.在左边显示传输保持记录,移位记录,传输控制时钟,全部集中在发射机的txmit端。

在右边的是显示接收移位寄存器,接收记录和控制逻辑时钟,所有都包含在接收模块的rxcver端,这两个模组都单独的投入与产出,大部分的控制线,只有双向数据总线,主时钟和复位线共享的模块。

顶层UART系统的I/O功能描述

UART的标准数据格式

图3显示了UART的串行数据格式,串行数据包含在帧8个数据字节,以及编码信息比特,在连续传输线路高通,在传输初始化时开始低一点.,接下来的低一点开始到8比特的数据信息,低位对于后边高位有重要的作用。

然后后边的8bits数据进行奇偶校验,反馈8位数据的结果。

UART时序图

下面显示怎么将从寄存器里出来的数据写给移位寄存器,并在上升沿速率时钟时,转向tx输出。

发送时间如下表,如何得到数据从rx传输到接收移位寄存器然后存储。

发送器

主控时钟称为mclkx16,分频成正确的等于mclkx16/16的txclk波特率。

数据以平行的形式锁存模块,而转向以串行格式的tx输出波特率时钟频率。

数据转到tx输出跟随串行数据格式显示在图6。

发送器行为描述

发送器等待新的数据来写入模块,新的数据在发送器初始化后发送。

数据以并行方式传送串行数据帧的tx输出.当没有传输序列的地方,tx输出是高通。

发送器实现

产生逻辑的Verilog始于模块端口的声明,这里定义的信号,是移植到从单元,没有方向指明这一点。

在下一个端口定义来自端口的方向,方向指定为输入,输出或(双向),见表1。

指明端口方向来声明内部信号,内部信号的Verilog称为wire和reg数据类型,WIRE被数字低音的分配,REG用在分配Verilog里的always时钟,座,常常使用逻辑顺序的分配,但不是一定的,进一步解释见Verilog参考书,数据类型的内部信号如表3。

我们现在已经通过了所有必要的声明,并已作好准备,看看实际执行,用硬件描述语言使我们描述的功能的发送器更加行为化,而不是把重点放在它门级。

在软件编程语言,职能和工作程序分成更具可读性和易处理,一个Verilog的功能及任务是作为相当于复线Verilog代码,如果某些输入信号或某些影响产出或变数.使用的职能和任务,通常发生在多行代码都是重复使用的设计,从而使得设计易于阅读和维护肯定,一个Verilog的功能,可以有多种输入,但始终只有一个输出,虽然Verilog任务可以兼得多投入,多产出,甚至在某些情况下,非取长补短,下面显示了Verilog任务,即拥有所有必要的顺序语句,用来描述发送器的转移模式。

我们可以看到在移位寄存器有2个标志位tag1和tag2,在描述空闲和置位模块时产生相同的作用,使用这些Verilog工作,现在我们可以产生一个容易阅读的行为模型的空穴传输过程。

如果txdoneandtxdatardy都是正确的,进入发送器负荷模式.接下来的负载模式下,进入发送模式转变.,在上升沿的速率时钟,内容tsr转移到tx输出.奇偶校验过程产生于tsr变化中,如下所示。

重要的一点,就是tsr为零发生在传输过程,在不同的数据传输时标志位tag和tsr赋零。

传输序列的模拟

在写上升沿时数据总线容量被锁存,在下一上升沿txclk,thr的容量载入tsr,低电平开始位进入tx,发送标志位显示,thr再次等待新的数据的写入。

在每个发送时钟上升沿,tsr的容量被送入tx,在数据传输过程中发生奇偶校验,周期循环时奇偶校验为高,tx产生奇偶检验结果。

接收模块

主控时钟mclkx16分频到合适的波也率时钟称为rxclk,它等于mclkx16/16.串行数据为收到的rx输入模块,要按照UART的数据格式显示为图3,收到的数据格式以并行形式读出,通过8位数据总线。

接收模块行为描述

在连续发送时,发送保持高,根据标准异步串行UART,接收器在等待闲置模式的rx输入要低,在rx下降沿接收进入保持模式,现在寻求一种有效的开始位等待新的数据帧的到来,当有效的开始位被检测到时,接收器回到闲置模式,在接收一个数据帧,各种校验和检查错误,当一个完整的数据帧收到接收端返回待机模式.,接收器基本运作如下所示。

接收频率为mclkx16,和第一上升沿的rxclk常常发生在中心点开始位,如下图显示,对于中心点的起始位及后边的数据字节,波特率时钟是同步。

接收器模块的实现

为了产生一个易读易操作的接收器模块,用两中Verilog功能来描述不同的接收方式,当接收在空闲状态时,其中一个Verilog称为空闲复位,而它需要所有必要的顺序语句来描述接收机复位条件。

当接收器不在复位状态,也不在空闲状态下,rx输入端的采样数据,传输到移位寄存器中,在进入的数据中产生奇偶校验位,另外一个Verilog称为数据移位,需要所有必要的顺序语句来描述上述行为。

利用两个Verilog实现上述功能,现在在复位状态,空闲状态或者数据传输状态,我们可以产生行为级描述的接收器,所有上述行为是和接收时钟同步的,它们的实现如下所示。

当低电平开始位到达rsr[0]时,一个完整的数据帧将会给接收到,在下一个接收时钟上升沿到来是又回到空闲状态,当返回空闲状态时,接收器显示数据接收准备,然后数据以并行方式读出,错误的标识更新,并返回空闲状态,在数据读出后清除,在读下降沿,rhr的容量锁存在数据总线,表8所示接收器各种错误检查。

接收序列的模拟

在连续传输时线路高通,在rx输入下降沿,,内部rxcnt开始计数,和mclkx16同步,如果rx输入在mclkx16的8个周期循环,内部空闲复位,接收时钟产生使能,和中心低开始位同步,在接受时钟上升沿,数据从RX传输到RSR,当低开始位到底rsr[0]时,在下一个接收时钟上升沿又被置空闲位,此时失效,在接收序列,刚好产生rxclk的11个周期,为采样一位低开始位,一位数据位,一位奇偶位,一位置高停止位。

在返回空闲状态,rsr被置入rhr,内部标志位更新,接收位产生,rhr容量给读出,在读下降沿,rhr应用到数据总线。

硬件描述语言仿真

我们现正研究如何HDL可用于行为级设计,实现了数字UART。

在HDL进行设计的实施更容易阅读,并希望能理解,它还规定,能够方便的描述依存度之间的各种程序,通常是发生在这样一个复杂事件驱动系统,例如UART,我们很快将看到这种依靠各种进程来描述的能力对于实现模拟是确实必须的。

Verilog语言中的模拟激励叫做测试工具,测试工具的Verilog模块,拥有各线路的HDL代码要生成仿真激励,而在同一时间端口影射,这些产生的信号将会模拟。

端口影射是完成了被异步通用步收发传输器的级层模块实例化顶端水平进入测试工具,如下所示。

这使得仿真激励适用于输入的设计,同时检测输出的设计,输入激励,可以有条件地反应与输出,图19显示说明如何测试工具端口影射到UART的顶层。

在测试工具的输出的传输模块又循环到接收器的输入模块,这使得发送器模块用来作为测试信号发生器接收器模块,数据可以并行的方式向发送器,同时回送到输入的接收机模块,收到的数据最终从接收器以并行格式读出,为了尽可能实现UART的自动化测试,独立书Verilog功能如下,发送写入功能需要一切必要的声明来产生一个并行的数据写序的发送器,数据写入发送器来完成写入接收功能,锁存内部测试工具供以后的分析。

接收读出功能需要一切必要的声明来产生一个并行的数据写序的接收器,数据读出接收器来完成读出功能,锁存内部测试工具供以后的分析。

数据比较功能需要一切必要的声明来同先前写入发送器,相应的最新接收数据和接收模块读出的数据比较,如果发生任何误差,数据比较标志一个从发送器写出的数据定义错误,相应的数据也从接收模块接收和读出,有任何误差发生时,笔记比较数据功能将立即停止模拟仿真。

综合

HDL作为设计方法比传统的FPGA设计输入方式如原理图方式有若干优势,它同时规定了极大的灵活性以及高性能的目标装置的综合流程,UART综合流程已针对两个灵活和高性能的可编程逻辑器件FPGA系列,如pASIC-1和pASIC。

UART设计和模拟的文件进入叫做使用HDL语言编辑器的SarosTechnologies的turbow软件,HDL设计合成了快速高效的正确综合工具,综合以后,设计布局使用spde可编程逻辑工具,在布局之后,UART使用有标注的Verilog布局时序模块,快速Verilog仿真为来自Simucad的SilosIII后布局仿真,所有使用过的工具中可用的

工具来自于快速逻辑。