电子系统设计实验报告.docx

《电子系统设计实验报告.docx》由会员分享,可在线阅读,更多相关《电子系统设计实验报告.docx(30页珍藏版)》请在冰豆网上搜索。

电子系统设计实验报告

基于单片机和FPGA的等精度频率计

一、设计任务

工作频率通信系统极为重要的参数,频率测量是通信系统基本的参数测试之一。

本设计的主要任务是使用单片机与EDA技术设计制作一个简易的等精度频率测试仪,可对输入周期信号的频率进行测量、显示。

被测信号的频率范围和测试的精度要求见相应的设计任务书。

二、设计框图

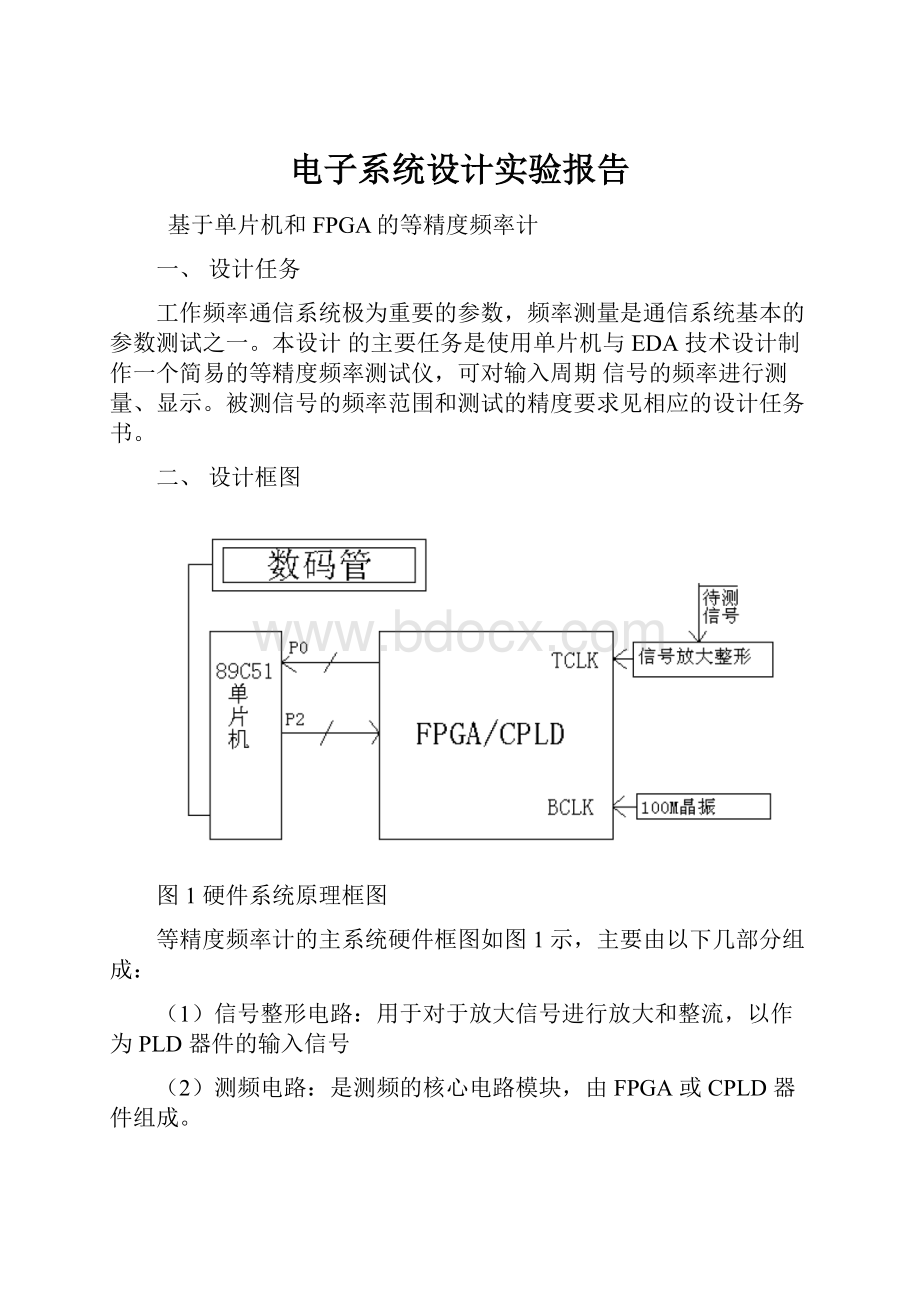

图1硬件系统原理框图

等精度频率计的主系统硬件框图如图1示,主要由以下几部分组成:

(1)信号整形电路:

用于对于放大信号进行放大和整流,以作为PLD器件的输入信号

(2)测频电路:

是测频的核心电路模块,由FPGA或CPLD器件组成。

(3)单片机电路模块:

用于控制FPGA的测频操作和读取测频数据,并做出相应处理。

(4)数码显示模块:

用8个数码管显示测试结果,考虑到提高单片机I/O口的利用率,降低编程复杂性,提高单片机的计算速度以及降低数码显示器对主系统的干扰,可以采用串行静态显示方式。

三、测频原理分析

3.1等精度频率测试的原理

频率是一个基本的物理量,其它的物理量可以转换为频率进行测量。

测试频率的基本方法包括直接测频和测周法。

其中直接测频法是产生一个标准宽度(例如1s)的时基信号,然后在这个信号时间范围内打开闸门对被测频率信号进行计数。

此方法的弱点之一是高精度的标准时基信号不容易获得;其二,这种方法对于高频信号的测量精度比较有保证,但是对于低频信号由于计数周期有限测试精度较低。

测周法是用被测信号作为闸门信号、对标准脉冲信号进行计数,显然这种方法适合测量低频信号的频率。

等精度测频法的核心思想是用两个计数器分别对标准和被测脉冲进行计数,计数的时间严格同步于被测脉冲。

这种方法的最大优点是测试的精度和被测信号的频率无关,因而可以做到等精度测量。

其测试原理如图2示。

预置闸门信号是测试命令,即测频的使能信号,该信号为高电平的期间进行测频。

但是当预置闸门信号为高电平时,测频并不是立即开始,而是要等到被测信号的上升沿到来以后,实际闸门信号跳为高电平,测频才真正开始。

同理,当预置闸门信号跳低以后,测频并没有马上结束,而是要等到被测信号的上升沿以后,实际闸门信号才跳低,测频结束。

由此可见,实际闸门信号完全同步于被测信号,其脉冲宽度必然是被测信号周期的整数倍,期间对被测信号和标准脉冲进行计数,再通过简单的计算就可以求得被测信号的频率。

图2等精度测频各信号时序图

3.2测频误差分析

周期法测频时,是在被测信号的一个周期xT内,对被测信号sT脉冲进行计数,计数结果为Ns,Tx=Ts⋅Ns误差1sΔN≤。

容易求得信号频率为:

对上式两边求微分,得:

固定sT,则误差与xT成反比,当被测信号的频率接近标准频率信号时,测量误差会增大。

直接测频时,是在一个标准的时间GT内对被测信号xT进行计数。

设计数值为xN,则GxxT=T⋅N,误差1xΔN≤。

则被测频率可以表示为:

对上式两边微分,得到相对误差为:

由此可见,如果固定GT,则误差与xf成反比,当被测信号的周期较长时,测量误差会增大。

设在一次实际的闸门时间τ以内记得被测信号和标准信号的计数值分别为Nx和Ns,标准信号的频率为fs,则被测信号的频率为:

若被测信号的实际频率为fxe,则测量误差为:

由于实际闸门完全同步于被测脉冲,因此xxτ=NT(其中xT为被测信号的周期)。

而对fs的计数sN则最多相差1。

所以被测信号真实的频率可以表示为:

由以上3式可以得到:

以上分析表明,测量误差仅取决于实际闸门时间的长度和标准信号的频率,其乘积越大则误差越小,而与被测信号本身无关,所以称之为等精度频率测试。

四、占空比原理分析

FPGA多加一个计数器,用来计数待测信号高电平时所计数得的数X,之后再将X除以标准信号计数的值N,所得的值为待测信号的占空比。

五、系统硬件模块

5.1单片机模块

单片机负责对测频核心FPGA和数码管的控制,由于单片机的速度慢,不能直接测量高频信号,所以使用高速FPGA为测频核心,FPGA由单片机控制,单片机的P0口负责读取数据,P2负责发送控制信号。

单片机的P0口接8位数据DATA,负责读取测频数据。

单片机可以通过结束信号了解测频记数是否结束,以确定何时开始读取数据。

P2用于控制多路通路的数据选择。

分别读出标准频率记数值和待测频率记数值。

单片机根据读取得数据计算出被测频率得数值,然后使用串行口的同步模式驱动移位寄存器显示被测信号的频率值。

图3FPGA/CPLD模块框图

5.2FPGA模块

FGPA模块框图

FPGA模块由三个高速计数器,多路选择器,门控信号发生器构成。

如图3示。

在这种设计方法中,FPGA的工作比较简单,仅仅在单片机的控制下进行简单的计数工作。

通过在FPGA中增加控制寄存器,主控模块和状态转换的功能,可以让FPGA的工作变得较为智能化,单片机仅仅发出开始测量的命令,由FPGA决定测量的周期,在测量结束时通知单片机读取数据。

FGPA模块测频过程

等精度测频的实现方法可以简单用图3来说明,图中预制门控信号CL由单片机发出,D的时间宽度可以在1s至0.1秒内选择,在此设其宽度为Tpr。

BHZ和TF是两个可控的32位高速计数器,BRNA和ENA分别是他们的计数允许信号端,高电平有效。

标准频率信号从BZH的时钟输入端BCLK输入,设其频率为Fs;经过整形后的被测信号从BHZ相似的32位计数器TF的时钟输入端TCLK输入,设其真实频率值为Fxe,测量频率为Fx。

测频开始前,首先发出一个清0信号CLR,使两个计数器和D触发器置0,然后由单片机发出允许测频命令,就是让CL=1,这时D触发器要一直等到被测信号的上升沿通过时Q端才被置1,也就是START被置为1,与此同时,启动计数器BHZ和TF,从而进入记数允许周期。

在此期间,BHZ和TF分别对被测信号和标准频率同时记数,当Tpr秒后,CL被单片机置为0,但此时两个计数器仍没有停止记数,一直等到随后而来的被测信号的上升沿到来,才通过D触发器将这个两个计数器同时关闭。

可见、CL的宽度不会影响记数使能信号START,允许记数的周期总是恰好等于待测信号TCLK的完整周期数。

这正是确保TCLK

在任何频率条件下都能保持恒定精度的关键。

而且CL宽度的改变以及随即出现的时间造成的误差最多只有BCLK信号的一个时钟周期,如果BCLK由精确稳定的晶体振荡器产生,则测量精度在一个很宽的频率范围内都可以做到恒定。

设在一次预置门时间Tpr中被测信号计数值为Nx,对标准频率信号的记数值为Ns,则有:

Fx/Nx=Fs/Ns

不难得到被测的频率为:

Fx=(Fs/Ns)*Nx

图5FPGA信号流程图

图6单片机流程图

六、模块设计

1)FPGA模块

1D触发器

moduleDchufaqi(clk,D,Q,clr);

inputclk,D,clr;

outputQ;

regQ;

//assignQ<=0;

always@(posedgeclk)

if(clr==1)Q=0;

elseif(clr==0)Q=D;

elseQ=D;

endmodule

2分频器

moduleyclk(clk1,clk);

inputclk;

outputclk1;

regclk1;

reg[7:

0]q;

always@(posedgeclk)

beginif(q<9)

q=q+1;

else

beginclk1=~clk1;

q=0;

end

end

endmodule

3计数器

计数器设计过程

modulelpm_counter0(

clock,

cnt_en,

sclr,

q);

inputclock;

inputcnt_en;

inputsclr;

output[31:

0]q;

wire[31:

0]sub_wire0;

wire[31:

0]q=sub_wire0[31:

0];

lpm_counterlpm_counter_component(

.sclr(sclr),

.clock(clock),

.cnt_en(cnt_en),

.q(sub_wire0),

.aclr(1'b0),

.aload(1'b0),

.aset(1'b0),

.cin(1'b1),

.clk_en(1'b1),

.cout(),

.data({32{1'b0}}),

.eq(),

.sload(1'b0),

.sset(1'b0),

.updown(1'b1));

defparam

lpm_counter_component.lpm_direction="UP",

lpm_counter_component.lpm_port_updown="PORT_UNUSED",

lpm_counter_component.lpm_type="LPM_COUNTER",

lpm_counter_component.lpm_width=32;

endmodule

4多路数据选择器

modulexuanzeqi(cout1,cout2,set,data,dcout);

input[31:

0]cout1;

input[31:

0]cout2;

input[31:

0]dcout;

input[3:

0]set;

output[7:

0]data;

reg[7:

0]data;

always@(set)begin

case({set})

0:

begindata<=cout1[7:

0];end

1:

begindata<=cout1[15:

8];end

2:

begindata<=cout1[23:

16];end

3:

begindata<=cout1[31:

24];end

4:

begindata<=cout2[7:

0];end

5:

begindata<=cout2[15:

8];end

6:

begindata<=cout2[23:

16];end

7:

begindata<=cout2[31:

24];end

8:

begindata<=dcout[7:

0];end

9:

begindata<=dcout[15:

8];end

10:

begindata<=dcout[23:

16];end

11:

begindata<=dcout[31:

24];end

default:

data<=0;

endcase

end

endmodule

功能:

单片机的数据总线有限,不可能一次性将两个计数器的值读入,多路选择器的作用就是将三个计数器的96位计数器暂时储存,然后在单片机发出的选择信号sel0~sel3的控制下分8次把计数值读入,每次8位。

FPGA模块总电路图:

5占空比脉宽控制器

modulemaikuan(clr,en,clk,dclk,cen);

inputclr,en,dclk,clk;

outputcen;

regcen;

always@(clk)

begin

if(clr)

cen=0;

elseif(en)

begin

if(dclk==1)

cen=1;

else

cen=0;

end

elsecen=0;

end

endmodule

功能:

保证被测信号的高电平一被测信号的计数保持同步。

总的结构图

注释:

clk:

标准信号输入(实验中接单片机内部晶振频率即CLK5);

clk1:

被测信号(实验中通过一个分频器将clk分频后作为要测试的clk1输入);

D:

单片机发出控制测频电路的门控信号(实验中接51单片机的P2.7脚);

clr:

清零信号(试验中接51单片机的P2.6脚);

data:

数据输出口(实验中接51单片的P1口);

sel[3..0]:

多路选择器的选通信号,控制8位数据输出(实验中接单片机P2.0,P2.1,P2.2,P2.3脚)。

调试波形:

波形分析仪:

单片机部分:

单片机程序1

#include

#include

#defineucharunsignedchar

#defineuintunsignedint

#defineulongunsignedlong

#defineclk

unsignedcharcodetable[10]={0xFC,0x0C,0xDA,0xF2,0x66,0xB6,0xBE,0xE0,0xFE,0xF6};

unsignedcharcodetable1[10]={0xFD,0x0D,0xDB,0xF3,0x67,0xB7,0xBF,0xE1,0xFF,0xF7};

uchardate;

uchardatab[8];

unsignedcharin[12];

xianshi();//显示子程序

cepinlv();//频率低于1M测频子程序

gcepinlv();//频率高于1M测频子程序

gxianshi();

cezhouqi();//测周期子程序

dushu();//单片机读数子程序

zouhuang();//数码管左移子程序

shanshou();//数码管闪烁子程序

cemaikuan();//测占空比子程序

zhuanghuan(ulong);//转换子程序

uinti;

ucharj;

ucharnum;

ucharbzw;

uchardushubz;

//floatn,m;

ulongn,m,hm,zq;

ulongn0,n1,n2,n3;

ulongm0,m1,m2,m3;

ulonghm0,hm1,hm2,hm3;

ulonga;

ulongx;

floath,w,k,kx;

sbitD=P2^4;

sbitCLR=P2^5;

sbitsel2=P2^0;

sbitsel1=P2^1;

sbitsel0=P2^2;

sbitsel3=P2^3;

sbitfw=P1^0;

sbitkv=P1^1;

sbitkv1=P1^2;

voiddelayms(unsignedintcc)

{

unsignedintx,y;

for(y=cc;y>0;y--)

for(x=50;x>0;x--);

}

voidfuwei()

{

num=0;

TF0=0;

CLR=1;

D=0;

TR0=0;

TI=0;

bzw=1;

for(i=0;i<8;i++)

{

SBUF=0xfc;

while(!

TI);

TI=0;

delayms

(1);

}

}

voidmain()

{

sel1=0;

sel2=0;

sel0=0;

sel3=0;

dushubz=1;

num=0;

CLR=1;

D=0;

bzw=1;

EA=1;//开总中断

ET0=1;//开定时器0中断

TMOD=0x01;

TH0=(65536-10000)/256;

TL0=(65536-10000)%256;

for(i=0;i<8;i++)

{

SBUF=0xFF;

while(!

TI);

TI=0;

delayms

(1);

}

while

(1)

{

if(fw==0)

{

fuwei();

delayms(500);

}

if(bzw==1)

{

bzw=0;

CLR=0;

TR0=1;//启动定时器0

D=1;

}

if(num==50)

{

num=0;

TR0=0;

D=0;

dushu();

w=n/m;

cemaikuan();

cezhouqi();

if(w>=20)

{

cepinlv();

zhuanghuan(a);

zouhuang();

shanshou();

xianshi();

}

else

{

gcepinlv();

zhuanghuan(a);

zouhuang();

shanshou();

gxianshi();

}

}

if(kv1==0)

{

//cezhouqi();

zhuanghuan(zq);

shanshou();

gxianshi();

}

if(kv==0)

{

zhuanghuan(x);

shanshou();

xianshi();

}

}

}

dushu()

{

for(i=0;i<12;i++)

{

j=0Xf0&P2;

j=j+i;

P2=j;

in[i]=P0;

delayms(100);

}

n3=in[3]*0x;

n2=in[2]*0x;

n1=in[1]*0x;

n0=in[0]*0x;

n=n3+n2+n1+n0;

m3=in[7]*0x;

m2=in[6]*0x;

m1=in[5]*0x;

m0=in[4]*0x;

m=m3+m2+m1+m0;

hm3=in[11]*0x;

hm2=in[10]*0x;

hm1=in[9]*0x;

hm0=in[8]*0x;

hm=hm3+hm2+hm1+hm0;

}

cemaikuan()

{

//kx=hm/n;

k=10000/(n/hm);

x=(ulong)k;

}

cepinlv()

{

h=(clk/w)*100;

a=(ulong)h;

}

gcepinlv()

{

h=clk/w;

a=(ulong)h;

}

cezhouqi()

{

zq=/(clk/w);

}

zhuanghuan(ulongxx)

{

b[0]=xx/;

b[1]=xx%/;

b[2]=xx%%/;

b[3]=xx%%%/10000;

b[4]=xx%%%%10000/1000;

b[5]=xx%%%%10000%1000/100;

b[6]=xx%%%%10000%1000%100/10;

b[7]=xx%10;

}

xianshi()

{

for(i=0;i<8;i++)

{

j=b[i];

if(i!

=5)

SBUF=table[j];

else

SBUF=table1[j];

while(!

TI);

TI=0;

delayms(100);

}

}

gxianshi()

{

for(i=0;i<8;i++)

{

j=b[i];

SBUF=table[j];

while(!

TI);

TI=0;

delayms(100);

}

}

zouhuang()

{

for(i=0;i<8;i++)

{

SBUF=0xFC;

while(!

TI);

TI=0;

delayms(500);

}

}

shanshou()

{

for(j=0;j<5;j++)

{for(i=0;i<8;i++)

{

SBUF=0xFC;

while(!

TI);

TI=0;

delayms

(1);

}

delayms(200);

for(i=0;i<8;i++)

{

SBUF=0x00;

while(!

TI);

TI=0;

delayms

(1);

}

delayms(500);

}

}

voidtime0()interrupt1

{

TH0=(65536-10000)/256;

TL0=(65536-10000)%256;

TF0=0;

num++;

}

单片机程序2

实验结果:

1、标准信号Fs=hz时,100分频后fx=20000hz

2、待测频率值:

3、待测信号占空比:

4、待测信号占空比:

液晶屏扩展:

心得总结:

通过这两周的电子系统课程设计,深刻的贯彻了学以致用的教育方针和让我们更深的了解了电子系统的应用及其强大的功能,本次课程设计主要以fpga和单片机相结合,设计一个完整的应用性事物——等精度测频器。

短短两周让我们学到了很多很多,从刚开始的懵懵懂懂到两周后的熟练掌握应用。

让我们感到真为电子人的骄傲,今后我们会更加努力学习好相关知识,掌握好技能。