DS1023中文翻译.docx

《DS1023中文翻译.docx》由会员分享,可在线阅读,更多相关《DS1023中文翻译.docx(13页珍藏版)》请在冰豆网上搜索。

DS1023中文翻译

1.DS1023延时芯片

8bit可编程定时元件

特性:

⏹步长类型:

0.25ns,0.5ns,1ns,2ns,5ns

⏹片上参考延时

⏹可配置的脉冲宽度、延时线、调制器或自激振荡器

⏹可以延时1个整周期甚至更长

⏹保证单调性

⏹并行或者串行可编程

⏹单5V供电

⏹16引脚的DIP(双列直插式封装)或者SOIC(小外形集成电路)封装

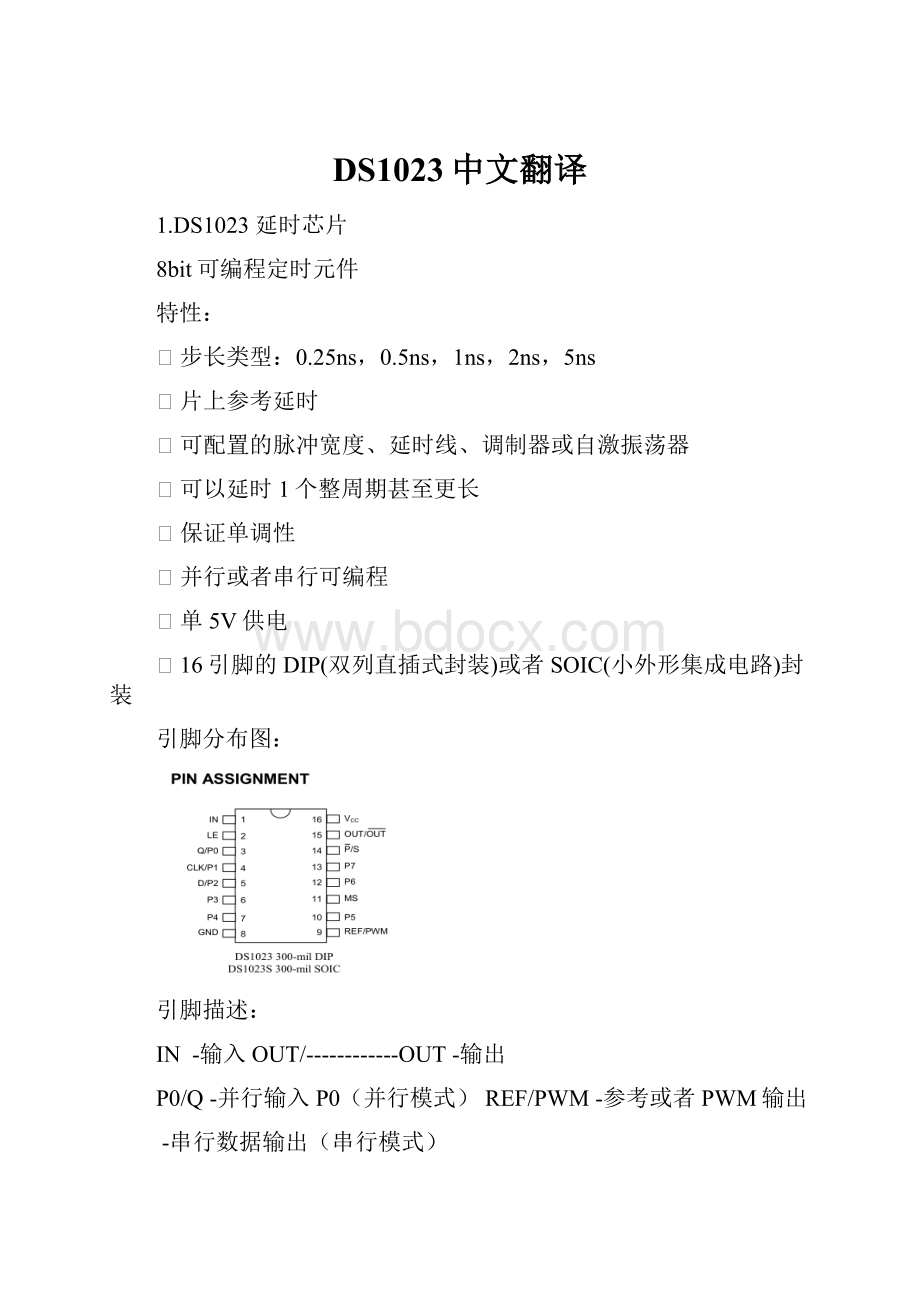

引脚分布图:

引脚描述:

IN-输入OUT/------------OUT-输出

P0/Q-并行输入P0(并行模式)REF/PWM-参考或者PWM输出

-串行数据输出(串行模式)

P1/CLK-并行输入P1(并行模式)----P/S-并行/串行可编程选择

-串行输入时钟(串行模式)

P2/D-并行输入P2(并行模式)MS-输出模式选择

-串行数据输入(串行模式)

P3-P7-剩余的并行输入口LE-输入锁存使能

GND-地VCC-提供电压

描述:

DS1023是一个8bit可编程延时线,在功能方面类似于DS1020/DS1021.

额外增加的特性用于扩大应用范围:

内部的延时线结构经过优化修改,已经可以使得信号被延时至1个整周期甚至更长的时间。

和一个片上参考延时(用来抵消芯片固有延时或称为“0档位”延时)相结合,时钟相位可以有0-360°的变化范围。

片上选通允许设备提供一个脉宽调制输出,由输入值触发,输入持续时间由编程值设定。

如果外部输出端和输入端连接,那么芯片的二选一输出信号可以反转,此时可将其看作一个自激振荡器。

可编程:

芯片的可编程性和DS1020/DS1021一样。

串行的时钟和数据3个引脚,是和并行的输入引脚复用的。

----P/S引脚的功能是“模式选择”,和DS1020/DS1021一样。

低电平使能并行模式:

只有在LE是高电平时,编程值才会改变;LE是低电平时,数据锁存,并行输入值改变不会影响可编程值。

这对于多路复用是有用的。

对于硬连线的应用来说,LE应该束缚于高电平。

当----P/S引脚置高,使能串行模式:

LE必须维持高电平才能装载或者读取内部寄存器的值,延时时间由之前设定的值决定。

在时钟的上升沿数据导入。

当LE置低,数据传输结束,新的值激活。

并行模式:

并行可编程模式中,经过一段延时,DS1023的输出会和输入的逻辑状态保持一致。

延时时间由输入管脚P0~P7决定。

可编程的并行输入可以使用直流电平,也可以使用计算机产生的数据。

少量的修改延时值,跳线就可能把输入管脚连接到VCC或者GND。

对于进行频繁时间调整的应用来说,DIP封装适合。

当使用计算机生成的数据时,8bit并行可编程芯片具有最大限度的灵活性。

......P2

串行模式:

串行可编程模式中,经过一段延时,DS1023的输出会和输入的逻辑状态保持一致。

延时时间由串口D的8bit输入值来决定。

当观察datasetup和datahold时,时序数据在时钟的上升沿从最高有效位装载至最低有效位。

在装载或者读取内部8位输入寄存器时,LE应该为1。

当LE变为0时,数据传输结束,新的延时值被激活。

当延时值被移入串行数据输入D时,先前的8bit输入寄存器中的数据按照从高到低的顺序从输出口Q输出。

将一个DS1023的串行输出口和另一个DS1023的串行输入口相连,许多这样的设备首尾相接,就形成了用于可编程目的的daisy-chain(菊花链)(级联结构)。

如图1所示,串行bit总数必须8倍于“单位菊花链”的个数而且8bit数据必须按照从高到低的顺序打入。

如图2所示,通过用一个值为1KΩ-10KΩ的电阻连接串行输出口Q和串行输入口D,应用可以读取DS1023延时线的设定。

因为读过程是有破坏性的,电阻还原了读的值而且在向设备写的过程中提供了绝缘。

电阻一定要将最后一个设备的串行输出Q和第一个设备的串行输入D连接。

串行读出器通过一个电阻自动复位,设备在写串行数据时处于高阻态。

初始化串行读取,LE为1,CLK为0。

在一段等待时间(tEQV)后,bit7(最高有效位)出现在串口输出(Q)。

在第一个时钟上升沿,bit7重写,在一段时间tCQV后,bit6出现在串口输出。

为了还原输入寄存器的初始状态,这个时钟过程要被重复8次。

如果是菊花链,这个过程要在每个组件上重复8次。

如果读取的值在LE置0前还原,就不需要校正时间(tEDV),编程延时保持不变。

因为DS1023是CMOS设计,未使用的输入引脚(P3-P7)应该连接定义明确的逻辑电平,一定不能悬空。

串口输出Q/P0如果不用要悬空。

图1和图2

参考延时:

所有的延时线都有固有延时,这是由于从输入缓冲器到输出缓冲器存在传播延迟。

在DS1023中,与延时步长相比,固有延时是很大的。

为了简化系统设计,一个参考延时被包含在了片上,用来抵消固有延时。

这就意味着DS1023输出的最小可编程延时相对于参考延时来说实际上是0。

对于高精度来说,强烈推荐使用参考延时。

输入电平和转变次数的变化能够显著改变被测量的延时。

如果使用了参考延时输出,上述影响将被完全消除。

而且,温漂的不利影响也将被消除。

输入脉冲持续时间:

DS1023的内部结构使得输出延时时间要比输入脉宽长很多。

这个特性在很多应用中都很有用,特别是在时钟相位控制方面,延时可达1个整周期。

模式选择:

DS1023有4种输出功能但只有两个输出引脚。

这两个输出引脚的功能是由模式选择(MS)引脚所决定的。

OUT是输入波形经过延时后的输出。

可编程延时值0的结果是一个非零的延时。

输出信号OUT的极性与输入相同。

REF是一个固定的参考延时。

它也是输入波形的复制,但是延时间隔固定于一个近似于“0步长值”的值。

事实上,设备要确保参考延时总比“0步长值”要略微长。

(1.5ns)

PWM是由输入波形的上升沿触发的输出。

一段近似于“0步长”的时间间隔后,PWM输出高电平。

参照TAB1,一段时间间隔后输出将变为低电平。

因此可以获得从0到整个延时范围的输出脉宽。

最小输出脉宽被设备的反应时间所限制,约为5ns。

编程值小于这个值将会导致输出高电平直到最后没有可分辨的输出脉冲产生。

输出的频率/重复率由输入频率决定。

输入脉宽可以比输出脉宽短,输出脉宽被最短的输入脉宽限制。

PWM的功能不是可再次触发的,后来的输入触发脉冲直到输出变为低电平才起作用。

------------OUT是输入波形的反向输出。

可编程的0值结果是非零的延时值。

------------OUT引脚连接输入引脚会产生一个自激振荡器。

振荡频率由可编程延时值决定(见表2)。

测试设置描述:

图8举例说明了用于测试DS1023时间参数的硬件配置。

在软件控制下,一个精密脉冲产生器产生输入波形。

时间延时被一个连接在输出端的分辨率为20ps的时间间隔计数器测量。

DS1023的串行和并行口通过接口被中心计算机所控制。

所有的测量都是全自动的,每个仪器都在IEEE488总线协议下被计算机所控制。

测试环境:

输入:

外界环境温度:

25℃±3℃

电压:

5.0V±0.1V

输入脉冲:

高电平=3.0V±0.1V

低电平=0.0V±0.1V

电源阻抗:

最大50Ω

上升和下降时间:

最大3.0ns(在0.6V-2.4V间测量)

脉宽:

500ns

周期:

1μs

注:

以上所有条件只用于测试,在其他条件下并不限制操作。

输出:

输出装载着一个74F04(fast反相器)。

延时的测量是通过测量输入信号上升沿的1.5V位置和输出脉冲相应边沿1.5V的位置来得到的。

绝对最大额定参数*:

任意引脚电压:

-1.0V~+7.0V

工作温度范围:

0℃~70℃

贮藏温度:

-55℃~125℃

焊接温度:

260℃(10s)

短路输出电流:

50mA(1s)

*这只是一个强调参数。

在上述以外的条件下进行的操作并未指明。

把器件放在绝对最大额定参数下使用会影响器件的可靠性。

注:

1.延时从输入到输出有可编程延时值0

2.这是REF和OUT间的相对延时。

当可编程值为0延时,OUT输出总比REF输出早。

这个参数数值上等于tD0-tREF。

(见图15)

3.参考延时接近0步长延时,相对时间接近0。

4.最糟糕的情况就是SubDAC从最大值转换至最小值。

其他步长均为±0.5lsb。

这个结论不适用于不使用SubDAC的200系列和500系列。

(见图14)

5.实际测量延时是从IN到OUT。

这个参数将会显示出比相对延时参数更大的温度变化。

6.图15是实际测量延时相对于REF输出。

这个参数比绝对延时参数更接近反应可编程延时值。

7.图13的直线反映了在0步长延时值和最大可编程延时值间的最大误差。

相对于REF输出,它象征着测量延时和可编程延时间的最大误差。

另外从IN到OUT的绝对延时抵消的误差等于0步长延时和它的公差。

8.当选择了反向输出模式而不是普通、非反向输出模式,延时值要改变。

9.在PWM模式下,延时在输入上升沿和输出上升沿之间。

10.PWM脉宽的最小值应可编程。

较窄的脉宽可编程但输出会被削减,最终无输出产生。

11.在输入的过渡时间内允许的最小时间间隔来确保设备操作的准确性。

违反这个参数设置时间精度将削减,最终非常窄的脉宽将导致设备无输出。

12.这个参数只用于普通延时模式。

50%占空比的输入时钟时,最高时钟频率是可用的。

但是如果输入时钟是不对称的,可用的最高频率降低直到满足最小输入脉宽要求。

在PWM模式下,最小输入周期等于0步长延时+可编程延时(tD0+tD)。

13.测量从输入上升沿到输出上升沿(tDR)。

14.从上升沿到上升沿。

15.在测量延时时,更快的上升和下降时间将更为精确。

缓慢的边沿变化将使得结果不稳定。

16.最小和最大的限制不适用于253-255步长。

只有典型值适用。

术语:

Period:

(周期)在第一个脉冲的前沿和紧接着的脉冲的前沿间消逝的时间。

tw1(脉宽):

1.5V前沿到1.5V后沿间的时间。

tRISE(输入上升时间):

输入脉冲前沿的20%上升至80%所用的时间。

tFALL(输入下降时间):

输入脉冲后沿的80%下降至20%所用的时间。

tD(时间延时):

输入1.5V的边沿到输出1.5V的相应边沿间所用的时间。

注:

1)tDREF=255*标准步长。

2)因为tD0要比tREF小,所以实际步长要比标准值略大。

3)因此绝对延时值(tDMAX-tD0)的范围要比标准范围(tDREF0)大。