实验八 数字电路功能与实现.docx

《实验八 数字电路功能与实现.docx》由会员分享,可在线阅读,更多相关《实验八 数字电路功能与实现.docx(89页珍藏版)》请在冰豆网上搜索。

实验八数字电路功能与实现

实验八数字电路功能与实现

本章运用FPGA来完成数字电路的功能实现。

数字电路实验主要包括4位全加器、触发器、8位计数器、8位乘法器、锁存器、7段数码管显示译码器以及七人投票表决器,文中介绍了实验原理、ISE功能仿真、chipscope在线观测与调试。

8.14位全加器实验

1.实验原理

全加器是指能进行加数、被加数和低位来的进位信号相加,并根据求和结果给出该位的进位。

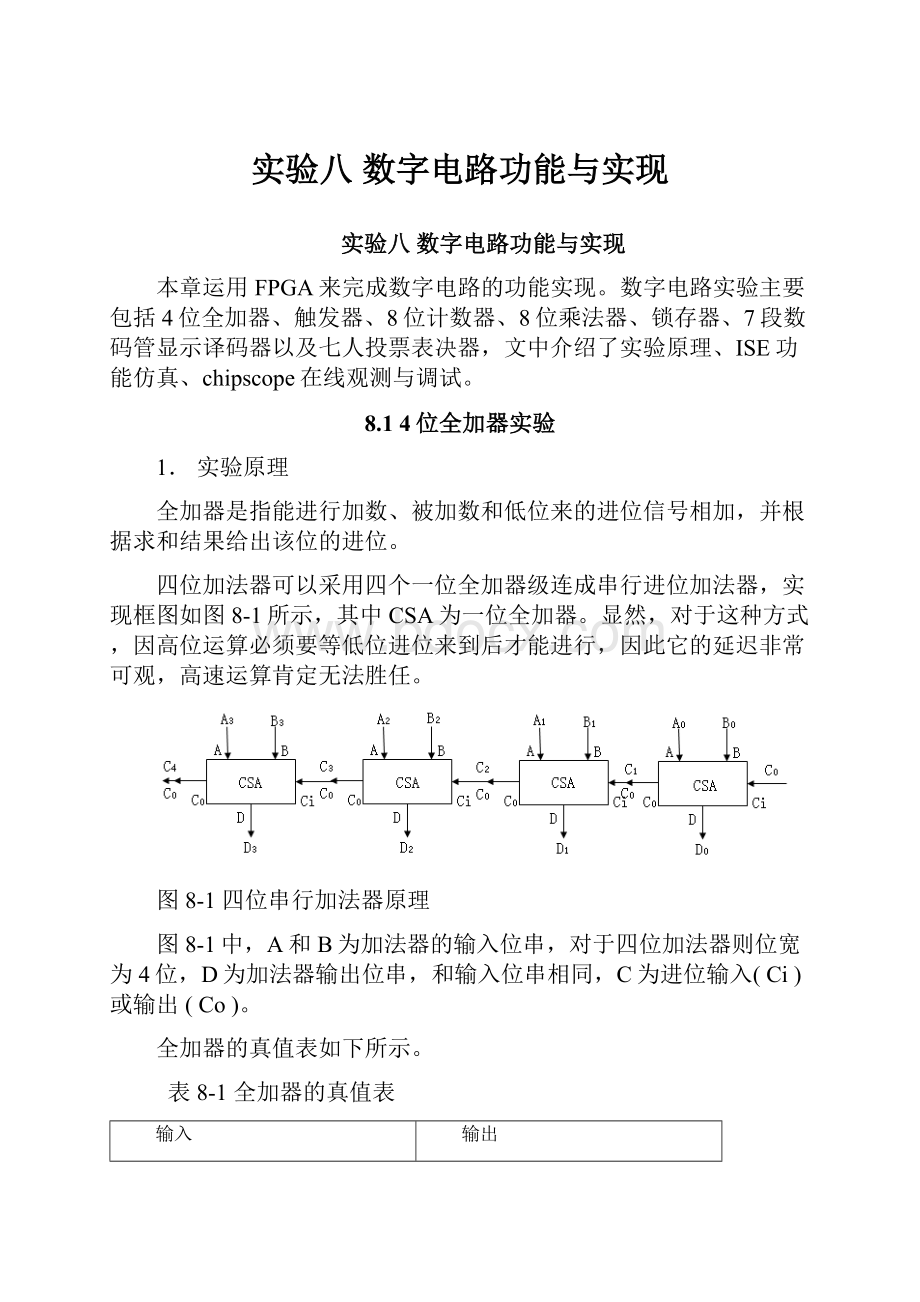

四位加法器可以采用四个一位全加器级连成串行进位加法器,实现框图如图8-1所示,其中CSA为一位全加器。

显然,对于这种方式,因高位运算必须要等低位进位来到后才能进行,因此它的延迟非常可观,高速运算肯定无法胜任。

图8-1四位串行加法器原理

图8-1中,A和B为加法器的输入位串,对于四位加法器则位宽为4位,D为加法器输出位串,和输入位串相同,C为进位输入(Ci)或输出(Co)。

全加器的真值表如下所示。

表8-1全加器的真值表

输入

输出

XiYiCi-1

SiCi

000

001

010

011

100

101

110

111

00

10

10

01

10

01

01

11

实现代码为:

moduleadder4(cout,sum,ina,inb,cin);

output[3:

0]sum;

outputcout;

input[3:

0]ina,inb;

inputcin;

assign{cout,sum}=ina+inb+cin;

endmodule

2.实验目的

(1)熟悉ISE9.1开发环境,掌握工程的生成方法;

(2)熟悉SEED-XDTKXUPV2Pro实验环境;

(3)了解VerilogHDL语言在FPGA中的使用;

(4)了解4位全加器的VerilogHDL语言实现。

3.实验内容

(1)用VerilogHDL语言设计4位全加器,进行功能仿真验证;

(2)使用chipscope-Pro生成ILA/ICON核,在线观测调试。

4.实验准备

(1)将USB下载电缆与计算机及XUPV2Pro板的J8连接好;

(2)将RS232串口线一端与计算机连接好,另一端与板卡的J11相连接;

(3)启动计算机后,将XUPV2Pro板的电源开关SW11打开到ON上。

观察XUPV2Pro板上的+2.5V,+3.3V,+1.5V的电源指示灯是否均亮,若有不亮的,请断开电源,检查电源;

5.实验步骤

(1)创建工程及设计输入

1)在E:

\project\目录下,新建名为count8的新工程;

器件族类型(DeviceFamily)选择“Virtex2P”

器件型号(Device)选“XC2VP30ff896-7”

综合工具(SynthesisTool)选“XST(VHDL/Verilog)”

仿真器(Simulator)选“ISESimulator”

2)设计输入,在源代码窗口中单击右键,在弹出的菜单中选择NewSource,在弹出的对话框中选择VerilogMoudle,在右端的Filename中输入源文件名adder4,下面各步点next,然后在弹出的源代码编辑框内输入前面所示的源代码并保存即可。

(2)功能仿真

1)在sources窗口sourcesfor中选择BehavioralSimulation;

2)由TestBenchWaveForm添加激励源,如下图所示。

图8-2波形激励编辑窗口

然后在processes窗口中点击simulaterbehavioralmodel即开始仿真,仿真结果如下:

图8-3仿真结果

从图中可以验证由VerilogHDL语言设计的4位全加器的工作是正确的。

由于此全加器没有时钟输入,所以不必进行UserConstraints。

(3)用chipscope进行在线调试

这里使用的是核生成法。

1)生成chipscope核

代码比较简单,这里只需要ICON和VIO这两个核即可。

打开chipscopeprocoregenerator,下面的8-4图至8-6图是ICON核的生成过程,8-7图至8-8图是VIO核的生成过程。

图8-4操作示意

图8-5操作示意

在outputnetlist位置指向adder4所在的路径,在devicefamily里选virtex2p器件,由于只用了VIO核,所以ICON的控制端口数设置为1。

图8-6操作示意

如上图中选定HDL语言为verilog,综合工具为xilinxXST。

在接下来的VIO和生成过程中,选定VIO前的复选框进入VIO核的生成过程。

路径也选择adder4所在位置,器件类型为virtex2p,然后在输入输出端口设置过程中选定异步输入端口和异步输出端口。

异步输入端口宽度根据ina(4位)、inb(4位)、cin(1位)、sum(4位)、cout(1位)的总位数设定,异步输出端口根据ina(4位)、inb(4位)、cin(1位)的总位数设定。

如下面两图所示。

图8-7操作示意

图8-8操作示意

2)添加ICON和VIO核到工程

点击file>open,在adder4所在位置找到icon_xst_example.v和vio_xst_example.v文件并打开,将两部分的模块声明加到源代码中endmodule后面,然后分别将icon_xst_example.v,vio_xst_example.v示例中例化模块所用到的代码加到adder4.v相应的位置,并进行修改,最后得到的代码如下:

moduleadder4(cout,sum);

output[3:

0]sum;

outputcout;

wire[3:

0]ina,inb;

wirecin;

wire[35:

0]control0;

wire[13:

0]async_in;

wire[8:

0]async_out;

iconi_icon

(

.control0(control0)

);

vioi_vio

(

.control(control0),

.async_in(async_in),

.async_out(async_out)

);

assignasync_in[3:

0]=ina[3:

0];

assignasync_in[7:

4]=inb[3:

0];

assignasync_in[8]=cin;

assignasync_in[12:

9]=sum[3:

0];

assignasync_in[13]=cout;

assignina[3:

0]=async_out[3:

0];

assigninb[3:

0]=async_out[7:

4];

assigncin=async_out[8];

assign{cout,sum}=ina+inb+cin;

endmodule

moduleicon

(

control0

);

output[35:

0]control0;

endmodule

modulevio

(

control,

async_in,

async_out

);

input[35:

0]control;

input[13:

0]async_in;

output[8:

0]async_out;

endmodule

然后在ISE里进行综合、实现并generateprogrammingfile。

3)在chipscope里观测调试

点击analyzedesignusingchipscope进入chipscopeproanalyzer窗口,点击

图标,找到前面生成的比特文件,在所用器件名上右击然后选configuration将bit文件下载到板子上,然后打开vioconsle窗口,在这里即可进行观测调试,调试结果如下面两图所示。

图8-9调试结果

图8-10调试结果

在这里可以看出全加器的设计是正确的。

8.2触发器实验

1.实验原理

(1)主从D触发器

下面是主从触发器的逻辑图及逻辑符号。

图8-11主从触发器原理图

主从结构的触发器状态改变是在时钟脉冲下降沿完成的,因而这种结构的触发器无空翻现象。

若CP下降沿前D=1,则Qn+1=1;若CP下降沿前D=0,则Qn+1=0。

代码如下:

moduledtrigger(Q,QB,clk,D);

inputclk,D;

outputQ,QB;

regQ,QB;

always@(negedgeclk)

begin

Q<=D;

QB=~Q;

end

endmodule

(2)主从JK触发器

主从JK触发器的逻辑图及逻辑符号如图8-12所示,其状态转换是在时钟下降沿完成的。

图8-12JK触发器原理图

其真值表如下表所示。

表8-2真值表

Verilog代码如下:

modulejktrigger(Q,QB,J,K,clk);

inputJ,K,clk;

outputQ,QB;

regQ;

assignQB=~Q;

always@(negedgeclk)

begin

case({J,K})

2'b00:

Q<=Q;

2'b01:

Q<=1'b0;

2'b10:

Q<=1'b1;

2'b11:

Q<=~Q;

default:

Q<=1'bx;

endcase

end

endmodule

(3)JK触发器转换的D触发器

真值表如下表所示。

表8-3真值表

根据上表可写出JK与D、Q的关系:

J=D、K=/D

图8-13JK转D触发器原理图

Verilog代码如下:

modulejkdtrigger(cp,D,Qn,Qnb);

inputcp,D;

outputQn,Qnb;

wireJ,K;

jktriggera2(Qn,Qnb,J,K,cp);

nota1(K,D);

assignJ=D;

endmodule

modulejktrigger(Q,QB,J,K,clk);

inputJ,K,clk;

outputQ,QB;

regQ;

assignQB=~Q;

always@(negedgeclk)

begin

case({J,K})

2'b00:

Q<=Q;

2'b01:

Q<=1'b0;

2'b10:

Q<=1'b1;

2'b11:

Q<=~Q;

default:

Q<=1'bx;

endcase

end

endmodule

此代码中添加了子模块jktrigger();说明程序写法有自上而下的特点。

2.实验目的

(1)熟悉ISE9.1开发环境,掌握工程的生成方法;

(2)熟悉SEED-XDTKXUPV2Pro实验环境;

(3)了解VerilogHDL语言在FPGA中的使用;

(4)了解触发器的VerilogHDL语言实现。

3.实验内容

(1)用VerilogHDL语言设计D触发器、JK触发器和JK触发器转换的D触发器,进行功能仿真验证;

(2)使用chipscope-Pro生成ILA/ICON核,在线观测调试。

4.实验准备

(1)将USB下载电缆与计算机及XUPV2Pro板的J8连接好;

(2)将RS232串口线一端与计算机连接好,另一端与板卡的J11相连接;

(3)启动计算机后,将XUPV2Pro板的电源开关SW11打开到ON上。

观察XUPV2Pro板上的+2.5V,+3.3V,+1.5V的电源指示灯是否均亮,若有不亮的,请断开电源,检查电源;

5.实验步骤

(1)D触发器设计

1)创建工程及设计输入

◆在E:

\project\目录下,新建名为dtrigger的新工程;

器件族类型(DeviceFamily)选择“Virtex2P”

器件型号(Device)选“XC2VP30ff896-7”

综合工具(SynthesisTool)选“XST(VHDL/Verilog)”

仿真器(Simulator)选“ISESimulator”

◆设计输入,在源代码窗口中单击右键,在弹出的菜单中选择NewSource,在弹出的对话框中选择VerilogMoudle,在右端的Filename中输入源文件名dtrigger,下面各步点next,然后在弹出的源代码编辑框内输入D触发器的源代码并保存即可。

2)功能仿真

◆在sources窗口sourcesfor中选择BehavioralSimulation;

◆由TestBenchWaveForm添加激励源,如下图所示;

图8-14波形激励编辑窗口

然后在processes窗口中点击simulaterbehavioralmodel开始仿真,仿真结果如下:

图8-15仿真结果

从图中可以验证由VerilogHDL语言设计的D触发器的工作是正确的。

3)添加引脚约束

◆首先对生成的工程进行综合;

◆添加引脚约束。

双击UserConstraints下的AssignPackagePins,由于采用chipscope进行调试,因此引脚约束只需要添加时钟引脚的约束就可以了,如图8-16所示。

图8-16引脚约束

4)Chipscope进行调试

这里也是用的核生成法,所用到的核有ICON核和VIO核。

◆生成ICON核和VIO核

核的生成过程同4位加法器里的生成过程一样。

ICON的生成中文件路径指向dtrigger所在位置,器件类型为virtex2p,控制端口数为1,语言为verilog,综合工具为xilinxXST。

VIO的生成中,异步输入端口宽度为3,异步输出端口数为1。

◆添加ICON和VIO核到工程

点击file>open,在dtrigger所在位置找到icon_xst_example.v和vio_xst_example.v文件并打开,将两部分的模块声明加到源代码中endmodule后面,然后分别将icon_xst_example.v,vio_xst_example.v示例中例化模块所用到的代码加到dtrigger.v相应的位置,并进行修改,最后得到的代码如下:

moduledtrigger(Q,QB,clk);

inputclk;

outputQ,QB;

regQ,QB;

wireD;

wire[35:

0]control0;

wire[2:

0]async_in;

wireasync_out;

assignasync_in[0]=D;

assignasync_in[1]=Q;

assignasync_in[2]=QB;

assignD=async_out;

iconi_icon

(

.control0(control0)

);

vioi_vio

(

.control(control0),

.async_in(async_in),

.async_out(async_out)

);

always@(negedgeclk)

begin

Q<=D;

QB=~Q;

end

endmodule

moduleicon

(

control0

);

output[35:

0]control0;

endmodule

modulevio

(

control,

async_in,

async_out

);

input[35:

0]control;

input[2:

0]async_in;

output[0:

0]async_out;

endmodule

◆在chipscope里观测调试

点击analyzedesignusingchipscope进入chipscopeproanalyzer窗口,点击

图标,找到前面生成的比特文件,在所用器件名上右击然后选configuration将bit文件下载到板子上,然后打开vioconsole窗口,在这里即可进行观测调试,调试结果如下面两图所示。

图8-17调试结果

图8-18调试结果

(2)JK触发器设计

1)创建工程及设计输入

◆在E:

\project\目录下,新建名为jktrigger的新工程;

器件族类型(DeviceFamily)选择“Virtex2P”

器件型号(Device)选“XC2VP30ff896-7”

综合工具(SynthesisTool)选“XST(VHDL/Verilog)”

仿真器(Simulator)选“ISESimulator”

◆设计输入,在源代码窗口中单击右键,在弹出的菜单中选择NewSource,在弹出的对话框中选择VerilogMoudle,在右端的Filename中输入源文件名jktrigger,下面各步点next,然后在弹出的源代码编辑框内输入JK触发器的源代码并保存即可,工程名称为jktrigger。

2)功能仿真

由TestBenchWaveForm添加激励源,如下图所示。

图8-19波形激励编辑窗口

仿真结果如下图所示:

图8-20仿真结果

由图中可以看出JK触发器的设计是正确的。

3)添加引脚约束

◆首先对生成的工程进行综合;

◆添加引脚约束。

双击UserConstraints下的AssignPackagePins,由于采用chipscope进行调试,因此引脚约束只需要添加时钟引脚的约束就可以了,如图8-21所示。

图8-21引脚约束

4)Chipscope进行调试

用核生成法,所用到的核有ICON核和VIO核。

按照前面的步骤生成ICON核和VIO核并将它们添加到工程。

ICON核的控制端口数为1,VIO核的异步输入端口宽度为4,异步输出端口宽度为2。

最后得到的代码如下:

modulejktrigger(Q,QB,clk);

inputclk;

outputQ,QB;

regQ;

wireJ;

wireK;

wire[35:

0]control0;

wire[3:

0]async_in;

wire[1:

0]async_out;

iconi_icon

(

.control0(control0)

);

vioi_vio

(

.control(control0),

.async_in(async_in),

.async_out(async_out)

);

assignasync_in[0]=J;

assignasync_in[1]=K;

assignasync_in[2]=Q;

assignasync_in[3]=QB;

assignJ=async_out[0];

assignK=async_out[1];

assignQB=~Q;

always@(negedgeclk)

begin

case({J,K})

2'b00:

Q<=Q;

2'b01:

Q<=1'b0;

2'b10:

Q<=1'b1;

2'b11:

Q<=~Q;

default:

Q<=1'bx;

endcase

end

endmodule

moduleicon

(

control0

);

output[35:

0]control0;

endmodule

modulevio

(

control,

async_in,

async_out

);

input[35:

0]control;

input[3:

0]async_in;

output[1:

0]async_out;

endmodule

在chipscopeproanalyzer里的VIOconsole里观测到的调试结果如下面几图所示:

图8-22调试结果

J=1,K=0时,将Q置1。

图8-23调试结果

J=0,K=0时,Q保持不变。

图8-24调试结果

J=0,K=1时,将Q置0

图8-25调试结果

图8-26调试结果

J=1,K=1时可以看到Q和QB不断地翻转。

因此,从调试结果分析可知JK触发器的设计是正确的。

(3)JK触发器转换为D触发器的设计

1)创建工程及设计输入

◆在E:

\project\目录下,新建名为jkdtrigger的新工程;

器件族类型(DeviceFamily)选择“Virtex2P”

器件型号(Device)选“XC2VP30ff896-7”

综合工具(SynthesisTool)选“XST(VHDL/Verilog)”

仿真器(Simulator)选“ISESimulator”

◆设计输入,在源代码窗口中单击右键,在弹出的菜单中选择NewSource,在弹出的对话框中选择VerilogMoudle,在右端的Filename中输入源文件名jkdtrigger,

下面各步点next,然后在弹出的源代码编辑框内输入JK触发器的源代码并保存即可,工程名称为jkdtrigger。

2)功能仿真

由TestBenchWaveForm添加激励源,如下图所示:

图8-27波形激励编辑窗口

仿真结果如下图所示:

图8-28仿真波形

从图中可以看出此设计是正确的。

3)添加引脚约束

◆首先对生成的工程进行综合;

◆添加引脚约束。

双击UserConstraints下的AssignPackagePins,由于采用chipscope进行调试,因此引脚约束只需要添加时钟引脚的约束就可以了,如图所示:

图8-29引脚约束

4)Chipscope进行调试

用核生成法,所用到的核有ICON核和VIO核。

按照前面的步骤生成ICON核和VIO核并将它们添加到工程。

ICON核的控制端口数为1,VIO核的异步输入端口宽度为5,异步输出端口宽度为1。

最后得到的代码如下:

modulejkdtrigger(cp,Qn,Qnb);

inputcp;

outputQn,Qnb;

wireD;

wireJ,K;

wire[35:

0]control0;

wire[4:

0]async_in;

wireasync_out;

assignasync_in[0]=D;

assignasync_in[1]=J;

assignasync_in[2]=K;

assignasync_in[3]=Qn;

assignasync_in[4]=Qnb;

assignD=async_out;

iconi_icon

(

.control0(control0)

);

vioi_vio

(

.control(control0),

.asy