第四章功能扩展.docx

《第四章功能扩展.docx》由会员分享,可在线阅读,更多相关《第四章功能扩展.docx(42页珍藏版)》请在冰豆网上搜索。

第四章功能扩展

第四章89C51的功能扩展

第一节最小应用系统与总线结构

一、单片机最小系统:

使单片机能运行的最少器件构成的系统,就是最小系统。

复位、晶振电路是必须的;如片内无ROM芯片:

如8031必须扩展ROM,现在应用很少,但许多实验箱中都用的8031。

如果片内有ROM芯片,如AT89c51、AT89c52等,构成最小系统时不必扩展ROM,只要有复位、晶振电路即可工作。

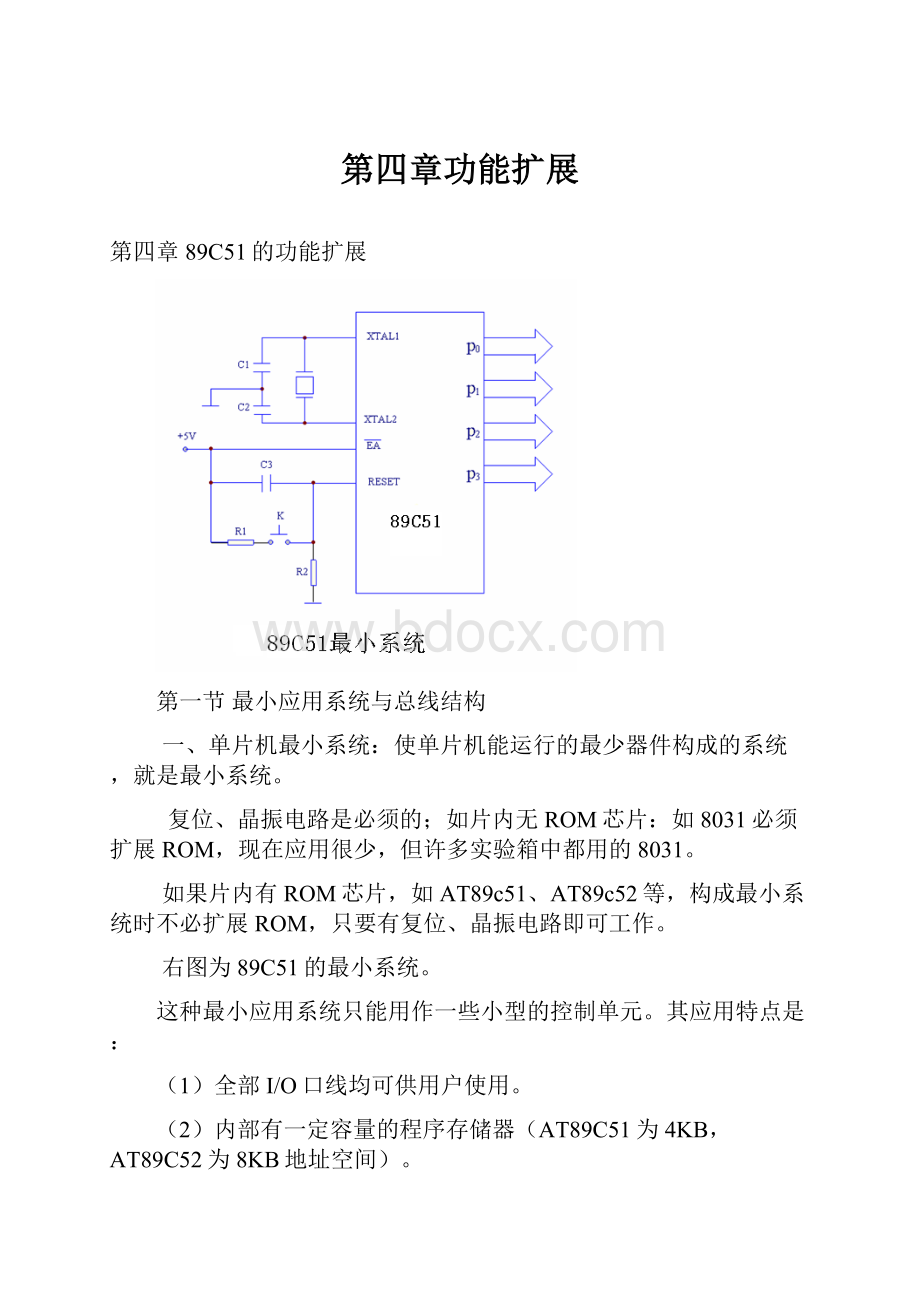

右图为89C51的最小系统。

这种最小应用系统只能用作一些小型的控制单元。

其应用特点是:

(1)全部I/O口线均可供用户使用。

(2)内部有一定容量的程序存储器(AT89C51为4KB,AT89C52为8KB地址空间)。

(3)内部的数据存储容量很小,不宜处理数据较多的情况。

二、89C51单片机的三总线结构

程序存储允许信号输出端

89C51系列单片机片外引脚可以构成如图所示的三总线结构:

地址总线(AB)(P0、P2)

•地址总线(AddressBus,AB)用于传送单片机送出的地址信号,以便进行存储单元和I/O端口的选择。

•地址总线是单向的,只能由单片机向外发送信息。

地址总线的数目决定了可直接访问的存储单元的数目。

•例如,n位地址可以产生2n个连续地址编码,因此,可访问2n个存储单元,即通常所说的寻址范围为2n个地址单元。

89C51单片机存储器扩展最多可达64KB,即216个地址单元,因此,最多需16位地址。

数据总线(DB)(P0)

•数据总线(DataBus,DB)用于单片机与存储器之间或单片机与I/O端口之间传送数据。

•数据总线的位数与单片机处理数据的字长一致。

•例如,89C51单片机是8位字长,所以,数据总线的位数也是8位。

数据总线是双向的,可以进行两个方向的数据传送。

控制总线(CB)

控制总线(ControlBus,CB)是单片机发出的以控制片外ROM、RAM和I/O口读/写操作的一组控制线。

外部芯片一般通过这三组总线进行扩展。

三、扩展注意事项:

1、接口驱动能力。

在单片机应用系统中,扩展的三总线上挂接很多负载,如存储器、并行接口、A/D接口、显示接口等,但总线接口的负载能力有限,因此常常需要通过连接总线驱动器进行总线驱动。

总线驱动器对于单片机的I/O口只相当于增加了一个TTL负载,因此驱动器除了对后级电路驱动外,还能对负载的波动变化起隔离作用。

2、电平兼容。

在对TTL负载驱动时,只需考虑驱动电流的大小;在对MOS负载驱动时,MOS负载的输入电流很小,更多地要考虑电平的兼容和分布电容的电流。

一般TTL电平与CMOS电平是不兼容的,CMOS电路能驱动TTL电路,而TTL电路一般不能驱动CMOS电路,在TTL电路和CMOS电路混用的系统中,应特别注意。

第二节扩展中常用的器件介绍

一、锁存器

1、作用:

P0口分时复用时,一定要用锁存器将地址信号锁存起来,才能够达到地址、数据分离、分时复用的目的。

2、常用器件:

74LS373,74LS573,74LS374,8282,8283等

3、74LS373的引脚及控制

74LS373带输出三态门的8D锁存器。

引脚功能:

1D~8D—输入;1Q~8Q—输出;

G-数据锁存控制,D=1,输入=输出;由高变低(负跳变),锁存数据;D=0,锁存数据不变。

-输出允许端,

=0,三态门开;

=1,三态门关。

扩展多路时用来选择。

74LS373与74LS573只是引脚布置的不同。

74LS273的11脚G逻辑与以上相反。

正跳变输入数据并锁存,高、低电平锁存保持不变。

二、常用的总线驱动器

作用:

提高驱动能力,改善信号性态。

常用元件:

74LS244、74LS245

74LS244介绍:

74LS244是由8个三态门构成的单向驱动器。

如图:

8个三态门分为两组,由

和

进行控制。

、

-低电平导通,高电平输出为高阻态。

高阻态可以隔离信号,便于总线传输数据。

芯片有20个引脚,如图:

系统总线中地址总线和控制总线是单向的,因此驱动器可以选用单向的,如74LS244。

系统中的数据总线是双向的,其驱动器也要选用双向的,如74LS245。

74LS245也是三态的,有一个方向控制端DIR,DIR=1时输出(An→Bn),DIR=0时输入(An←Bn)。

第三节

存储器的扩展

存储器扩展分程序存储器扩展和数据存储器扩展。

由于程序存储器扩展在实际应用中已很少使用,故只做简单介绍。

一、扩展的基本原理

1、程序存储器扩展

右图为扩展时基本连接方法。

当

接高电平时,首先执行片内程序存储器中的程序,然后执行片外程序,片内外统一编址;若

接低电平,只执行片外的程序。

为片外程序存储器读选通信号。

必须和被扩展芯片的读选通输入信号线相连。

P0口输入8位数据和输出地址低8位,P2输出地址高8位。

ALE用于锁存低8位地址,在下降沿将低8位地址锁存。

可以看出,尽管89C51单片机有4个I/O口,共32条口线,但由于系统扩展的需要,真正能作为数据I/O使用的,就只剩下P1口和P3口的部分口线了。

特别需要强调的是,程序存储器不应再采用外扩的方案。

因为89系列单片机内有4~32KB的不同型号产品可供选择。

如果课题需要功能更强的MCU,则可选择ADμC8××、C8051F×××和MAX7651等SOC芯片。

2、数据存储器的扩展

数据存储器的扩展,基本原理与程序存储器相同,也是三总线对接,但数据存储器要对数据进行读和写,扩展外部设备时,也占用的是外部RAM的地址。

因此数据存储器的扩展要比程序存储器复杂。

扩展数据存储器空间地址,由P2口提供高8位地址,P0口分时提供低8位地址和用作8位双向数据总线。

片外数据存储器RAM的读/写由89C51的,RD(P3.7)和WR(P3.6)信号控制。

注意:

在数据存储器扩展时,P2口未用的引脚还可以做它用。

但注意相互影响,不要在写数据时影响未用的端口。

二、常用的存储器芯片介绍

1、EPROM

EPROM是采样电信号写入、紫外线擦除的存储器,专门用紫外线灯擦除,在日光下也可以擦除,长期暴露在室内光线下程序也消失。

因此要将擦除窗口保护起来。

常见的型号:

2732、2764、27128、27256等。

其中27后面的数字代表位容量,如2764为64k位容量,也就是8K字节的容量。

CMOS型加C,如27c128

2、EEPROM和FlashROM(可以存储不常修改的数据)

EEPROM是一种电擦除可编程只读存储器,其主要特点是能在计算机系统中进行在线修改,并能在断电的情况下保持修改的结果。

因而在智能化仪器仪表、控制装置等领域得到普遍采用。

存在的问题是写和擦除较慢。

常用的EEPROM芯片主要有Intel2816A、2864A等。

FlashROM是一种新型的存储器,也叫闪速存储。

型号有AT29010A,AT29020A等。

AT29010A的容量为64K字节。

3、随机存储器RAM

数据存储器一般采用RAM芯片,这种存储器在电源关断后,存储的数据将全部丢失。

(用在运算数据量大的情况)

常用的静态RAM(SRAM),在工业现场常使用SRAM。

常用的型号:

6116、6264、62128、62256等

型号:

6264,前两位数62,表示SRAM,

后两位64÷8=8k字节容量。

引脚功能:

以6264为例,介绍引脚功能。

I/O0-7:

双向数据线,三态输出;

A0~A12:

地址线;

:

片选信号,低电平有效;

CE2:

片选线,高电平有效;

:

读选通信号,输出使能

:

写选通信号,写入使能VCC、GND:

电源

NC:

未使用

还有串行连接的存储器等,在后面讲。

三、采用三总线方式扩展时地址的确定

1、地址确定的方法

对于扩展的芯片,要根据不同的芯片区别对待:

存储器:

芯片都有自己的地址引脚,如6264扩展8K,则芯片地址为A0-A13,低8位直接与P0口由锁存器输出的低8位相连,高位与P2对应位相连。

芯片都有片选,一般P2高位地址中未用完的端口,与片选相连,就确定了该芯片的地址。

其它元件:

如A/D转换等,片内需要的地址很少,一般用低8位就可以满足,地址确定主要取决于地址高8位分配的片选信号。

如用P0驱动8位LED显示,地址作为位码,数据作为段码,该位码的地址从高到低分别为80H、40H、20H、10H、08H、04H、02H、01H,256个地址中只用了8个。

如果还要扩展其它元件,就要用高8位的某一位控制373的输出允许OE,就合成一个完整的16位地址。

在扩展几个芯片时,按高8位中连接方法不同,分线选法和译码法。

2.线选法寻址

如果要扩展几个存储器,用P0和P2口的低几位地址线对每个芯片存储单元统一进行寻址,称为字选。

所需地址线数由每片的存储单元数决定,对于8K×8容量的芯片需要13根地址线A12-A0。

然后将余下的高位地址线分别接到存储芯片的片选端CE,称为线选。

线选法的不足是空间不连续,中间有一部分存储空间无法使用。

如下图所示:

扩展6264,每个只有8K,最多可以扩展8个6264,下面扩展3片6264为例,讲解如何扩展和确定地址(仅作为例子,如果扩展的容量大,可以直接选容量大的芯片,不但便宜,电路也简单,下面例子实际上可以直接用1片32K的62256)

6264

(1)的地址:

C000H-DFFFH,(P2.5=0)

6264

(2)的地址:

A000H-BFFFH,(P2.6=0)

6264(3)的地址:

6000H-7FFFH,(P2.7=0)

可以看出,高8位已经全部应用,只扩展了24K。

3.译码法寻址

译码法寻址就是利用译码器对系统的片外高位地址进行译码,以其译码输出作为存储器芯片的片选信号,将地址划分为连续的地址空间块,避免了地址的间断。

译码法仍用低位地址线对每片内的存储单元进行字选,而高位地址的某几位经过译码器译码后输出作为各芯片的片选信号。

常用的地址译码器是3/8译码器74LS138。

译码法又分为完全译码和部分译码两种。

如上例中用译码法,P2.5、P2.6、P2.7接3/8译码器,则最高3位的地址为000B-111B,就可以扩展8片6264。

注意:

将片外器件(如A/D转换等)扩展时,它的地址是RAM的一个单元地址,和RAM地址连续排列。

四、数据存储器6264的扩展举例

引脚连接说明:

1)数据线D0~n直接从锁存器前连接单片机的P0.0-P0.7;

2)地址线A0~A7从锁存器后连接,地址线A8~A12直接连单片机的P2.0~P2.4口。

3)片选线CE2接高电平,

连P2.7

4)读写线

(R/W)连接读写控制线

。

注意:

扩展时地址经常有形式上的不惟一性,如该电路中6264的8KB地址范围不唯一(由P2.5、P2.6、P2.7确定地址A15A14A13,只要保证P2.7为低电平,P2.5、P2.6如果在电路中无其它用途,则可置任意值),故地址的高三位是000,010,001,011都是正确的。

当向该片6000H单元写一个数据DATA时,可用如下指令:

MOVA,#DATA;要写入的数据

MOVDPTR,#6000H;要写入的地址

MOVX@DPTR,A

从7FFFH单元读一个数据时,可用如下指令:

MOVDPTR,#7FFFH

MOVXA,@DPTR

第四节I/O口的扩展

一、扩展的方法

当89C51应用系统需连接较多的输入/输出的外围设备(如打印机、键盘、显示器等),就得扩展。

2、用并行口扩展I/O口

1)用通用器件进行扩展

只要根据“输入三态,输出锁存”与总线相连的原则,选择74LS系列的TTL电路或CMOS电路即能组成简单的扩展I/O口。

例如采用8位三态缓冲器74LS244组成输入口,采用8D锁存器74LS273,74LS373,74LS377等组成输出口。

2)用串行口扩展I/O口

当MCS-51单片机串行口工作在方式0时,使用移位寄存器芯片可以扩展一个或多个8位并行I/O口。

这种方法不会占用片外RAM地址,而且可节省单片机的硬件开销。

缺点是操作速度较慢,扩展芯片越多,速度越慢。

常用的芯片有74LS165、74LS164等。

3)用专用芯片进行扩展

常用芯片如下:

型号

功能

8155/8156

256BRAM、可编程两个8位I/O口、可编程一个6位I/O口、14位定时器

8212

8位I/O口

8251A

可编程通信接口

8253

可编程3个16位定时器

8255A

可编程三个8位I/O口

8279

可编程键盘/显示器接口(64键)

8355

2K×8位ROM、两个通用8位I/O口

8755A

2K×8位EPROM、两个通用8位I/O口

二、通用器件的扩展

根据“输入三态,输出锁存”与总线相连的原则

下图中74LS244作为输入口、74LS273作为输出口,它们都可以通过P0口输入、输出数据。

注意:

由于P0口操作时,按指令相应的

和

有控制信号,在编程时就可以直接用MOVX给一个地址送数据,用其他端口时,就需要给端口送数据。

在74LS273中,

-清除线,低电平输出全为0;

-上升沿输入数据并锁存,高、低输出不变。

控制过程:

1、控制LED,

P2.0=0;

由1变0;“或非门”2输出正跳变,273将单片机输出的信息锁存。

输出低电平LED显示,因为用

锁存P0口的输出,所以LED的显示是由P0口输出的数据而不是地址,地址只要满足P2.0=0;其它地址位(含低8位)随意。

2、读按键输入

P2.0=0;

=0,“或”门1输出0电平,244的Q=D(直通),当

由低变高时,CPU读走数据。

当244的

、

为高电平时,Q端输出为高阻态。

注意:

确定地址时,要使P2.0(A8)为0。

其他未用地址可以随意。

三、用串行通信口扩展

1、用串行口扩展输出口

用串行口扩展输出口时,一般用移位寄存器,如74LS164芯片、4094芯片。

74LS164为串入并处的移位寄存器,下图为74LS164的引脚,各引脚功能如下:

Q0-Q7:

并出数据线;

DSA、DSB:

串行输入线,当其中有一个为低电平时输出为0;两个同时为高电平时输出QA为1。

可以同时接串行口的数据输出口RXD,也可以一个用于控制;

CP:

移位脉冲输入口,在脉冲上升沿移位;

:

清零,低电平有效。

例:

用89C51串行口外接164串入-并出移位寄存器扩展8位并行口;8位并行口的每位都接一个发光二极管,要求发光二极管从左到右以一定延迟轮流显示,并不断循环。

设发光二极管为共阴极接法,如图7-17所示。

解:

设数据串行发送采用中断方式,显示的延迟通过调用延迟程序DELAY来实现,延时程序的编写已经讲过。

程序清单:

ORG0000H

AJMP0030H

ORG0023H;串行口中断入口

AJMPSBR;转入串行口中断服务程序

ORG0030H;主程序起始地址

MOVSCON,#00H;串行口方式0初始化

MOVA,#80H;最左一位发光二极管先亮

CLRP1.0;传送数据时不显示

MOVSBUF,A;开始串行输出

LOOP:

SJMP$;等待中断,

SBR:

SETBP1.0;允许显示,数据传送完开始显示

ACALLDELAY;显示延迟一段时间

CLRTI;清发送中断标志

RRA;准备右边一位显示

CLRP1.0;关闭显示

MOVSBUF,A;再一次串行输出

RETI;中断返回

如果将上面指示灯看作七段数码管,一个164可以驱动1个七段数码管LED,N个LED需要N个164。

可以连续将要显示的数据发送完然后显示。

要用串行口扩展并行输入口,用芯片74LS165,也可以用4014芯片。

该部分内容自己看教材相关部分。

四、用专用芯片的扩展

由前面已经知道,用专用芯片,不但可以扩展并行端口,而且还可以扩展定时器/计数器,RAM等。

扩展时很大的特点是可以编程。

本节只用8155芯片介绍扩展方法。

1.8155的结构和技术性能

8155的结构框图。

在8155内部具有:

(1)256字节的静态RAM,存取时间为400ns。

(2)三个通用的输入/输出口。

(3)一个14位的可编程定时/计数器。

(4)地址锁存器及多路转换的地址和数据总线。

(5)单一+5V电源,40脚双列直插式封装。

2、8155的引脚功能

AD0-AD7:

三态地址/数据总线,带地址锁存;

ALE:

地址锁存信号,负跳变(高→低)锁存;

IO/

:

RAM与I/O口的选择线,低电平选择RAM操作,高电平选择I/O口;

:

片选信号,低电平有效;

:

读写控制线;

PA0-PA7:

端口A;

PB0-PB7:

端口B;

PC0-PC5:

端口C;

TIMERIN、TIMEROUT:

定时器/计数器输入输出。

3、8155的寄存器

和单片机相同,可编程器件都是由寄存器控制,编程也就是对寄存器编程。

(1)命令/状态寄存器C/S,该寄存器地址为×××××000B

该寄存器是两个寄存器公用一个地址,(写是命令,读是状态)

命令寄存器:

(见表)

注意:

复位时,命令寄存器被置为00H,端口PA、PB都为输入方式。

状态寄存器:

状态寄存器用于查询当前状态。

读状态寄存器,TIMER自动清零。

(2)PA寄存器,地址:

×××××001B

为PA口寄存器。

(3)PB寄存器,地址:

×××××010B

为PB口寄存器。

(4)定时器低8位寄存器,地址:

×××××100B

定时器高8位寄存器,地址:

×××××101B

(5)PC寄存器地址:

×××××011B

为PC口寄存器,可以由命令寄存器中的PC1、PC2设置PC口为输入寄存器、输出寄存器,也可以PC的6个端口设为PA、PB口的控制线。

第五节中断扩展

1、为什么要扩展中断。

AT89C52单片机有两个外部中断请求输入端(即外部中断0、外部中断1)。

在实际应用中,往往有三个或三个以上的外部事件需要用中断进行处理,这就需要扩展外部中断源。

2、利用查询加中断的方式进行扩展

利用AT89C52的两个外部中断线,每一个中断线可以通过“与”的关系连接多个外部中断源,同时利用AT89C52的I/O端口作为各中断源的识别。

例:

用单片机监测X1,X2,X3三个外部设备在运行过程中是否有故障。

不管哪

一个设备一旦出现故障,必须马上处理,所以采用中断系统来监测这三个外部设备。

当系统无故障时,3个故障源输人端X1~X3全为低电平,对应的3个显示灯全灭;当某个设备出现故障时,其对应的输入端由低电平变为高电平,从而引起AT89C52单片机中断,中断服务程序的任务是判定故障,并点亮对应的发光二极管。

其中,发光二极管LEDl~LED3对应3个输入端X1~X3。

实现上述功能的电路如图所示。

3个故障源X1~X3通过“或非门”与AT89C52单片机的外部中断0输入端相连,同时,X1~X3与PO口的P1.0-P1.2引脚相接,3个发光二极管LEDl~LED3分别与P0口的P1.3~P1.5相接。

主程序如下:

ORG0000H;;主程序的入口地址

AJMPMAIN;跳转到主程序的开始处,

ORG0003H;外部中断0的中断程序入口地址

AJMPSERVE;跳转到中断服务程序处

MAIN:

ORLP1,#OFFH;灯全灭,准备读入

SETBIT0;选择边沿触发方式

SETBEX0;允许INT0中断

SETBEA;CPU开中断

AJMP$;等待中断

中断服务子程序如下:

SERVE:

PUSHPSW;保护规场

PUSHACC

JNBP1.0,L1;若x1无故障,跳到L1

CLRP1.3;点亮LED1

L1:

JNBP1.1,L2;若x2无故障,跳到L2

CLRP1.4;点亮LED2

L2:

JNBP1.2,L3;若x3无故障,跳到L3

CLRP1.5;点亮LED3

L3:

POPACC;恢复现场

POPPSW

RETI

第四节串行扩展总线接口技术

一、概述

1、并行口扩展:

线路复杂,占用资源多,使单片机本来就不多的资源显得很紧张,对于智能仪器,特别是便携式仪器,功耗低,体积小是一个重要的指标。

2、串行总线扩展:

占用MCU的I/O口线少,系统简单,体积小,编程也方便。

。

3、实现方法:

1)、串行口扩展I/O口线;

2)、SPI串行总线扩展;

3)、I2C总线扩展;

4)、单总线扩展。

5)、其它如USB总线等。

扩展应尽量采用串行扩展方案。

通过SPI或I2C总线扩展E2PROM、A/D、D/A、显示器、看门狗、时钟等芯片。

有些单片机已经带有该接口。

4、扩展时的共性问题

1)系统如何找到该器件;

2)如何对扩展的芯片进行控制;

3)通信协议是什么(特别是时序图);

4)怎样进行读或写。

二、I2C总线扩展

一)概述

1、什么是I2C总线

I2C(Inter-IntegratedCircuit)总线是一种由PHILIPS公司开发的一种简单、双向二进制同步串行总线,它只需要两根线即可在连接于总线上的器件之间传送信息。

I2C总线产生于在80年代,最初为音频和视频设备开发。

2、I2C总线的几个基本概念

1)所有进入I2C总线系统中的设备都带有I2C总线接口,只需将I2C总线上所有节点的串行数据线SDA和时钟线SCL分别与总线的SDA和SCL相连即可。

2)当执行数据传送时,启动数据发送并产生时钟信号的器件称为主器件;被寻址的任何器件都可看作从器件;发送数据到总线上的器件称为发送器;从总线上接收数据的器件称为接收器。

3)I2C总线是多主机总线,可以有两个或更多的能够控制总线的器件与总线连接;同时I2C总线还具有仲裁功能,当一个以上的主器件同时试图控制总线时,只允许一个有效,从而保证数据不被破坏。

4)I2C总线的寻址采用纯软件的寻址方法,无需片选线的连接,这样就简少了总线数量。

3、优点

①总线只有两根线,即串行时钟线SCL和串行数据线SDA。

②同步时钟允许器件以不同的波特率进行通信;总线的长度可高达7m,在标准I2C模式下数据传送率可达100kB/s,高速模式下可达400kB/s。

③它是一个真正的多主总线,带有竞争监测和仲裁电路,多个主机任意发送而不破坏总线上的数据。

下图中单片机有2个,单片机必须有I2C总线接口。

89C51无该接口,只能用于单主扩展。

④支持带电插拔,并有众多的外围接口芯片;并且能够以10Kb/s的最大传输速率支持40个组件。

4、I2C器件类型及用途

常用的12C总线外围通用器件有:

SRAM,EEPROM,ADC/DAC,I/O口,实时时钟芯片RTC等。

外围设备模块有LED驱动控制器构成的LED显示器,各种LCD驱动控制器